### Mu2e CD3c Review WBS 7.7 FEE & Power

S. Miscetti, Mu2e Calorimeter L2 manager representing G. Corradi, Mu2e Calorimeter Frontend Electronics and Power L3 Manager

18 April 2016

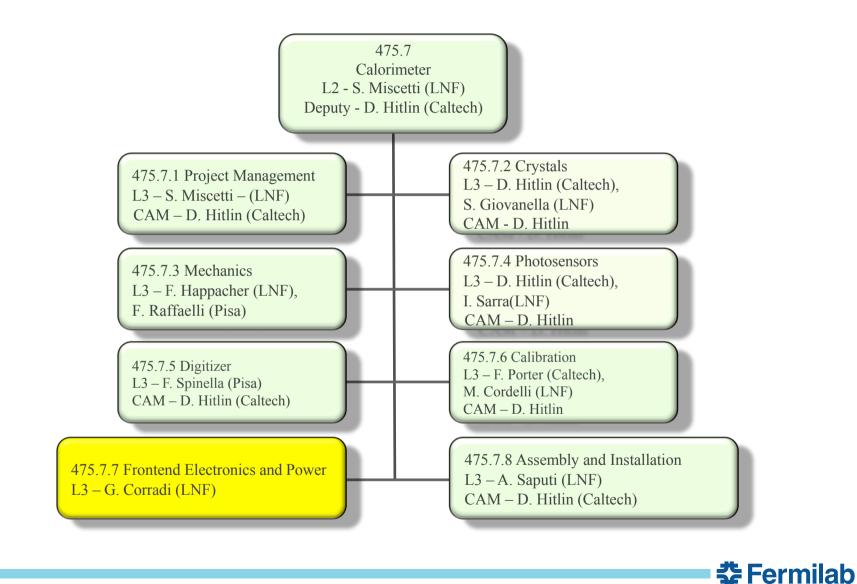

# **Mu2e Calorimeter Organization**

### Scope

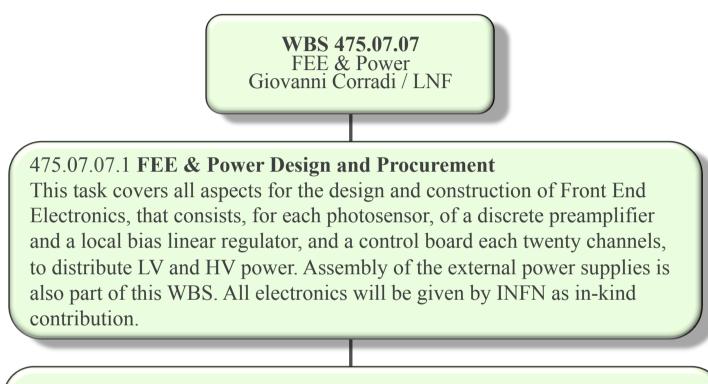

#### 475.07.07.2 FEE & Power Production

This task covers all the work for:

- The Front End chips for amplification and bias regulation;

- The LV and HV distribution boards;

- The LV and HV external power supplies.

Delivery of the FEE and power supplies from INFN.

**7** Fermilab

### **Calorimeter Electronics Scheme**

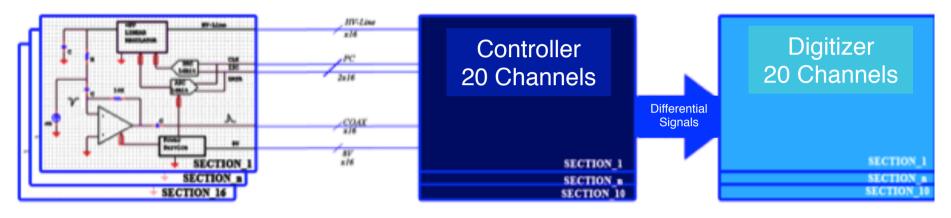

Overview of the calorimeter readout electronics: each disk (~ 680 crystals per disk) is subdivided into 34 groups of 20 crystals.

- Groups of 20 left (right) Amp-HV chips, controlled by a \_ dedicated mezzanine board that distributes the LV and the HV reference value, while setting and reading back the locally regulated voltage

- Groups of 20 amplified signals are sent to a digitizer module where they are sampled and processed before being optically transferred to the DAQ system.

### Mu<sub>2</sub>e

### **Calorimeter FEE Layout**

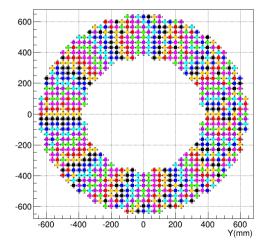

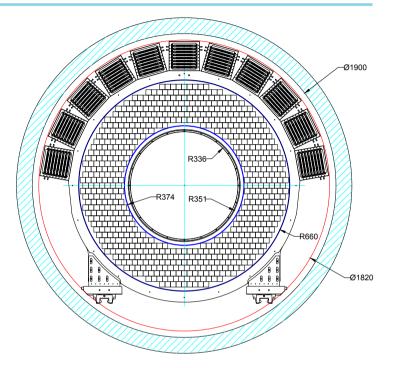

- There are therefore 11 crates per disk, hosting 6/7 sets of AMP-HV and WFD boards;

- The crates are placed in the outermost region of each disk;

- The crates are designed to provide heat dissipation for the electronics boards (see presentation on cooling).

Crystal 34.3 mm x 34.3 mm (including wrapping 0,15 mm) (34 mm + 0.15 mm + 0.15 mm) x (34 mm + 0,15 mm + 0.15 mm) 674 crystals

### Mu2e

### **Requirements I – Calorimeter FEE**

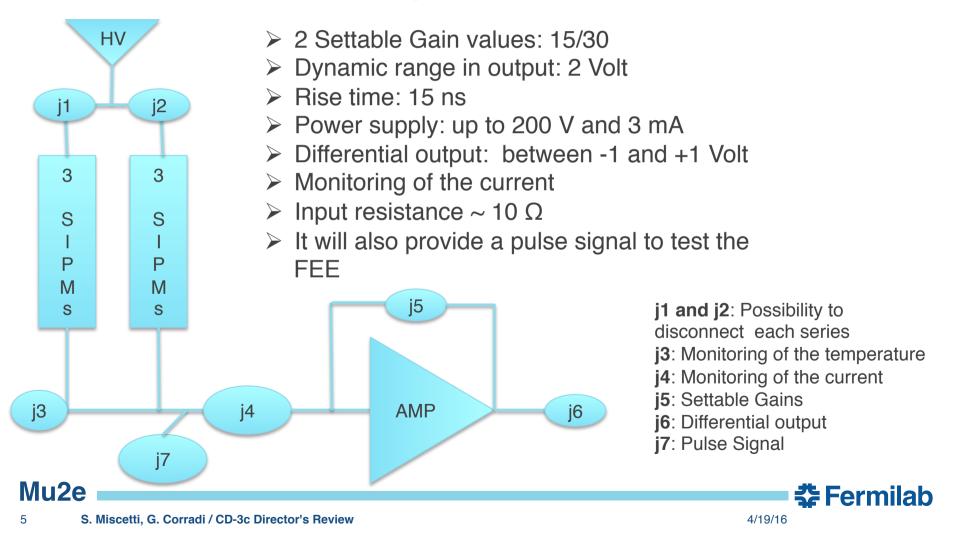

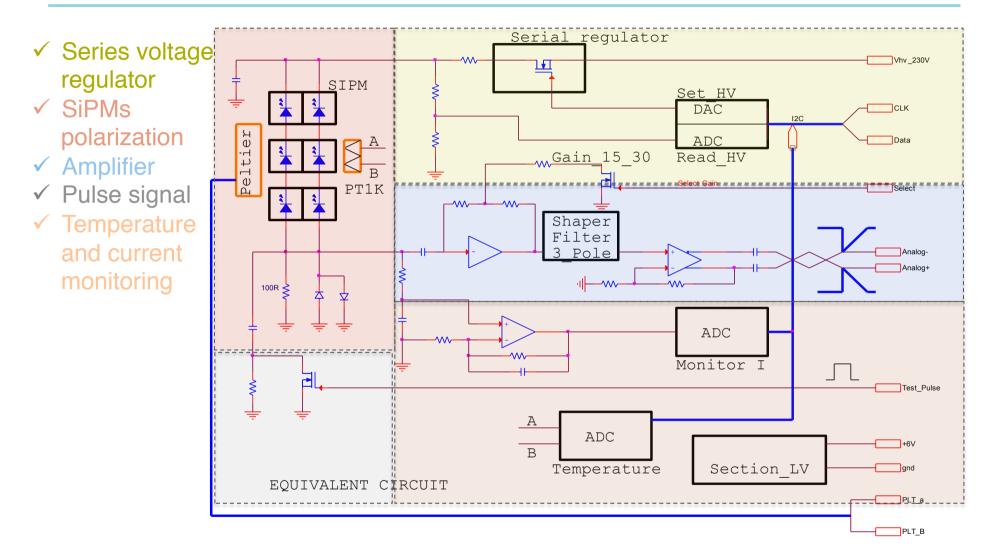

Provide both the amplification stage and a local linear regulation for the Silicon photosensor bias voltage

### **Architecture of Front-end**

Mu2e

**‡**Fermilab

# **Transimpedance Preamplifier**

- Trans-impedance

- Dynamic differential

- Bandwidth

- Rise time

- Polarity

- Output impedance

- Coupling output end source

- Filter Shaper

- Noise, with source capacity 1pf

- Power dissipation

- Power supply

Mu<sub>2</sub>e

Input Protector over-Voltage

750 $\Omega$  to 1.5K $\Omega$ **2**V 35 Mhz 15ns Differential 100 O AC 3-pole must be evaluated 20mW 6V 10mJ

#### 7 S. Miscetti, G. Corradi / CD-3c Director's Review

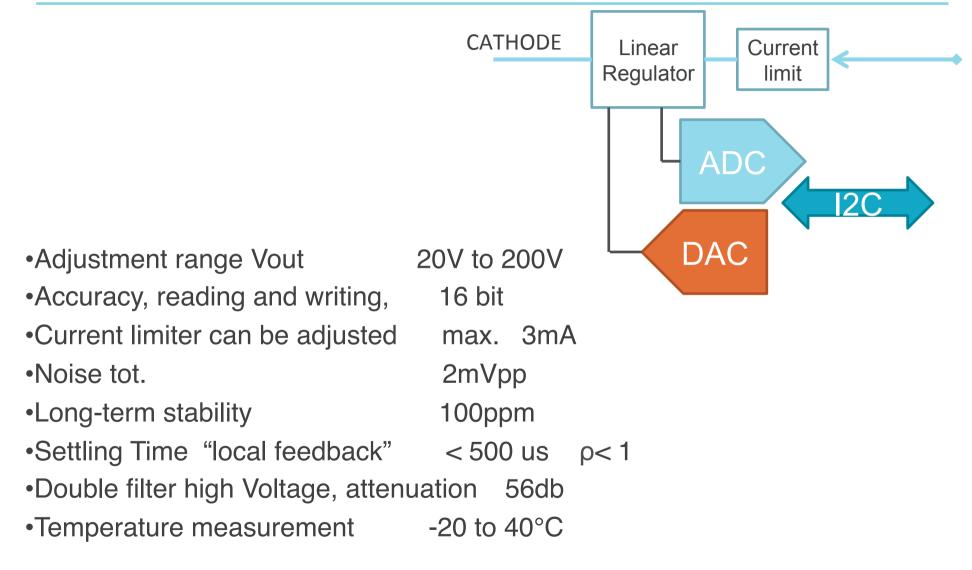

# Linear Regulator shunt architecture.

Fermilab

### **AMP-HV Prototyping**

Since 2014 2 different production of preamplifiers have been carried out, together with their control boards in ARM technology, following the long story of our technology choice :

- $\rightarrow$  Amp-HV for LYSO (Gain 300, Vbias ~ 500 V)

- $\rightarrow$  Amp-HV for SL APD (Gain 300, Vbias ~ 2 kV)

A lot of experience gained with these prototyping phase

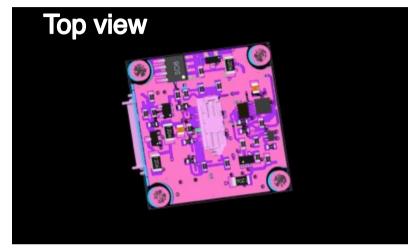

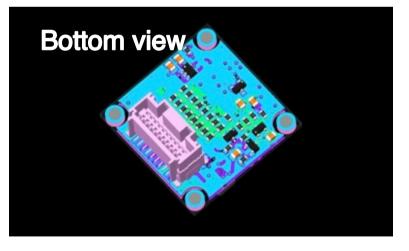

- ✓ Prototypes have been designed and produced also for the MPPC option for the used SPL/MicroFilm arrays of 16 3x3 mm<sup>2</sup> SIPMs.

- ✓ Test beam carried out successfully in April 2015

$\rightarrow$  Amp-HV and analog adder for 16 channels MPPC at 60 V bias used.

➢ The design of the new electronics for the final selected SIPM packaging is starting from this last experience.

**7** Fermilab

### **Therma-bridge Resistor**

# Power to dissipate 150mW Therma-bridge Area of mechanical anchorage MPPC Output connector Mu<sub>2</sub>e **‡** Fermilab 10 S. Miscetti, G. Corradi / CD-3c Director's Review 4/19/16

# **Cooling problem for Amp-HV**

- We solve the problem of cooling in Vacuum by transferring the heat from the Amp-HV to the mechanical support, through a therma-Bridge

- An example is shown in the side view.

- The heat transfer must take place in isolation from common ground.

### Therma-Bridge<sup>™</sup> Electrically Isolated A/N Thermal Management Device

The ims Aluminum Nitride (A/N) **Therma-Bridge**<sup>TM</sup> is a simple, cost effective device which aids in thermal management. Bridges are available in standard sizes and thicknesses. Custom sizes are also available on request. The **Therma-Bridge**<sup>TM</sup> is designed to transport heat from one location to another. Simply attach one terminal to the heat source, and the other terminal to a thermal plane or heat sink. Popular application configurations are shown on the reverse side. The **Therma-Bridge**<sup>TM</sup> has the following features:

- · Electrically Isolated A&N substrate material

- Multiple sizes and thicknesses

- RoHS PtAg or Solder coated PtAg terminals for easy attachment

#### **Terminal style:**

#### **Terminal materials:**

PtAg (platinum silver) for epoxy or solder attachment

-C Solder coated PtAg for solder attachment

Mu<sub>2</sub>e

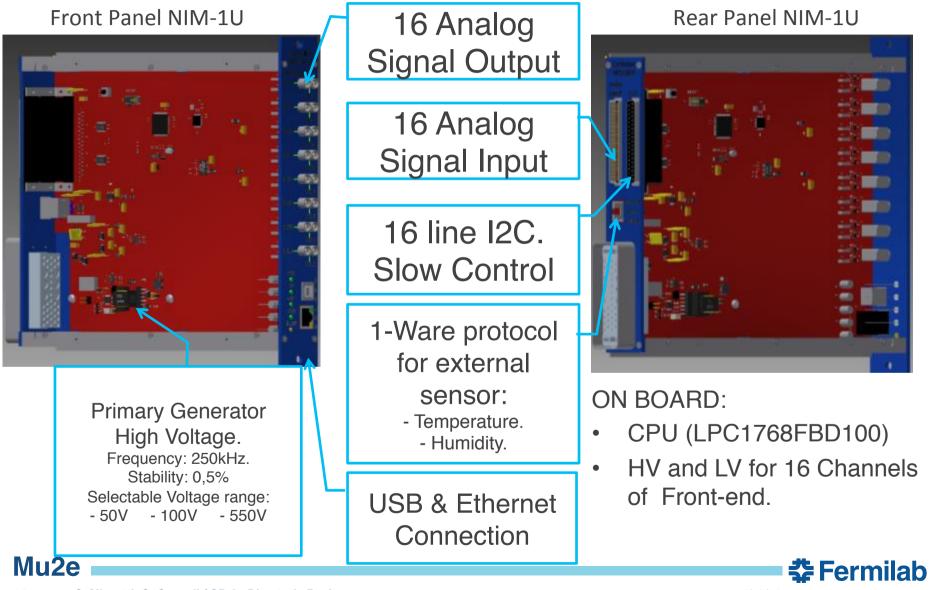

### **Controller- ARM used for Test Beam**

# **MPPC** amplifier

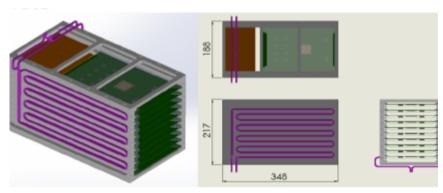

The Amp-HV is a multi-layer double-sided discrete component board that carries out the two tasks of amplifying the signal and providing a locally regulated bias voltage, thus significantly reducing the noise loop-area.

### Adder Amplifier

- Gain 4

- BW 200 MHz

- Rate up to 100 kHz

### HV regulator

- regulation steps 10 mV up to 90 V

- Stability better than 10 mV

### Mu<sub>2</sub>e

# **Design Maturity**

| Calorimeter<br>Subsystem                     | Design<br>Completion | Remaining Work/Risks                                                                                                                                                                                                        |

|----------------------------------------------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Crystals                                     | 90%                  | Specification of CsI slow component - Low risk.                                                                                                                                                                             |

| Photosensors                                 | 85%                  | SiPM packaging. Have one packaged SiPM from<br>Hamamatsu but want to qualify other vendors -<br>Low risk.                                                                                                                   |

| Mechanical<br>Infrastructure                 | 65%                  | Finalize cooling design. Optimizing tradeoffs between noise, radiation damage and operating temperature. x2 headroom - Low Risk                                                                                             |

| Front End Electronics<br>And Digitizer (WFD) | 60%                  | <ul> <li>New pre-amp design for CsI/SiPM - Low Risk.</li> <li>WFD board design with 20 channels.<br/>Moderate risk that we may have to back off to<br/>18 channel boards. Adds a small amount of<br/>complexity.</li> </ul> |

| Calibration                                  | 90%                  | Integration of source pipes. Finalize laser optics.<br>– Low Risk                                                                                                                                                           |

| Overall Design                               | 80%                  |                                                                                                                                                                                                                             |

**‡**Fermilab

# Quality

- FEE' plans included in Mu2e Quality Planning Document

- Available on web page (docdb 6005)

| Deliverable | QA or QC Step?                        | QA or QC Process<br>Documentation (DocDB #) | Inspection or Acceptance<br>Criteria/Plan                                                                                                                                             | Verification                                                                                                                                                                                                                                       |

|-------------|---------------------------------------|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FEE         | QA: Calibration of Voltage<br>scale   | in progress                                 | The regulation voltage part of<br>each FEE chip will be tested on<br>a bench in a semi-automatic<br>manner by varying the setting in<br>steps of 100 mV around the<br>operation bias. | Each step of setting will be controlled by means of an external voltmeter with digital readout                                                                                                                                                     |

| FEE         | QA: Gain                              | in progress                                 | For the preamplification part,<br>both the signal shape and the<br>amplification gain will be tested<br>when sending in input a narrow<br>analog signal.                              | The linearity in response will be determined by sending 20<br>different values of input signal in mV to test both the<br>amplification value and its linearity. Dinamic range up to 2 V,<br>Gain = 10. We will use input signals from 10 to 190 mV |

| FEE         | QA: Calibration of mezzanine<br>board | in progress                                 | The mezzanine boards will be<br>tested both for evaluating the<br>ADC/DAC part to set and read<br>the voltages.                                                                       | A reference WFD board will be used to test the connection<br>between the mezzanine and the WFD and allows to<br>communicate via optical fibers to a control desktop. A digital<br>voltmeter will be used to measure the output.                    |

Mu<sub>2</sub>e

### Interfaces

|                     |                          | Internal Interfaces                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                     |  |  |

|---------------------|--------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|--|--|

| Item                | Interface                | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Owners                              |  |  |

| 107.04.1.1          | SIPM/FEE/Laser<br>system | The disk consists of a self- standing structure built<br>piling-up the single crystal units in a way which<br>allows insertion and extraction of photo-sensors if<br>repair is needed. The SIPMs are mounted in the<br>SIPM/FEE holders attached to the rear support disk.<br>The SIPM are closely connected to the related FEE<br>electronics. The connectors for inserting optical<br>fibers will be placed in the rear face in a dedicated<br>spot in the SIPM holder. Interference between<br>calibration services and FEE cabling have to be<br>considered in the cabling layout at CAD level and<br>tested in a dedicated full size mockup and in a larger<br>size prototype (Module- 0). | 475.07.04<br>475.07.05<br>475.07.06 |  |  |

| External Interfaces |                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                     |  |  |

| 107.07.2.1          | AC Power<br>Distribution | AC power is required for the power supplies of the calorimeter, for and the general distribution will be supplied by WBS475.03                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 475.07.07<br>475.03                 |  |  |

Interfaces are understood and under control

**‡** Fermilab

### **Milestones**

- Short term:

- $\rightarrow$  Pre-production for the module-0 in June 2016

- $\rightarrow$  QA of pre-production July 2016

- $\rightarrow$  Module 0 in fall 2016

• Long Term:

PO issued for production FEE and Power April 2017

QC of all FEE and Power complete August 2018

# Conclusions

- The front-end system can handle the SiPM photosensor, in a Voltage range regulation between the 20-230 Volt.

- In the preamplifier, the gain can be adjusted at two different values in case of needs for the innermost region after irradiation.

- The connection cables, between preamp and controller card, should have lengths smaller than two meters. This is in agreement with the cabling layout we are designing for the final calorimeter geometry.

- We are now developing another version of this system, that will be adapted to the new SiPM packaging layout with readout in series:

- $\rightarrow$  Conceptual design ready;

- → Technical design will be released end of May 2016;

- → 120 prototypes will be assembled for test beam of the module 0, end of June 2016.

### **Controller\_ARM MPPC**

Front view

4/19/16

**‡** Fermilab

### **Control Panel**

APD1768 web server Decision of the served by an ARM Cortex-M3 processor. Click on the links below to see the status of the APD card or about the web server and the TCPAP stack. This software is developed in the frame of <u>RITMARE</u> and the <u>MuCe</u> projects For additional information about APD1768, please send mail to.

# [ Network | System | Configure | Data | Statistics ]

Copyright © 2013-17

### Control panel via network

- $\rightarrow$  Control the Front-End cards.

- → Setting and reading the output voltage.

- →Measurement of Temperature and supply voltages.

#### Individual channel HV control

This page allows to control individual channels of the APD sensor working voltage and monitor applied HV in numeric and graphic form. Refresh counter: 1244

|         | Global H | tv setting 🖻 🌔 | •      | Auto refresh 🗷 |          |  |

|---------|----------|----------------|--------|----------------|----------|--|

| Channel |          | HV             | Status | Volt           | Bargraph |  |

| > Ch01  |          | 385.0          | Θ      | 384.9V         |          |  |

| Ch02    |          | 382.9          |        | 382.8V         |          |  |

| > Ch03  |          | 0.0            | Θ      | ov             |          |  |

| > Ch04  |          | 0.0            | Θ      | 0V             |          |  |

| > Ch05  |          | 0.0            | Θ      | ov             |          |  |

| Ch06    |          | 0.0            | Θ      | ov             |          |  |

| Ch07    |          | 0.0            | Θ      | ov             |          |  |

| Ch08    |          | 0.0            | Θ      | 0V             |          |  |

| Ch09    |          | 0.0            | Θ      | OV             |          |  |

| Ch10    |          | 0.0            | Θ      | OV             |          |  |

| > Ch11  |          | 0.0            | Θ      | 0V             |          |  |

| > Ch01  |          | 0.0            | Θ      | 0V             |          |  |

| Ch13    |          | 0.0            | Θ      | ov             |          |  |

| Ch14    |          | 0.0            | Θ      | ov             |          |  |

| Ch15    |          | 0.0            | Θ      | ov             |          |  |

| Ch16    |          | 0.0            | Θ      | 0V             |          |  |

| Channel | Enable   | HV             | Status | Volt           | Bargraph |  |

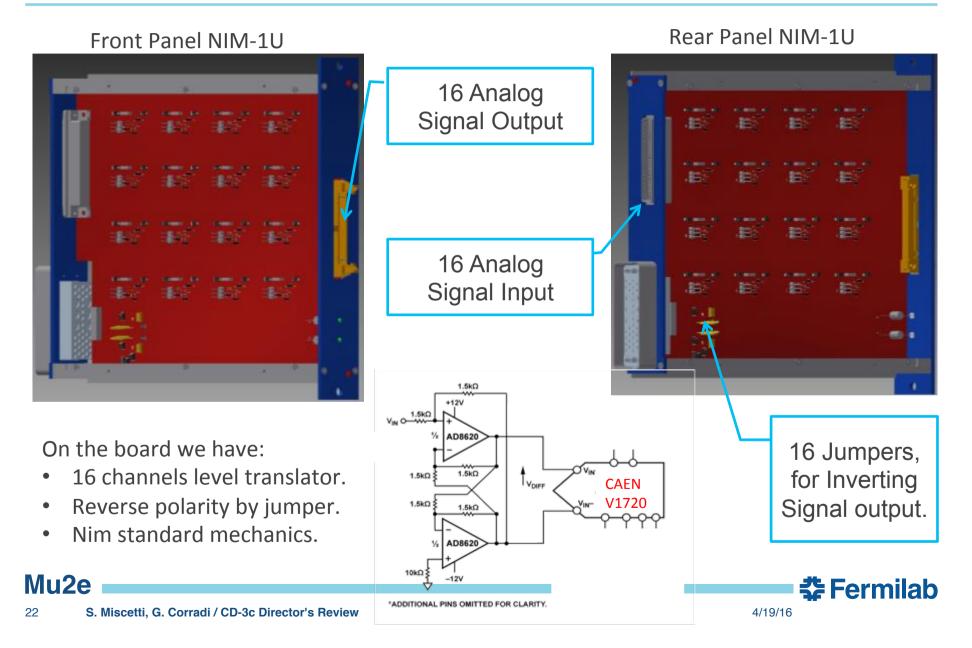

### Card shifter coax to differential.