# Monolithic Pixel Sensors in Deep-Submicron SOI Technology

Pixel 2008 International Workshop

FNAL, September 23-26, 2008

**Devis Contarato**

Lawrence Berkeley National Laboratory

M. Battaglia, L. Glesener (UC Berkeley & LBNL)

D. Bisello, P. Giubilato, S. Mattiazzo (LBNL & INFN Padova)

P. Denes, C. Q. Vu (LBNL)

### **Outline**

- Introduction on SOI technology: from commercial applications to radiation sensors

- OKI fully-depleted SOI-CMOS fabrication process

- Prototype chips design and testing at LBNL

- Experimental results: beam test and radiation tests

- Summary and Outlook

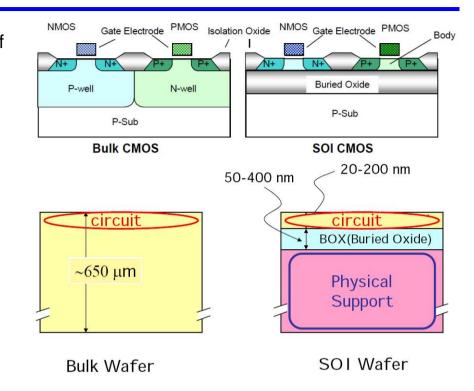

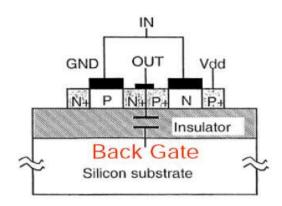

# Silicon-On-Insulator (SOI) technology

- CMOS electronics implanted on a thin silicon layer on top of a buried oxide (BOX): ensures full dielectric isolation, small active volume and low-junction capacitance

- Latch-up and soft-error immunity, low threshold, low noise: technology widely employed in high-speed and low power applications, e.g. microprocessors and portable electronics

- Radiation sensors can be built by using a high-resistivity substrate and providing a technology to interconnect the substrate through the BOX

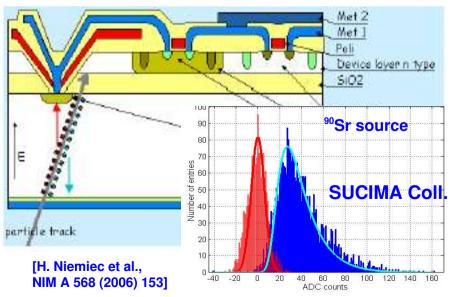

- $^{\bullet}$  First attempt from SUCIMA collaboration in a 3  $\mu m$  process from IET, Poland, though not compatible with standard CMOS processes

- Depletion of substrate via p-n junction implanted through BOX and fully-integrated readout logic on top

- → SOI monolithic pixel sensor

## **OKI Fully-Depleted SOI process**

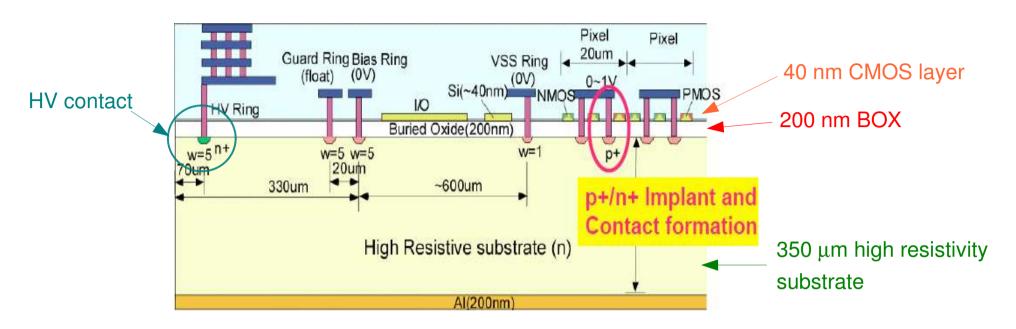

- Novel 0.15 μm Fully-Depleted (FD) SOI process from OKI Ltd., Japan

- 350  $\mu$ m thick substrate, high-resistivity (700  $\Omega$ ·cm): can be contacted through the 200 nm buried oxide for pixel implant formation and high voltage (HV) contact for substrate reverse bias

- 40 nm thin CMOS layer, fully depleted at operational voltages (low threshold, low power)

- Back-plane plated with 200 nm Al layer to allow biasing from the back

- Functionality demonstrated by prototype chip from KEK in '06; two subsequent runs in 2007 and 2008 involving submission from Japan and US institutes (LBNL, FNAL, U Hawaii)

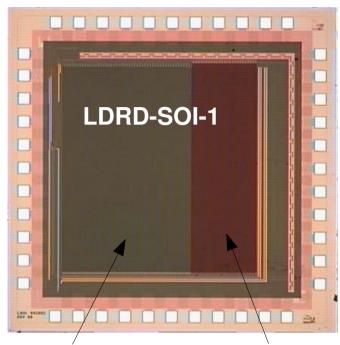

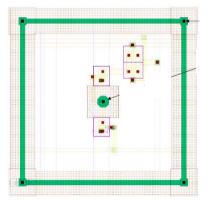

## LBNL SOI prototype in 0.15 µm process

**Analog pixels**

Digital pixels

#### LDRD-SOI-1 (2007)

- OKI 0.15 μm FD-SOI process

- Pilot run, not optimized in terms of leakage current

- 350 μm thick substrate (n-type, 6×10<sup>12</sup> cm<sup>-3</sup>), 200 nm BOX, 40 nm thin CMOS layer

- 160x150 pixels, 10x10 μm<sup>2</sup> pixels

- Floating p-type guard-ring around each pixel

- Choice of substrate contact and pixel layout justified by TCAD simulations

- 2 analog parts: 1.8 V and 1.0 V, simple 3T pixel architecture

- 1 digital part: in-pixel comparator and latch, no amplifier; adjustable threshold; 15 transistors/pixel

- Readout at 6.25 MHz, 1.3 ms integration time (analog pixels)

- Adjustable integration time for digital pixels

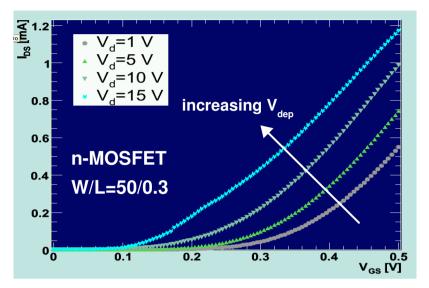

## The back-gating effect

- The high field in the depleted substrate causes backgating of the CMOS electronics on top of the BOX

- Test of single transistors vs depletion voltage: shift in the threshold voltage with increasing substrate voltage

- Significant effect observed in single transistor tests: expect analog section functional for V<sub>den</sub> < 20 V

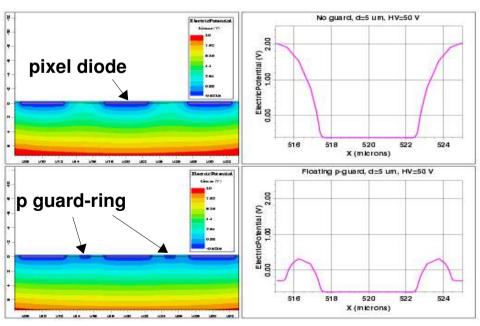

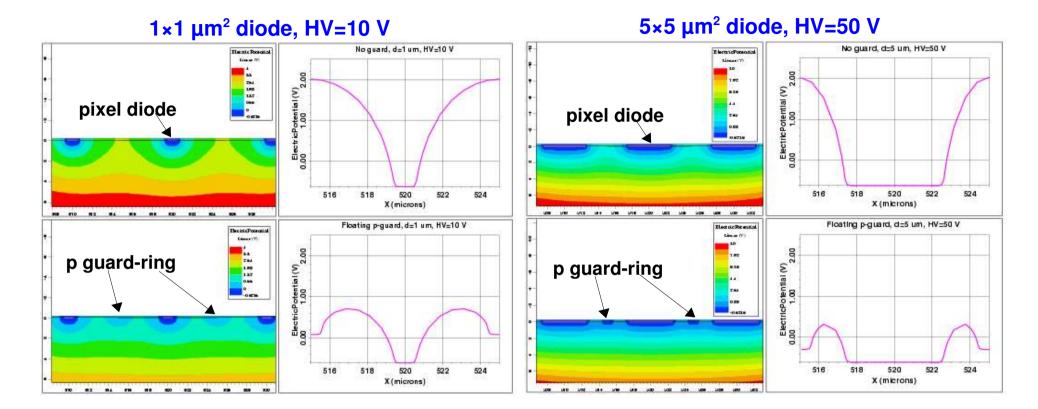

- Synopsys TCAD simulations: pixel surface potential for different diode sizes and depletion voltages

- Floating p-guard structure around each pixel to keep potential low and limit back-gate effects on MOSFETs

**Devis Contarato**

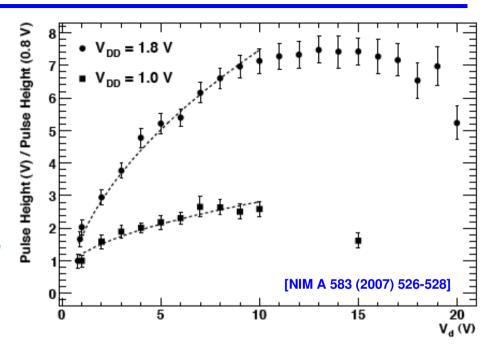

## **Tests with infrared laser**

- Depletion region thickness vs substrate voltage measured with focused 1060 nm laser

- Expect signal proportional to depletion region thickness D and:

$D\!\propto\!\sqrt{V}_{dep}$

• Good agreement with expectation for V<sub>dep</sub>≤10V (D~45 μm), back-gating effects becoming significant for larger voltages

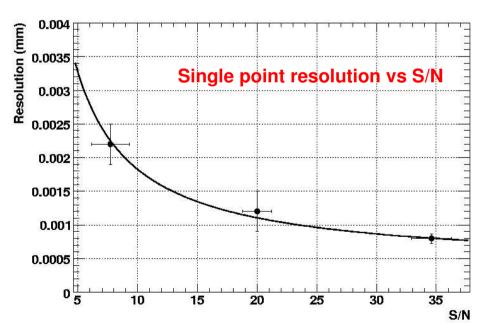

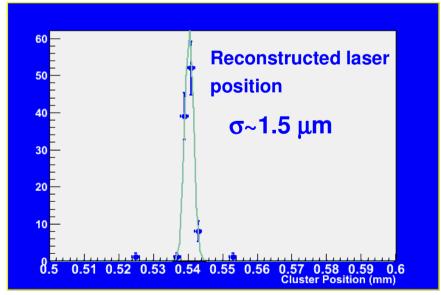

- $^{ullet}$  Sensor spatial resolution studied by means of pixel scans performed on the analog pixels with 1060 nm laser focused to a 5  $\mu m$  spot for different S/N values

- With pixels of 10  $\mu$ m pitch, 1  $\mu$ m single point resolution is achievable for a S/N ratio of 20

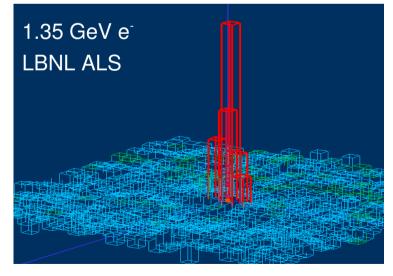

## **Electron beam-test: analog sectors**

- 1.35 GeV e<sup>-</sup> beam extracted from the injection booster at the LBNL Advanced Light Source

- First successful high momentum particle beam test on SOI monolithic pixel sensors

- As a function of the increasing  $V_{dep}$ : cluster pulse height increases and cluster multiplicity decreases, up to  $V_{dep} \sim 10 \text{ V}$ , consistent with lab tests and backgating effects becoming important at  $V_{dep} = 10 \text{ V}$

| NP of Clusters<br>0 1400 | 1     | V           | 8 V anal<br><sub>ep</sub> =10 V | og pixel              | S               |

|--------------------------|-------|-------------|---------------------------------|-----------------------|-----------------|

| 1000                     |       |             |                                 |                       |                 |

| 600                      | , Age |             |                                 |                       |                 |

| 400<br>200               | ¥     | Con Control | elen a                          |                       |                 |

| 00                       | 500   | 1000        | 1500                            | 2000<br>leight (ADC C | 2500<br>counts) |

|                       | 1.8 V Analog Pixels           |                                |                            |                         |  |  |  |

|-----------------------|-------------------------------|--------------------------------|----------------------------|-------------------------|--|--|--|

| V <sub>d</sub><br>(V) | Clusters / Spill<br>(Beam on) | Clusters / Spill<br>(Beam off) | Signal MPV<br>(ADC Counts) | Average<br>Signal/Noise |  |  |  |

| 1                     | 9.7                           | 0.05                           | 132                        | 8.9                     |  |  |  |

| 5                     | 14.0                          | 0.12                           | 242                        | 14.9                    |  |  |  |

| 10                    | 7.8                           | 0.20                           | 316                        | 15.0                    |  |  |  |

| 15                    | 3.9                           | 0.01                           | 301                        | 13.6                    |  |  |  |

[NIM A 583 (2007) 526-528]

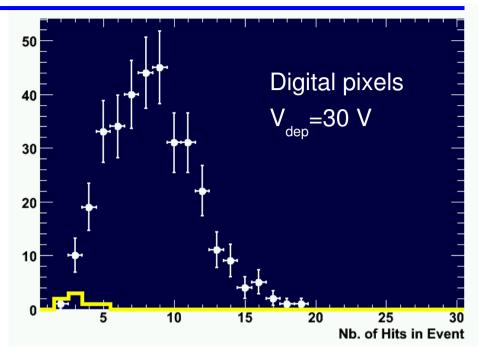

## Electron beam-test: digital pixels

- Signal above threshold only at high substrate voltages:

- analog threshold affected by back-gating

- $\rightarrow$  larger depletion  $\rightarrow$  increased charge signal

- these effects seem to combine for best detection capabilities at V<sub>den</sub>=25 V

- ullet Cluster multiplicity decreases with increasing  $V_{_{\text{dep}}}$

- Control data sets without beam to estimate fake hits

- Hit multiplicity corrected for the relative change of beam intensity, as determined by single MIMOSA-5 (IPHC, Strasbourg) reference plane 2 cm upstream from detector

| V <sub>d</sub> (V) | Clusters/Evt<br>w/ beam | Clusters/Evt<br>w/o beam | <nb pixels=""></nb> |

|--------------------|-------------------------|--------------------------|---------------------|

| 20                 | 3.7                     | 0.04                     | 1.78                |

| 25                 | 5.3                     | 0.04                     | 1.32                |

| 30                 | 4.7                     | 0.04                     | 1.26                |

| 35                 | 4.2                     | 0.01                     | 1.14                |

## **Irradiation tests**

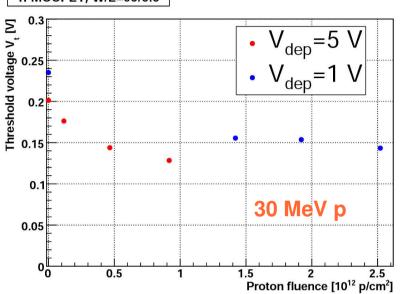

#### n-MOSFET, W/L=50/0.3

- Irradiations performed at LBNL 88" Cyclotron BASE Facility

- 30 MeV protons up to an integrated fluence of 2.5 x 10<sup>12</sup> p/cm<sup>2</sup> (~600 kRad)

- Shift in transistor threshold voltages throughout irradiation

- Charge trapping in BOX increases back-gating; contribution from charge trapped in thin MOSFET oxide negligible

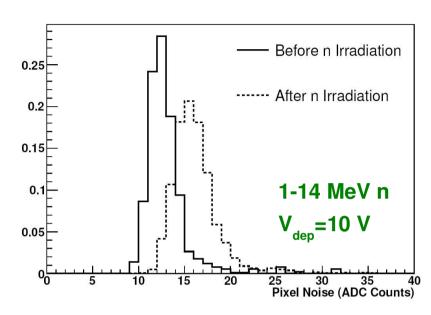

- 1-14 MeV neutrons up to 1.2 x 10<sup>13</sup> n/cm<sup>2</sup>

- No change in transistor characteristics

- Noise increases after irradiation (25% to 50% for  $V_{dep} = 5 \text{ V}$  to  $V_{dep} = 20 \text{ V}$ ), correlated with increased leakage current

- Pre-irradiation noise recovered by cooling to below +5°C

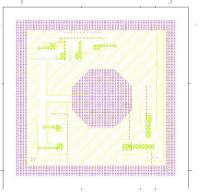

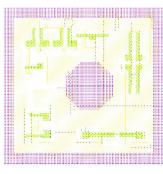

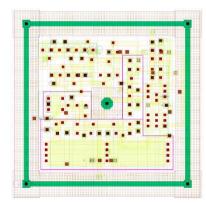

## New prototype in 0.20 μm process

**Analog pixels**

**Digital pixels**

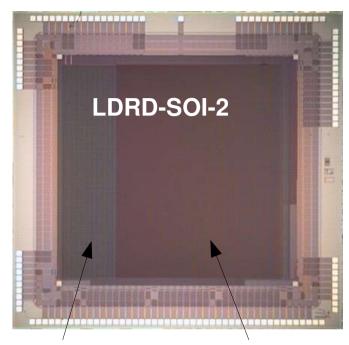

#### LDRD-SOI-2 (2008)

- $^{\bullet}$  OKI 0.20  $\mu m$  FD-SOI process; production process, optimized for low leakage current

- larger size prototype (5x5 mm²), 20x20 μm² pixels, 1.8 V operational voltage

- 40x172 analog pixels: simple 3T architecture for technology evaluation

- 128x172 digital pixels; evolution of chip-1 digital pixel: 2 capacitors for in-pixel CDS, clocked comparator with current threshold; 40 transistors/pixel

- 50 MHz readout, multiple (25) parallel outputs for improved frame rate

- Just received back from fabrication, first tests under way. Both analog and digital pixels functional.

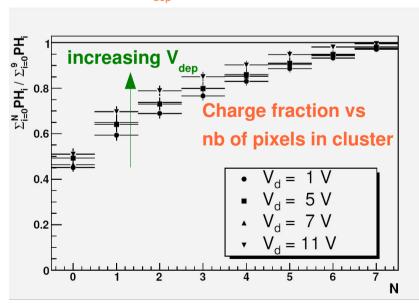

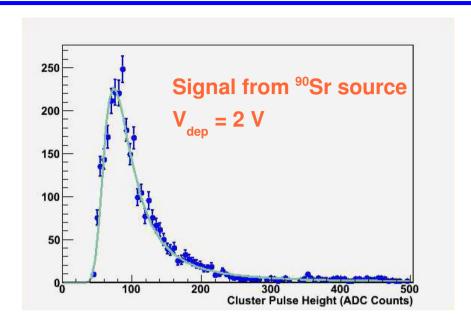

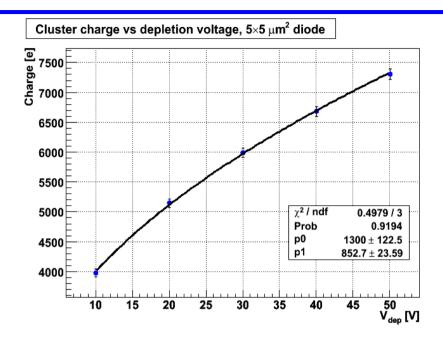

## First tests on LDRD-SOI-2 (analog pixels)

- First preliminary tests performed on analog pixels with  $^{90}$ Sr source and 1060 nm laser focused to a 5  $\mu$ m spot

- $^{\bullet}$  Signal vs. depletion voltage follows same trend as LDRD-SOI-1, back-gating effects becoming important for  $V_{_{dep}}{^{\sim}}10~V$

- Improved noise performance of analog pixels w.r.t. LDRD-SOI-1 (factor 3-5)

- $^{\bullet}$  Charge fraction distribution shows smaller charge spreading for higher V  $_{_{\text{dep}}}$

**PIXEL 2008**

## **Summary and Outlook**

- SOI-CMOS technology built on high-resistivity substrates allows the fabrication of reversely-biased silicon sensors integrated with full CMOS circuitry on the same device

- Two prototype pixel chips designed at LBNL in OKI deep-submicron FD-SOI technology

- LDRD-SOI-1 prototype in 0.15 μm process successfully tested:

- analog and digital pixel detection capabilities demonstrated with IR laser and 1.35 GeV e<sup>-</sup> at LBNL ALS

- back-gating effects significant at high substrate voltages and after irradiation with protons

- Second prototype LDRD-SOI-2 fabricated in optimized 0.20 μm process:

- currently being tested: both analog and digital pixels are functional

- \* first tests on analog pixels confirm results from LDRD-SOI-1 prototype with improved noise performance

- beam-test with 1.5 GeV electrons in October-November

- Several potential technology spin-offs for SOI monolithic pixels:

- thin, fast and integrated detectors for High-Energy Physics applications

- X-ray detection for application at synchrotron facilities

- VUV imaging for beam diagnostics, e.g. via thinning and back-processing; application foreseen at the plasma accelerator facility LOASIS @ LBNL

# **BACKUP SLIDES**

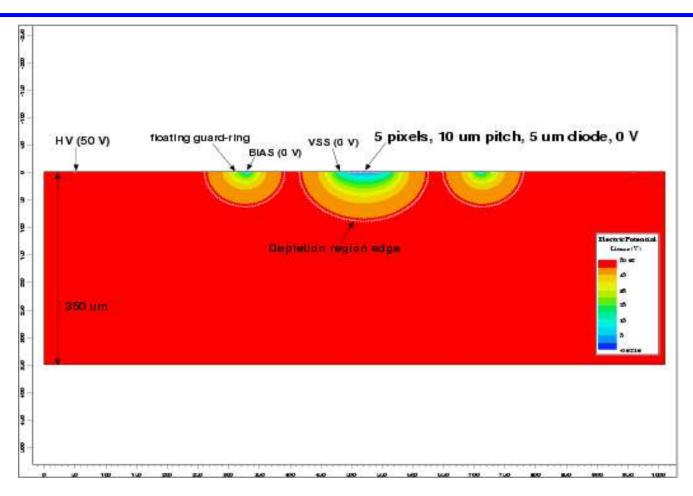

### **TCAD** simulations

- Simulation performed with Synopsys TCAD (Taurus Device)

- 2D model of 5 pixel cluster (10 µm pixel pitch) and substrate contact regions

- 350 µm thick substrate, n-type silicon (6×10<sup>12</sup> cm<sup>-3</sup>); 200 nm buried oxide

- Different diode sizes (1×1 μm² and 5×5 μm²)

**PIXEL 2008**

## Surface potential, choice of pixel guard-ring

- Pixel surface potential for different diode sizes and depletion voltages

- Potential in-between pixels too high, especially for smaller diode size

- Add floating p-guard structure (1 µm wide) to keep potential low and limit back-gate effects on MOS transistors on top of buried oxide

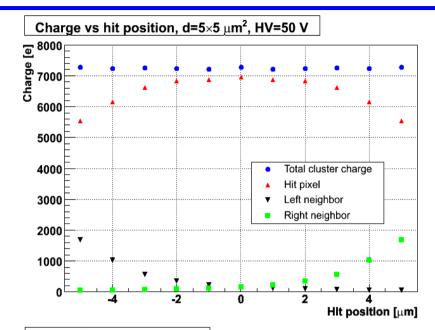

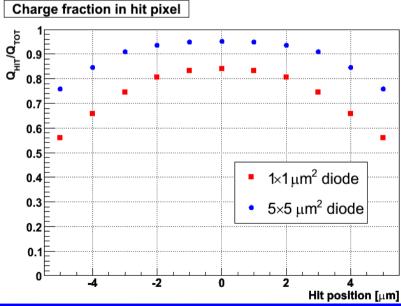

## Charge collection simulation

- Simulate passage of m.i.p. (80 e-h/μm) and charge collection in 5 pixel cluster

- Study collected signal as a function of depletion voltage and of track position within hit pixel

- Total cluster signal ~constant as a function of position within hit pixel

- Most of the charge is collected in hit pixel, expect larger cluster size for smaller diode pitch