#### Fermilab **BENERGY** Office of Science

## **Mu2e II Trigger/TDAQ Summary**

B. Echenard, G. Pezzullo

CalTech, Yale *for the Mu2e II Trigger Working group*8/30/18

### **Mu2e II implications for TDAQ architecture**

- Larger detector occupancy & beam-duty cycle

- Larger bandwidth needed to handle expected data flux

- x3-5 in the instantaneous rate, x3 duty cyle

- Higher rejection needed

- Guidance: no more than x2 in data storage 14 PB/y

- we need a factor x5 in the rejection

- Higher radiation delivered to the ROCs

- **PIP-II beam structure** with no phase shift in timing

- Consider to lock system clock to 162.5 MHz accelerator clock IF ok with electronics

- Reduced OFF Spill periods (to no OFF Spill time?) implies less advantage to large front-end buffers for streaming data

2

🚰 Fermilab

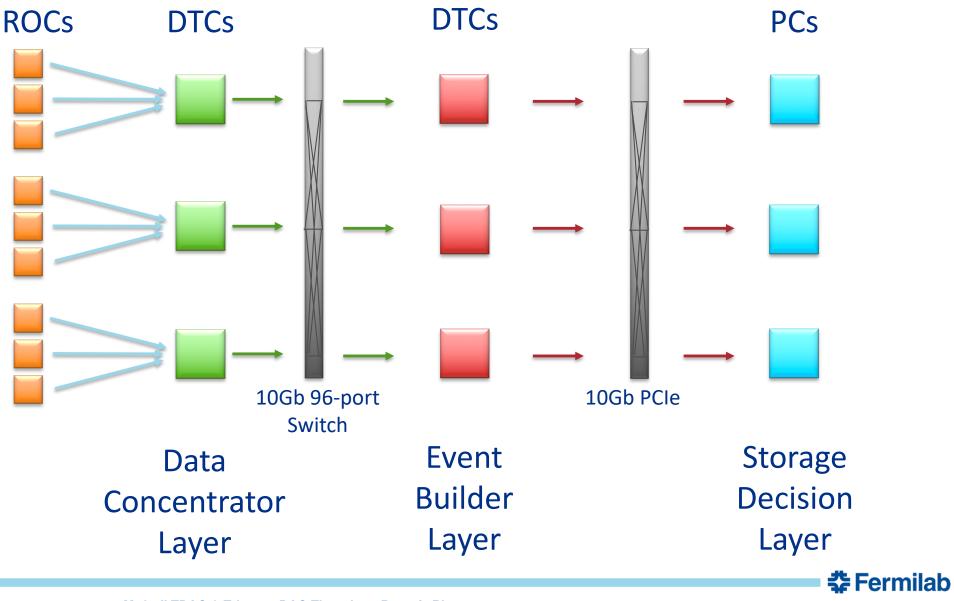

## **Generic Data Readout Applied to Mu2e-I**

Mu2e-II TDAQ & Trigger - DAQ Thoughts - Ryan A. Rivera

#### **TDAQ** architectures for Mu2e-II

- Expand current Mu2e architecture (1 level trigger):

- assuming x2 gain in tech, extrapolation of Mu2e system requires x5 more hardware

- larger DAQ room, power and cooling

- 100 Gb switches (Vs 10 Gb of today system)

- Will existing algorithm performance scale (now few ms/evt)?

- With retuning?

#### • 2 level Trigger

- do some processing on FPGA and the remainder on software

- Where are the boundaries?

- can we make a L1 trigger decision at FPGA level?

- Need to develop FPGA algorithms

🎝 Fermilab

#### **TDAQ** architectures for Mu2e-II (CRV)

- Independent CRV trigger on FPGA

- No significant OFF-spill period

- How much Cosmic data do we need?

- Develop dedicated CRV trigger?

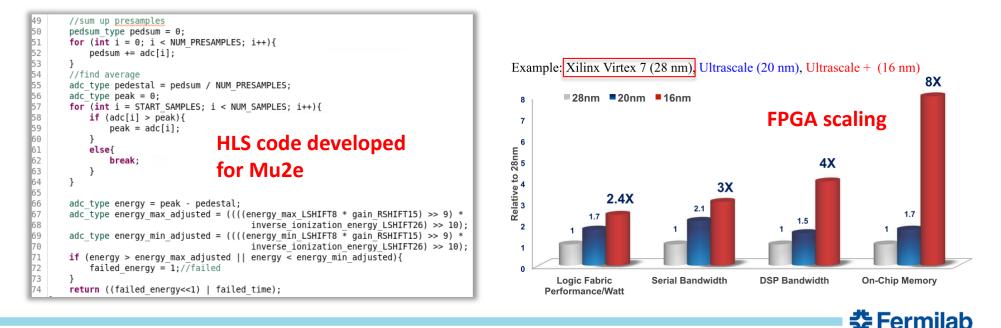

#### **FPGA considerations (1)**

- High Level Synthesis (HLS) is now good enough to rival manual VHDL or Verilog algorithm development.

- Allows physicists to easily develop FPGA algorithms

- development can take place now hardware is not needed!

- CMS is heavily investing in HLS

- <u>hls4ml</u> collaboration developing neural network tools using HLS

#### Current Mu2e timing architecture Mu2e timing architecture

- Mu2e has chosen a stable 40 MHz clock (system clock) from Clock Fan-Out (CFO) module

- Mu2e system clock is not locked to the Delivery Ring clock → experiment and beam are asynchronous

- CFO receives electrical signal associated with microbunches (DR turn marker), which is used to tell us...

- Microbunch timing with precision ~1 ns

- Timing within spill

See docdb-19095 for details

8/30/18

🛟 Fermilab

nilab

### **Mu2ell beam timing**

#### First thoughts on TDAQ thoughts re: beam timing

- Given increase of duty cycle from 25% to 97%...

- Pre-processing step with FPGA's? "Level-1+HLT" architecture?

- When to collect cosmic rays?

- When to perform calibrations?

- Given neither resonant extraction nor Delivery Ring...

- Implications of smaller pulse-to-pulse variation? (no spill structure)

- Work out new protocol to communicate "PIP-II beam to Mu2e" (i.e., replacement of DR turn marker)

- Given no phase shift of PIP-II RF...

- Consider to lock Mu2e-II system clock to 162.5 MHz accelerator clock

- Given that PIP-II timing is based on pulses every 6.15 ns...

- No action regarding structure within microbunch

- Don't omit possibility to vary spacing between microbunches

8

辈 Fermilab

nilab

#### VTRx

- We need rad hard optical link for Tracker and Calo ROCs

- Experiment "standard" for data transmission between ROCs and DTCs is the VTRx from CERN

- For Mu2e II we can follow CMS development for the next generation of rad hard optical links

- Keep looking for other options as well

### Summary / R&D projects

- Two possible architectures to investigate:

- 1 level: "expanded" Mu2e TDAQ system

- 2 levels: L1 Trigger + HLT

- Develop trigger algorithms for FPGA:

- Needed to set requirements on the hardware

- Evaluate performance/costs of the proposed architectures

- Cosmic rays study for CRV trigger

- Sim inputs for evaluating the expected doses in the ROCs

11 G. Pezzullo I Mu2e II Workshop @ Northwestern

8/30/18

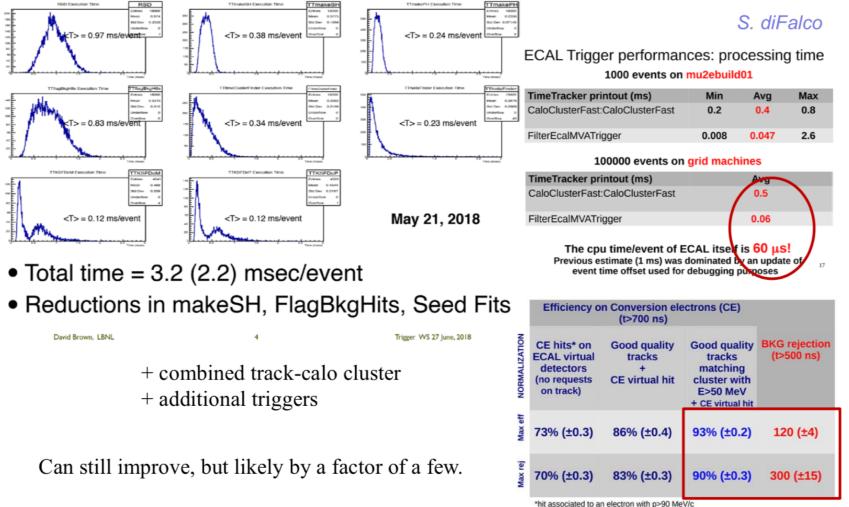

#### **Mu2e expected Trigger performance**

#### Triggers

#### Track Trigger Timing Status (triggerDev) D. Brown

Workshop @ Northwester

nilab

p. 5

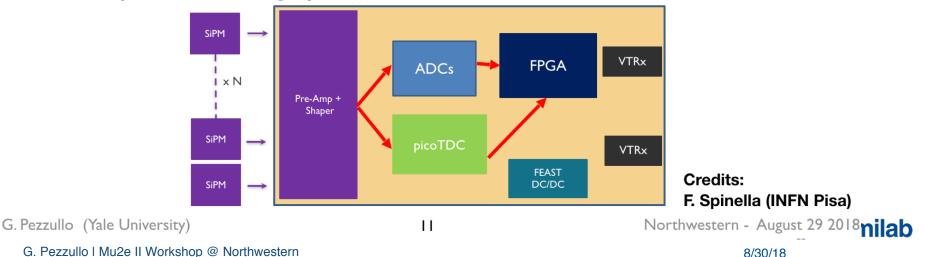

# Possible ADvanceD-DIRAC

- Instead of sampling the waveform we want to use TDCs for precise time reconstruction

- Rad hard ADC @ 50 MHz for charge reconstruction?

- The **PolarFire** FPGA is supposed to be sufficiently rad hard

- VTRx optical transivers

- The board will include also the PreAmp+shaper (thanks to the SiPM high gain)

⇒TID reduction & neutron flux by a facto of ~ 10

⇒simplified cooling system

# Future Tracker ROC?

- We don't know yet the Mu2e II tracker design!

- **Assuming** to use the same technology, we need smaller straws to handle the larger hit rate, thus more channels

- "bigger" DRAC boards?

- → larger bandwidth required (?)

- BUT, scaling to x10 the expected radiation levels makes majority of the components not well suited

- R&D to find commercial rad tolerant components

- possible mitigation strategies in the experimental setup?

- improved shielding design

- changes in the beam line