# **CPAD2018** Review of the Superconducting Detector **Sessions**

Pete Barry, Hsiao-Mei Sherry Cho and Ben Mates

#### Overview

Attempted to survey current state of instrumentation + future technology directions

- 3 parallel sessions

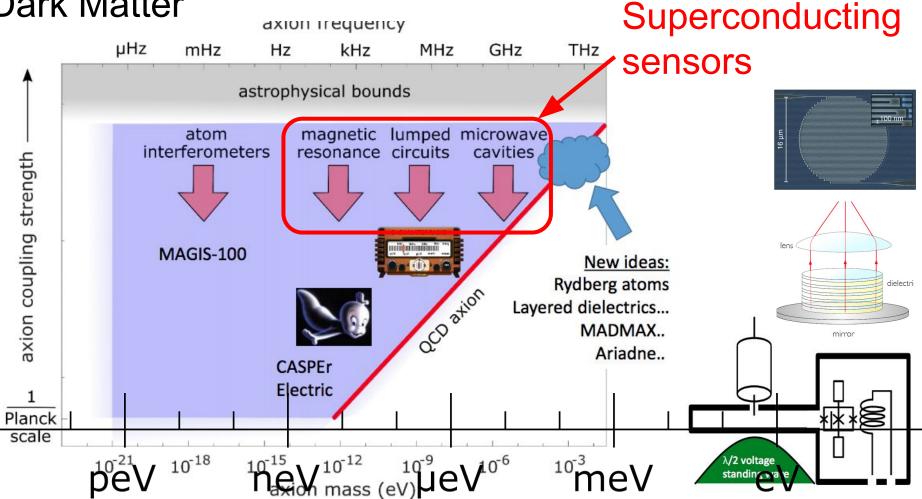

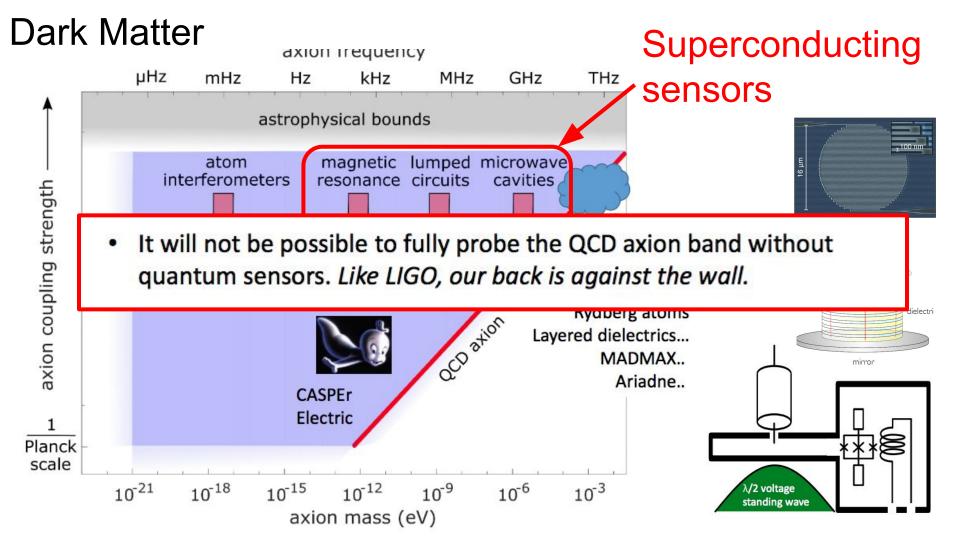

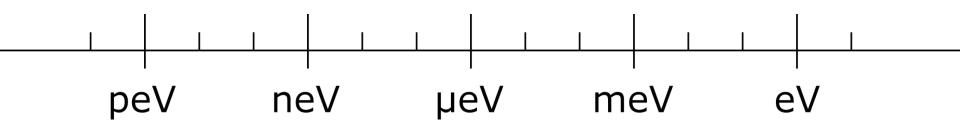

- Dark matter and  $0\nu\beta\beta$

- Cosmic Microwave Background (CMB)

- Readout technologies

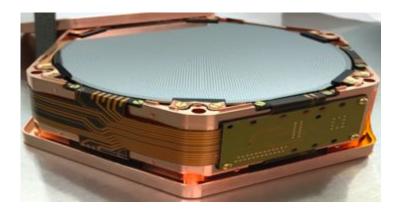

Superconducting nanowire detector for optical haloscope

< 1 dark count per second per sq. cm

#### Transition-edge sensors for detector of optical phonons

# Cosmology (CMB)

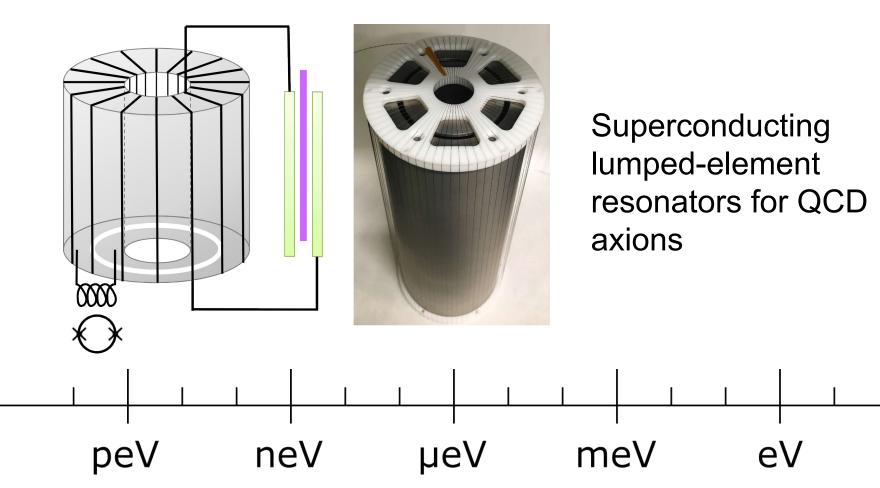

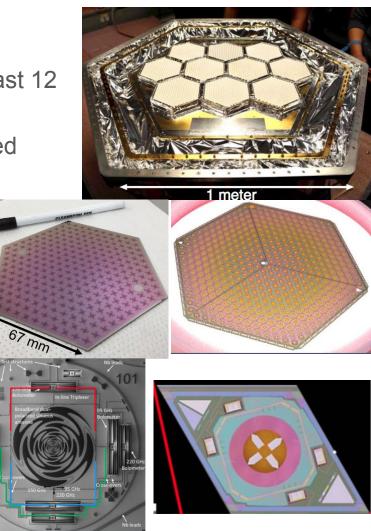

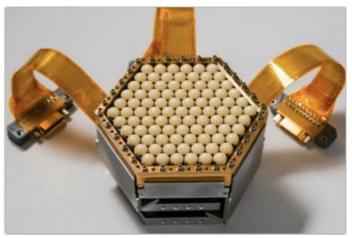

- Manufacture of TES detectors has matured over last 12 months → preparation for CMB-S4

- Required sensitivity/detector routinely achieved

150 GHz, Chip( 230 GHz, Chip)

- Uniformity across 6 inch wafer is sufficient for CMB-S4

- Improvements in yield have been a major achievement

- Quality control and assembly are the next challenges to solve for large scale arrays

## Cosmology (CMB + beyond)

- What comes next? CMB-S4 (~50k/telescope ~ 500k detectors)  $\rightarrow$  ???

- Extrapolating from trend over previous 15 years → even more detectors → need to <u>push toward ~MPixel arrays</u>

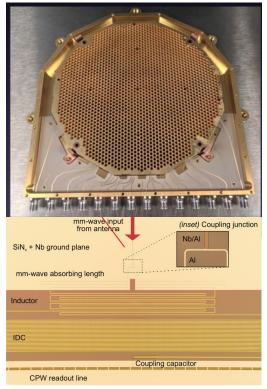

- MKIDs

- Built-in multiplexing offer elegant solution to massively multiplexed arrays

- Frequency domain multiplexing of TESs

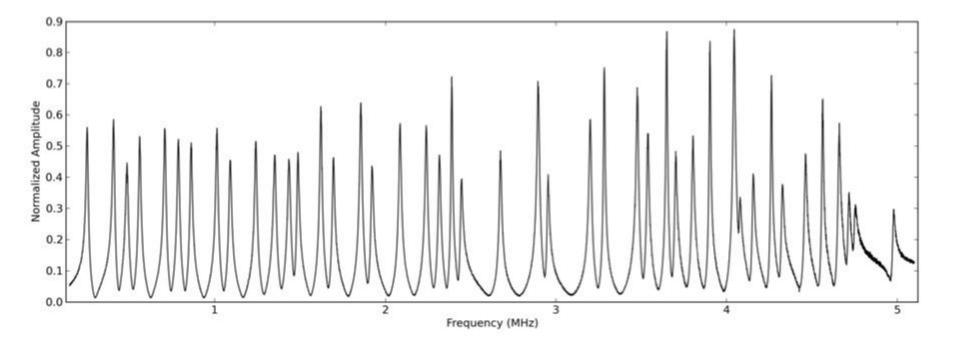

#### Readout: MHz Frequency Multiplexing

Each detector modulates a distinct MHz carrier

#### Readout: MHz Frequency Multiplexing

68x multiplexing factor demonstrated on fielded instrument

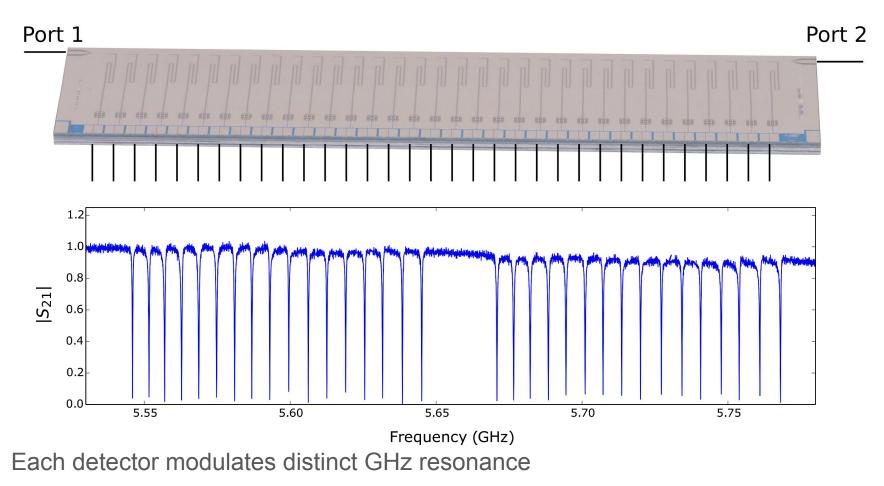

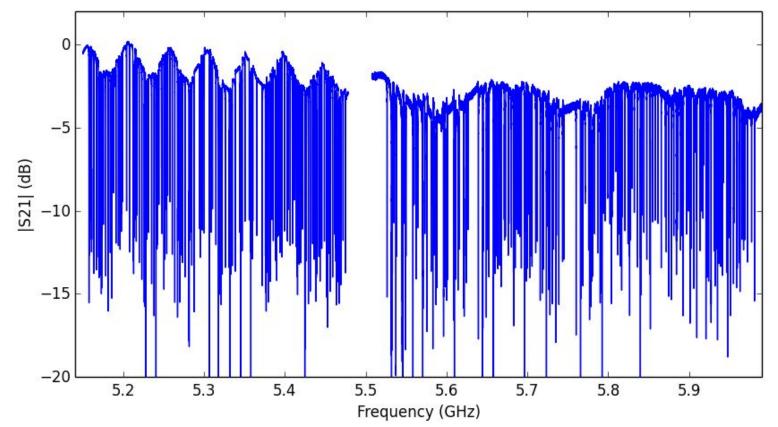

#### Readout: GHz Frequency Multiplexing

#### Readout: GHz Frequency Multiplexing

Targeting ~2000 channels in 4 GHz for CMB

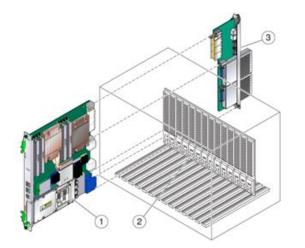

#### Readout: Software-defined Radio

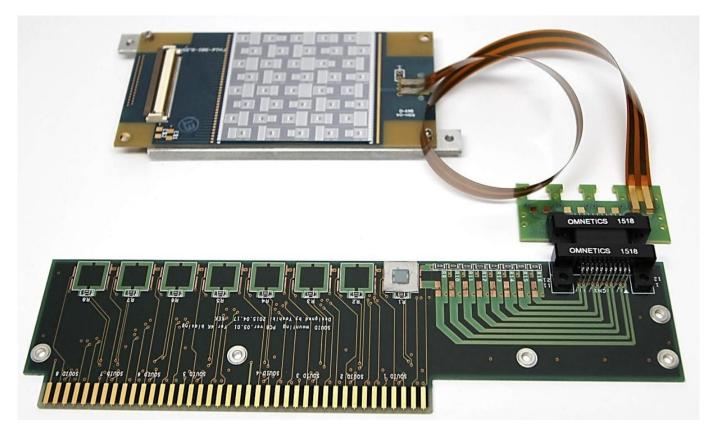

Room-temperature digital electronics critical for practical readout

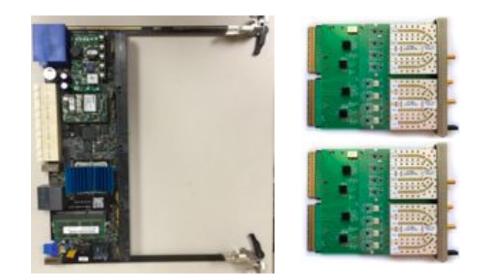

SMuRF readout, built on SLAC common platform

Readout electronics generate and demodulate GHz carriers (e.g. SMuRF)

#### Readout: System-on-a-chip

#### RFSoC = FPGA+CPU+DAC+ADC

- 8x 4 GS/s 12-bit ADCs

- 8x 6.4 GS/s 14-bit DACs

Simplify and reduce cost

Future: readout of complete GHz multiplexer on a single chip