# Responsibilities & Timeline (Discussion Fuel)

Cubism - Braque's Bottle and Fishes, Paris c.1910-12

Collaboration Meeting Bern, March 2019 James Sinclair, LHEP <sup>1</sup>

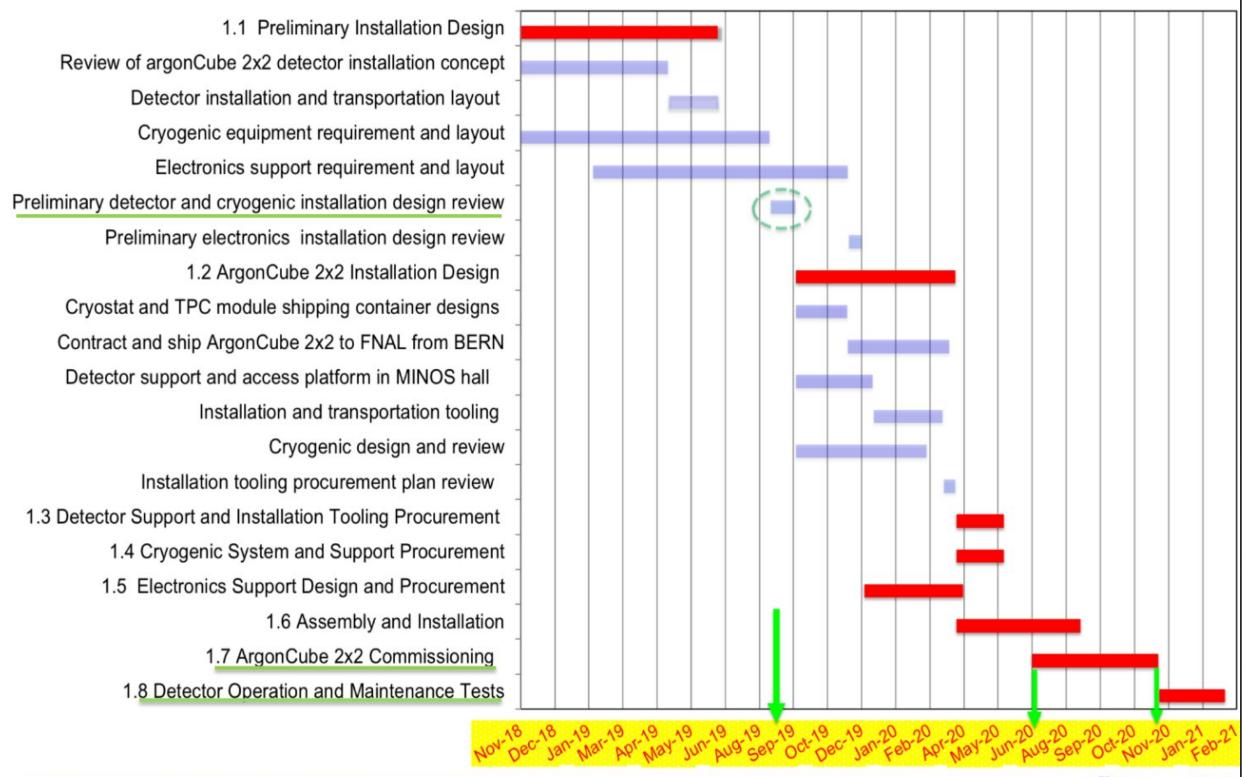

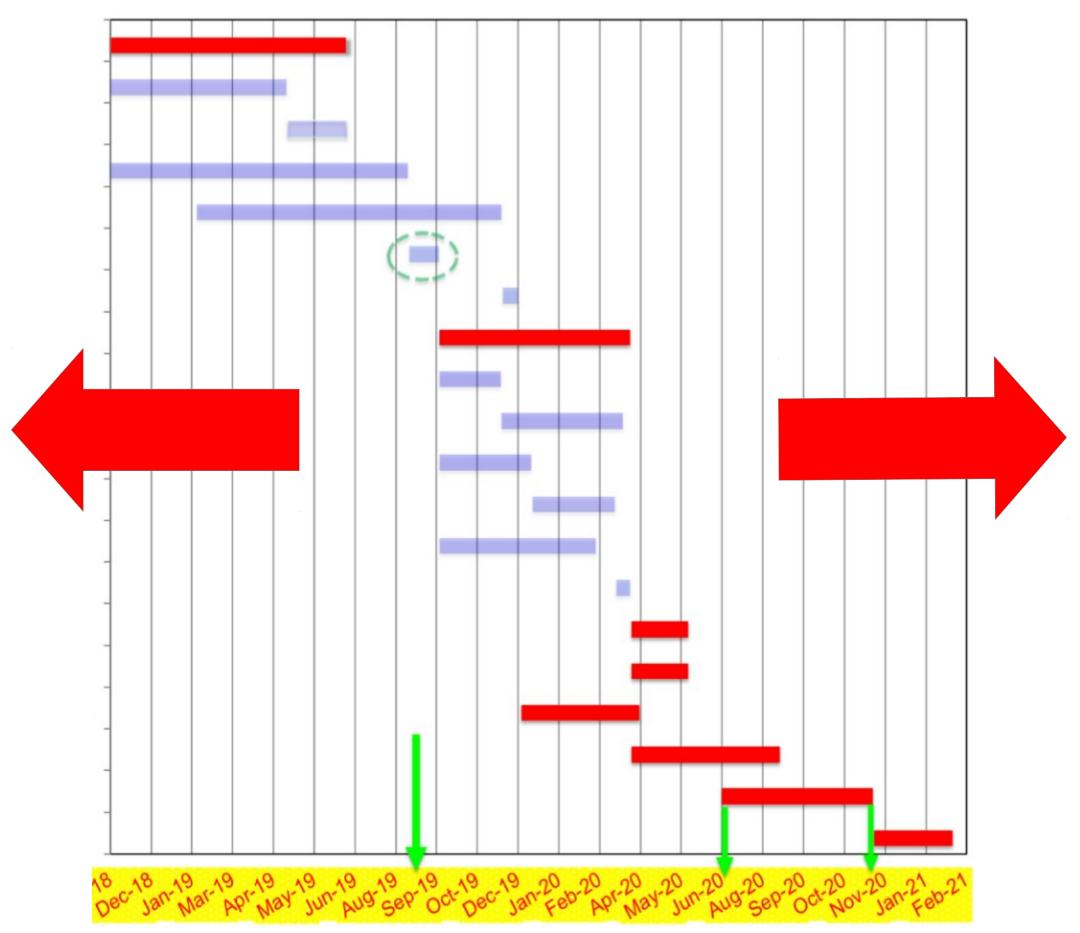

### **Schedule in Graphic**

3/22/2019

### ArgonCube2x2@MINOS Schedule

**Fermilab**

Ting Miao / ArgonCube2x2 at Fermilab

## LArPix-v2 Schedule

#### To meet 2x2 Demonstrator needs, 2019 schedule is aggressive:

#### Move directly to full ASIC production (skipping small-scale pre-production)

- Engineering production of ~7500 v2 ASICs (Mar. → slipping to Apr.)

- Limit v2 modifications to only those that are necessary and low-risk.

- Postpone other desired changes for future v3 ASIC

#### **Component testing:**

- 1) Detailed characterization of the unpackaged LArPix-v2 ASIC (Jun)

- 2) Detailed characterization of the packaged LArPix-v2 ASIC (Jun-Jul)

- 3) LArPix-v2 ASIC qualification (Jun-Oct)

Targets: Jun ~100-200 ASICs; Aug ~2000 ASICs; Oct ~8000 ASICs

4) Unloaded Pixel tile PCB qualification (May-Oct)

Brief assessment of each PCB before component/ASIC loading.

Targets: Jun ~5-10 small prototype tiles; Aug ~20 tiles; Oct ~72 tiles

#### Pixel tile testing:

1) Prototypes tile testing (Jul-Aug)

Test a small number (5 to 10) small-scale (maybe ~16cm x ~16cm, ~25 ASICs) prototype tiles using the v2 ASIC. Key questions:

- Is tile design adequate?

- Is additional ASIC qualification (e.g. cryo socket testing) needed before tile assembly?

#### 2) Initial full-scale tile testing (Sep-Nov)

Test a moderate number (~20) of production scale (~32 x ~32, ~100 ASICs) pixel tiles. Send to Bern and install in first 2x2 module.

3) Remaining full-scale tile testing (Nov-Feb)

Test enough (~52?) of production scale pixel tiles to instrument the 3 other 2x2 modules, plus ~10% spares. Send to Bern and install in the remaining 2x2 modules.

Mar. 21, 2019 LArPix-v2: Progress and Questions

4

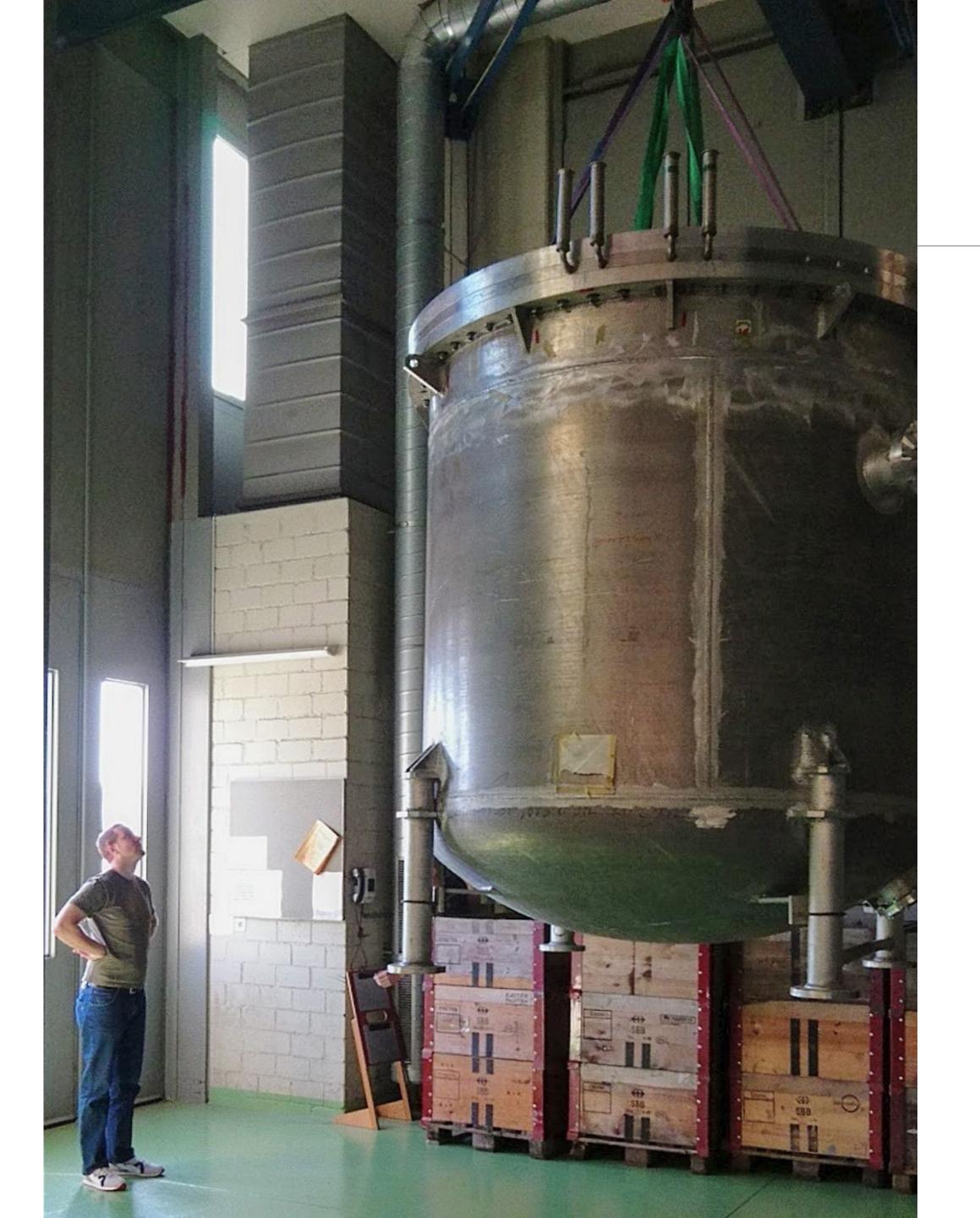

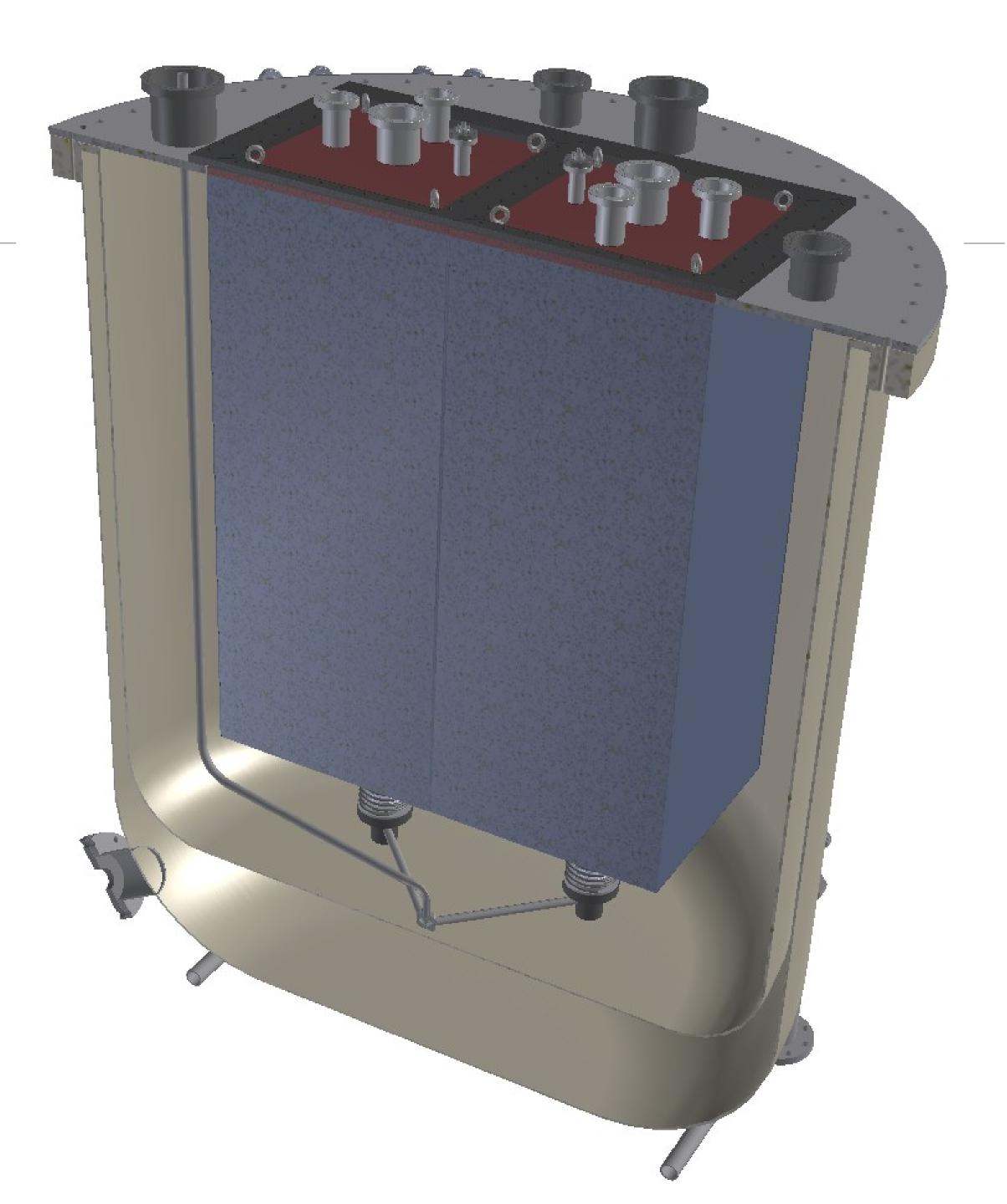

Knut's ArgonCube Modue in chalk, Bern 2019

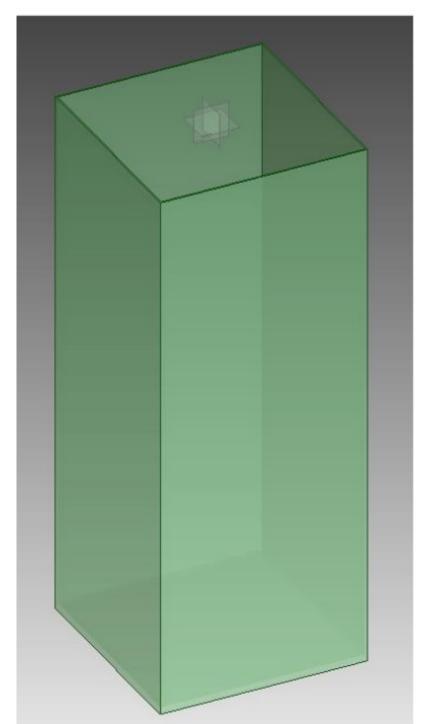

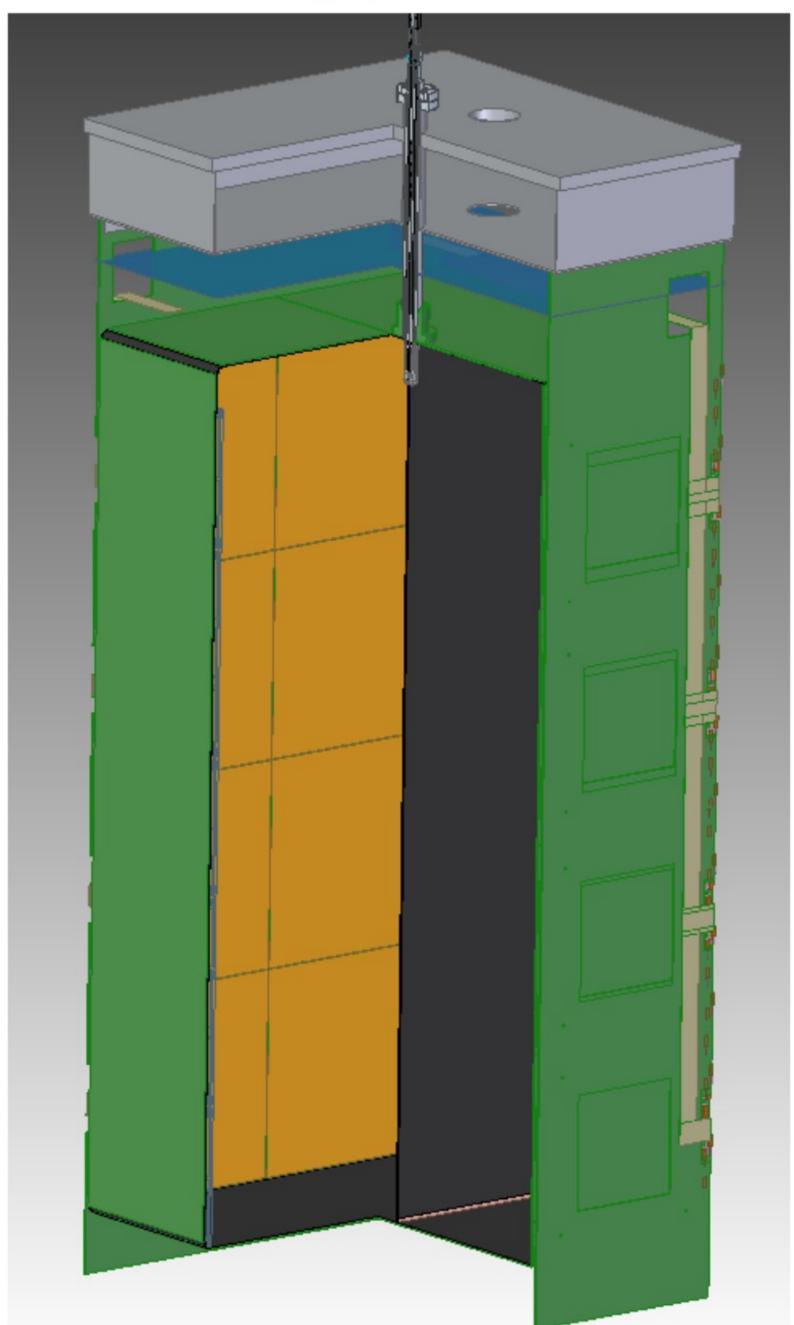

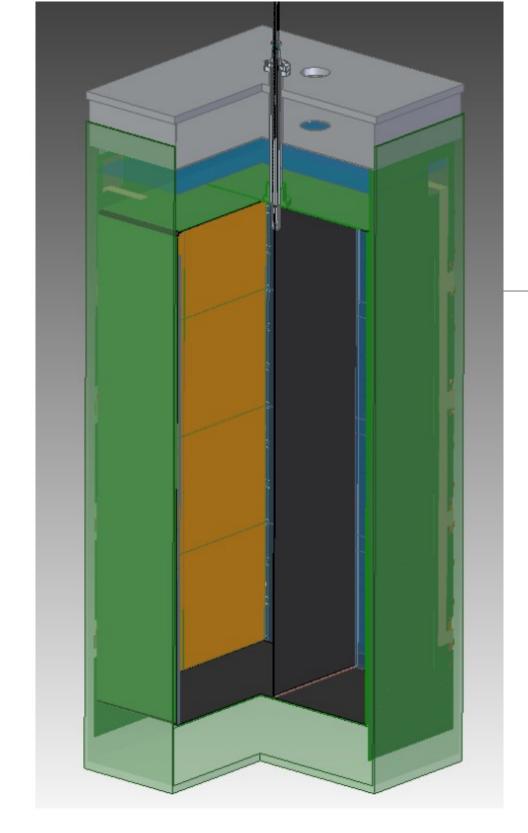

### Naked TPC hangs under insulating "pillow"

Many updates already implemented bus still must be tuned-

Fiberglass "bucket" is hermetic (check valves on bottom)

Fiberglass bucket bonds to pillow with shearable bond for removal

# Next - Interface Definitions

Interfaces have to be defined between individual components, along with test schemes of of interfaces.

- -Charge R/O

- -Light R/O

- -TPC + HV

- -Cabling

- -Module Structure + Cryostat

- –DAQ (event builder)

Resources loaded plan has now to be written incorporating all these, and integrate with Ting's (expanded, NOT extended).

# 2x2 Points of Contact (interface responsibles)

Module Structure + Cryostat – James, Bern

Charge R/O – Dan, LBNL

Light R/O – Nikolay, JINR

TPC + HV - Ran, SLAC

Cabling – Jonathan, UTA

DAQ + Beam trigger – Clarence, Rochester

FNAL installation – Ting, FNAL

Simulation – Kazu, SLAC