### input/output tests at Bham

Francesco Gonnella and Richard Staley

University of Birmingham

### ZCU102 setup

- ZCU102 delivered to Bham (thanks to Dave)

- Board successfully connected to Vivado via JTAG

- Clock programmed through micro USB serial link

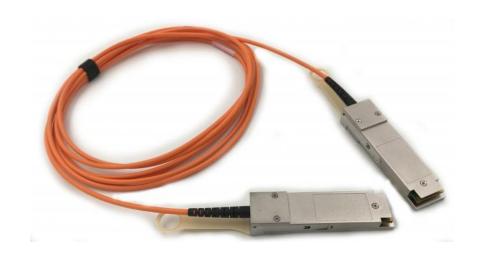

- An external loop was made with an optical fibre using SFP module

- A bitfile with IBERT (4 MGTs) was generated and programmed into the FPGA

- Communication tests were performed

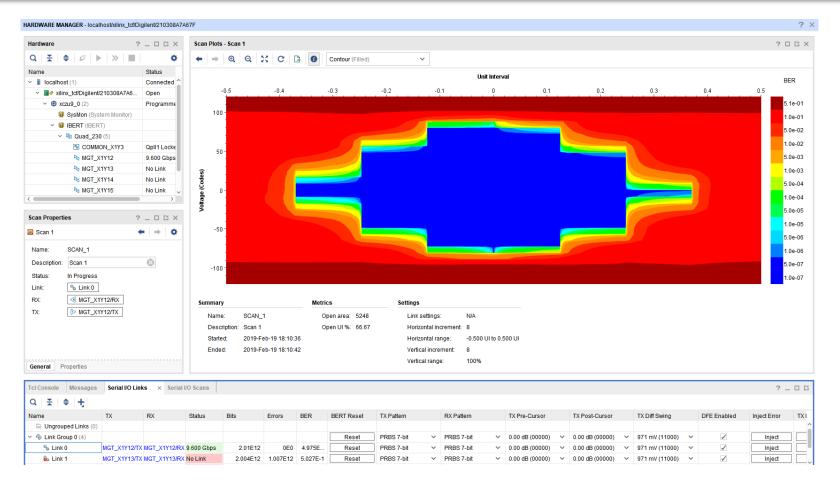

# Eye diagram on ZCU102

- This is the eye diagram on the IBERT GUI

- Test was done with single SFP fibre connector

## Next steps

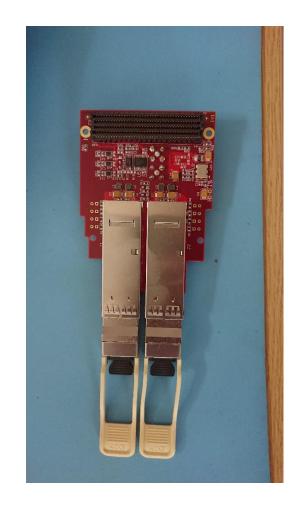

- Repeat the same exercise using the FMC board with QSFP+ connectors

- We need a short length 4-channel fibre ribbon cable to loop back to and from the QSFP+ connector on the FMC board

- Each channel has tx and rx, so we will be testing all the 8 channels

## Conclusion and future plan

- The communication between the WIB and the ZCU102 will be done through an FMC card.

- We need the details of this card: pinout, signals, clock, etc

- We used Si5345 IC (the same that is on the FELIX) the on the ZCU102 to program the transceivers

- Should we use the on-board clock of the FMC card?

- On the firmware repository side we are still trying to create the Vivado project and integrate the MGT IP cores created by Richard for the communication tests

- Will try last suggestions from Dave for IPBB operation

- Once we get there, we will need help/documentation of the existing firmware blocks

- Our plans for the next future are:

- Francesco will work at the data formatting

- Richard will handle the MGT communication

### Thanks for your attention

Francesco Gonnella