Ryan LaZur New Perspectives

View Overview of the Cold Electronics of SBND

1 / 17

## **SBND TPC Electronics**

#### You listened to an overview of SBND (in 10 minutes)...

**Ryan LaZur New Perspectives**

Overview of the Cold Electronics of SBND

2 / 17

## **SBND TPC Electronics**

...Now we will discuss the readout electronics in more detail!

# **SBND Readout Electronics**

## **Brief Overview**

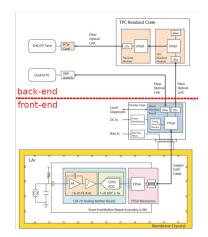

- The goal of the TPC readout electronics is to amplify, shape, digitize, and losslessly compress TPC ionization signals while maintaining high signal-to-noise ratio

- The SBND electronics build upon technology employed at MicroBooNE and has similar components to ProtoDUNE

- See Maura's talk at noon tomorrow

# **SBND Electronics**

#### Front-end and Back-end

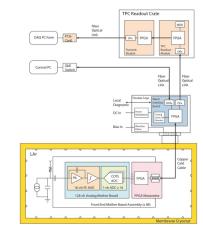

- Components inside the cryostat provide gain and shaping then digitize and multiplex the signal

- Warm interface components configures components inside cryostat and convert digital signal to optical and can be programmed by external PC

- The back-end (BE) electronics compress and store the data for later analysis

# **SBND Front-End Electronics**

## **Cold electronics**

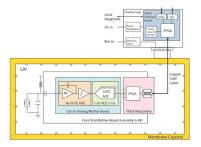

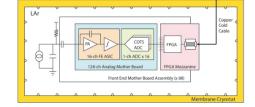

- FE application specific integrated circuits (ASICs)

- Analogue-to-digital converter (ADC) ASICs

- Field-programmable gate arrays (FPGAs)

- Other components qualified in cryogenic operation

- Warm interface boards (WIBs)

- Cold cables

#### **Ryan LaZur New Perspectives**

#### Overview of the Cold Electronics of SBND 7 / 17

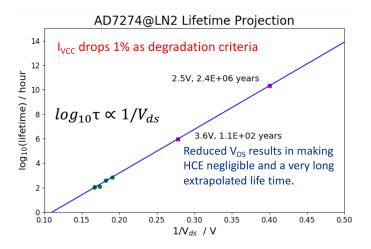

## Front-End Motherboard

**FEMB**

- Each FEMB handles 128 channels of TPC readout

- 8 FE ASICs ×

16 channels/ASIC

= 128 channels

- 128 single-channel commercial-off-the-shelf (COTS) ADCs

- Single FPGA per FEMB multiplexes the 128 channels and stores input from DAQ/external PC

- 11,264 channels per SBND / 128 = 88 FEMBs

# **SBND Cold Electronics**

## Motivation

- Increased detector design flexibility

- Less cabling

- ★ Less TPC penetrations

- $\star$  Less outgassing

- Improved signal-to-noise ratio

- Reduced thermal and capacitive noise

ICARUS multiplex outside cryostat necessitating many feedthroughs

**Electronics Noise:**

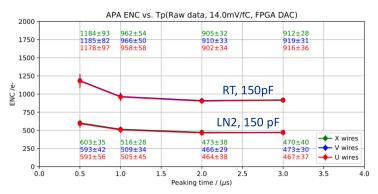

$$ENC^{2} \approx \frac{1}{2}A_{1}\frac{e_{n}^{2}C_{in}^{2}}{t_{p}} + A_{2}\pi C_{in}^{2}A_{f} + A_{3}\left(q_{e}l_{0} + \frac{2k_{B}T}{R_{b}}\right)t_{p}$$

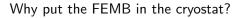

# **ADC ASIC Testing**

#### Test Setup

- The SBND ADC ASICs, unlike those in MicroBooNE, are in the LAr

- SBND will employ commercial (COTS) ADCs

- Tests at BNL and Manchester qualify the ADC ASICs for use in SBND

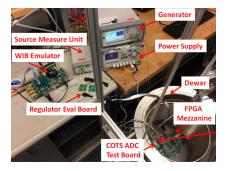

## **ADC ASIC Testing**

#### Lifetime Results

Lifetime projection is  ${\sim}2.4\,\times\,10^6$  years at 2.5V operation

# **FE ASIC** Testing

## **Testing Setup at BNL**

- Custom extended motherboard submerges FE ASICs in LN2

- Custom MSU Cryogenic Testing System (CTS) allows for quick, semi-automated testing

**Testing Summary**

- Each FE ASIC was tested for proper pedestal, pulse response, and power cycle resilience

- 1,200 LArASICv7 passed testing at BNL over the course of < 2 months to be used at ProtoDUNE and SBND

- Testing time was optimized to take  $\approx 1$  hour with significantly reduced chip breakage

- LArASICv7s are custom BNL FE ASICs used at SBND and ProtoDUNE

- A similar testing procedure should be implemented for DUNE

## Room vs Cryogenic Temperatures

- Equivalent noise charge (ENC) is a noise metric

- Factor of two reduction in noise in cold (LN2) vs room temperature

# **Cold Electronics Activities**

## **Production and Integration**

- CE production

- All FEMBs must pass 6 hour QA/QC tests

- Half of all components have arrived at FNAL

- CE integration

- Final integration test with FE and BE scheduled for June 18<sup>th</sup> at Nevis Labs

## Installing Cold Electronics to TPC

### In the Detector Assembly Building

# In Conclusion

- The SBND FE electronics are employing FE ASICs, COTS ADC ASICs, and FPGAs **in LAr** to improve the signal-to-noise ratio and simplify detector design

- R&D at SBND will greately benefit future LArTPC experiments, such as DUNE, as they might share similar components and production techniques

## **Thanks for Listening!**

## **Questions?**

## Slides

Ryan LaZur New Perspectives

Overview of the Cold Electronics of SBND 18 / 17

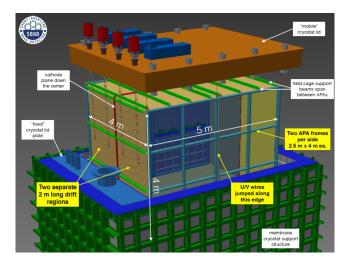

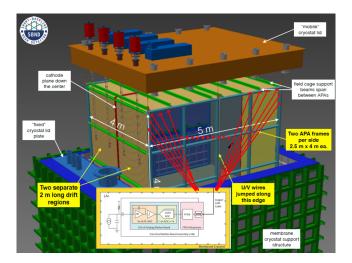

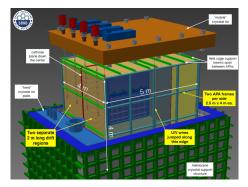

## The Short-Baseline Near Detector

## SBND

- A 112 ton liquid argon time projection chamber (LArTPC)

- $(4 \times 4 \times 5)$  m active volume

- Two drift volumes

- 3 wire planes: 0,  $\pm 60^{\circ}$

- ★ 3 mm wire pitch

- \* 11,264 total wires

- 110 m downstream from the Booster Neutrino Beam (BNB) target at Fermilab

- 8 GeV protons on a beryllium target

- Detector is under construction

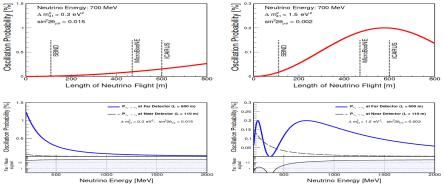

# **Physics**

## Physics goals of SBN

- Oscillation searches

- World-leading  $\sim 1$  ev sterile neutrino sensitivity

- $\nu_e$  appearance and  $\nu_\mu$ disappearance channels

- High statistics cross section studies

- Testing beyond the Standard Model theories

Machado, Pedro AN, Ornella Palamara, and David W. Schmitz, "The Short-Baseline Neutrino Program at Fermilab," arXiv preprint arXiv:1903.04608 (2019).

20 / 17

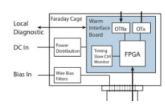

# Warm Interface Electronics

## WIECs and WIBs

- Warm interface electronics crate (WIEC) installed on each flange and contains the following

- Six WIBs (each can control up to 4 × 128 channels)

- One Power and timing backplane (PTB)

- One Power and timing card (PTC)

- WIECs are the interface between FE and BE electronics

- Convert signal to optical

- Timing, control, and monitoring functionality

**Ryan LaZur New Perspectives**