### **B05 : CE Concentrator ASIC**

### Jim Hirschauer (Fermilab), L3 Manager CD1 Review October 23, 2019

- Introduction and scope

- Conceptual design

- Cost, schedule, risks

- Organizational aspects

- Contributing institutions and resource optimization

- Quality assurance and quality control

- Prototype 1 plan and progress

- Summary

### **Biographical sketch**

Fermilab Scientist

### HL-LHC upgrade:

- L3 manager for Endcap Calorimeter (EC) Electronics and services

- Lead physicist for ECON ASIC development/production

- iCMS coordinator for EC On-Motherboard Electronics

### Phase 1 hadron calorimeter (HCAL) upgrade experience:

- L3 manager for barrel/endcap readout electronics 2013-2019.

- Lead physicist for QIE10/QIE11 readout ASIC development/production

- Helped lead team through CD-1, CD-2/3, and CD-4.

- iCMS coordinator for HCAL barrel/endcap upgrade 2013-2019

### **Other experience:**

- HCAL Operations Coordinator 2011-12.

- Chair of HCAL Institution Board since 2018.

Research focus: Searches for supersymmetry in fully hadronic final states.

### Introduction and scope

J. Hirschauer | CE Concentrator -- DOE CD1 Review

Oct 23, 2019

4

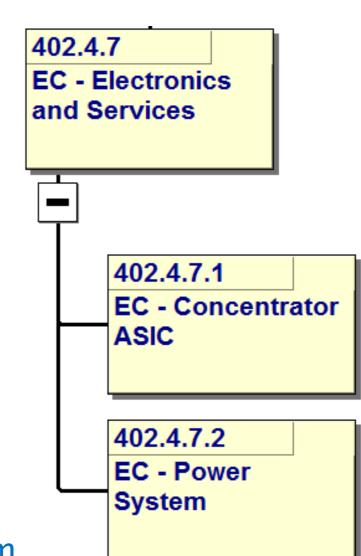

### **Deliverables and WBS structure**

- 402.4.7.1 Concentrator ASIC

- WBS includes specification, design, prototyping, prototype testing, production, packaging, and quality control of the "ECON" ASICs.

- Deliverable is fully tested set of ASICs for entire EC.

- Focus of this presentation.

- 402.4.7.2 Power system

- All scope included in objective KPP

- US is responsible for 40% of the low voltage (10V for electronics) and high voltage (1kV for Si bias) systems.

- WBS includes specification, prototype evaluation, procurement, and QC of the US fraction of the power system.

- Deliverable is 40% of the tested power system.

Charge #7

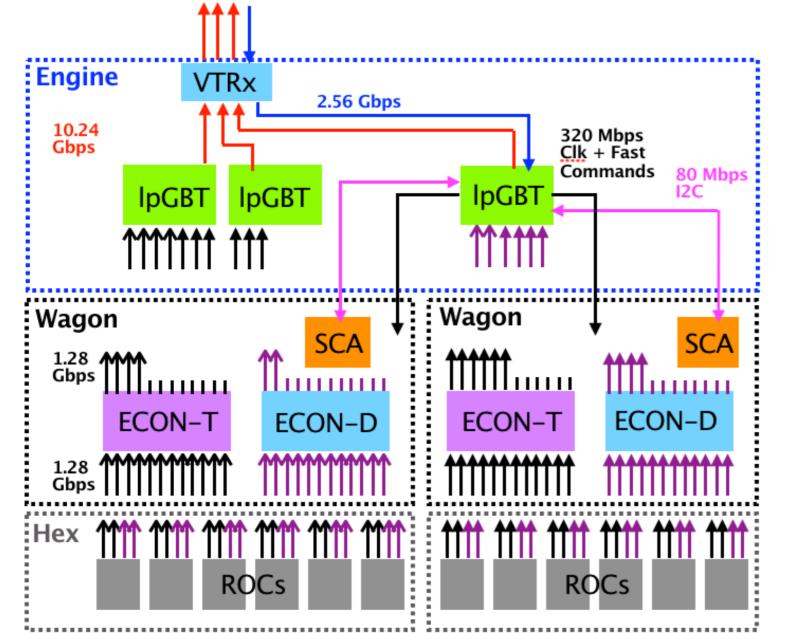

### Summary of ECON purpose

- EC has 4.3M trigger channels each sending >10 bits of data at 40 MHz.

- Naively requires 215k lpGBT links costing \$90M at \$400/link.

- However, interesting energy is deposited mostly in the central part of the detector.

- Bandwidth density is lower in outer part of detector.

- ECON will select and concentrate data associated with interesting energy depositions to maximize use of available bandwidth.

- ECON-based system requires 7k links instead of 215k.

Charge #1

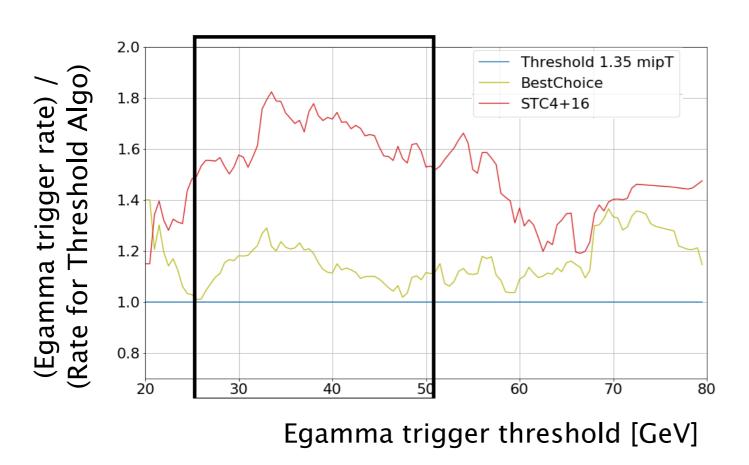

- Two data paths:

- 40 MHz trigger (TRG) data: ECON aggregates, selects/ compresses, serializes, and transmits to lpGBT.

- 750 kHz of (DAQ) data: On L1 accept, ECON applies zero suppression, aggregates, serializes, and transmits to lpGBT.

J. Hirschauer | CE Concentrator -- DOE CD1 Review

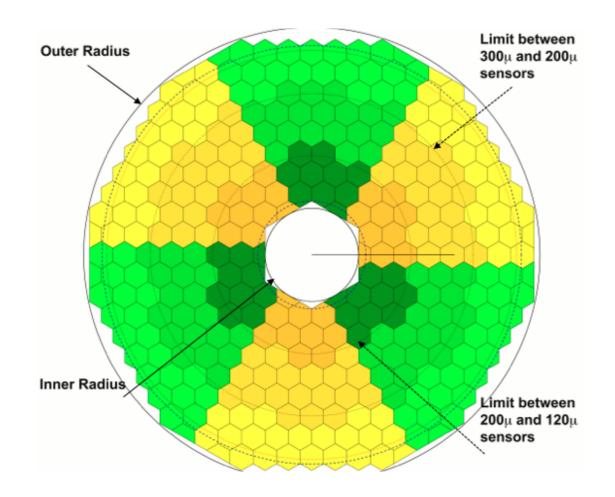

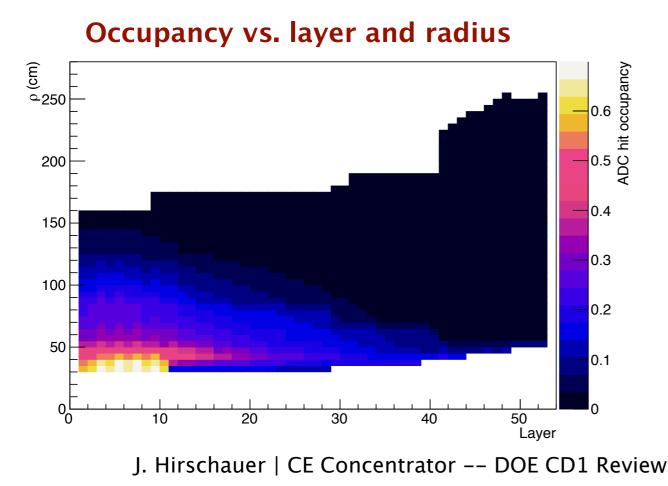

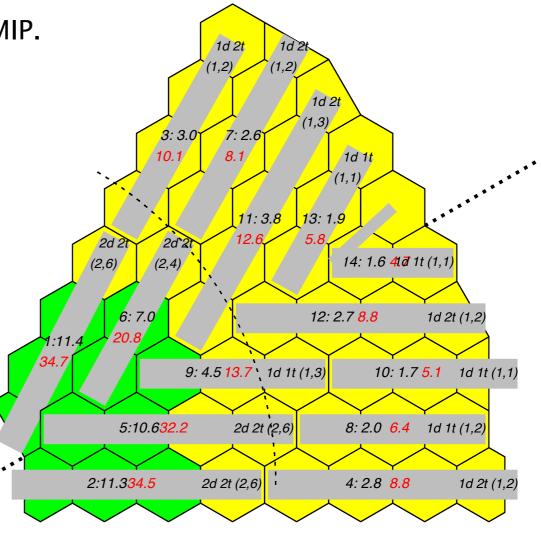

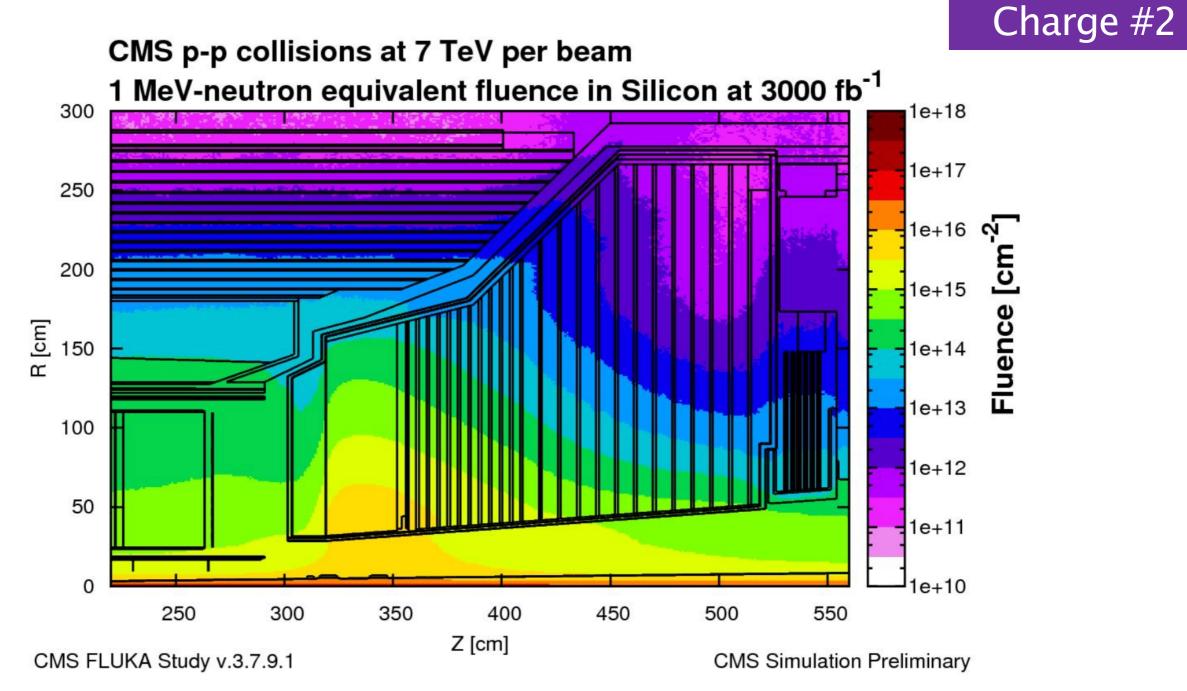

### **Occupancy and data rates** Charge #2

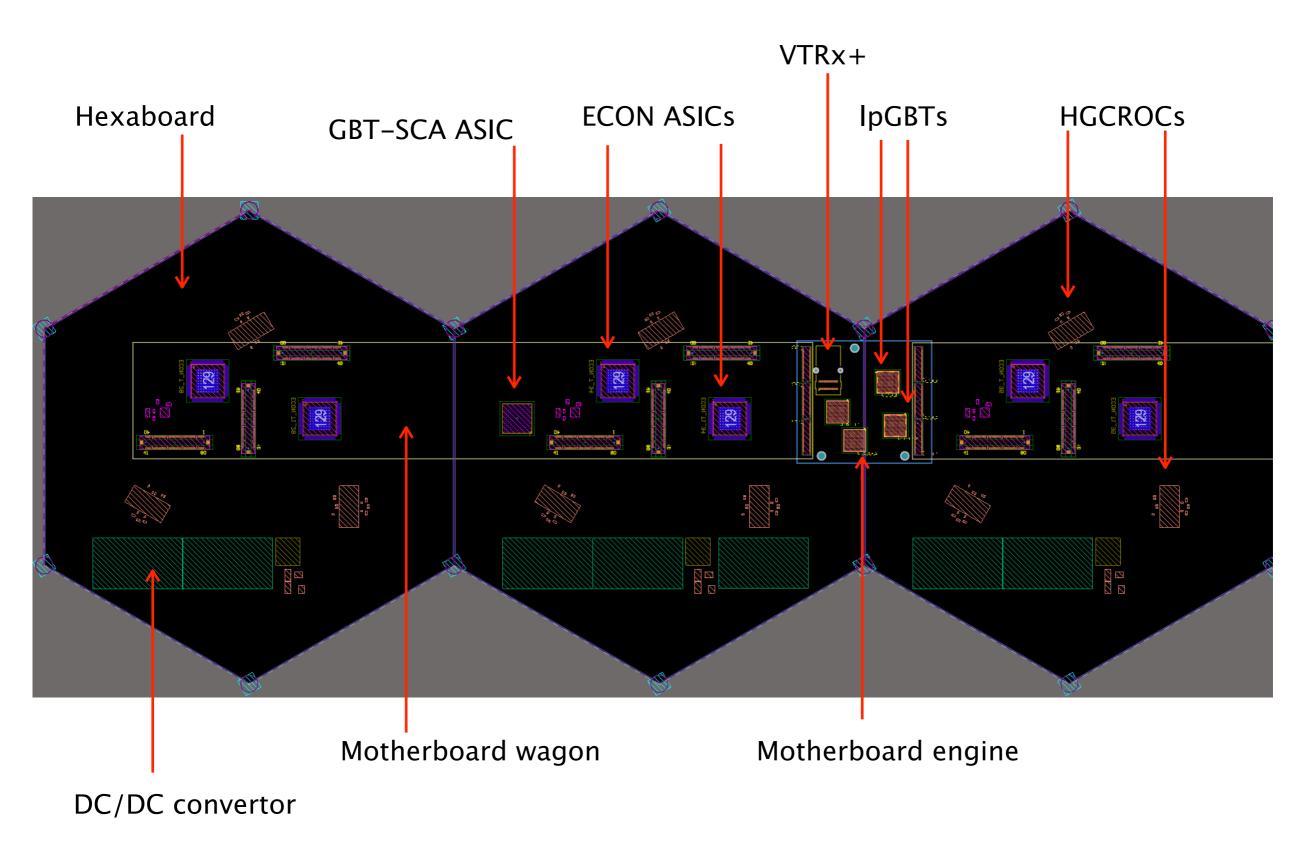

Plane 6 seen from Motherboard

- Motherboard layout for 6th CE-E layer with data rates

- Includes overhead associated with data headers, alignment patterns, etc.

- Red numbers are TRG data rates [Gbps]:

- Based on simple threshold-based algorithm: read out all TRG data for channels with E>2 MIP<sub>T</sub> and sum of energy in each ROC.

- Black numbers are DAQ data rates [Gbps] for E>0.5 MIP.

- Occupancy and data rates are well understood.

Layer 6 Module and Motherboard candidate layout

Oct 23, 2019

# **Conceptual design**

J. Hirschauer | CE Concentrator -- DOE CD1 Review

Oct 23, 2019 10

### **Relevant requirements**

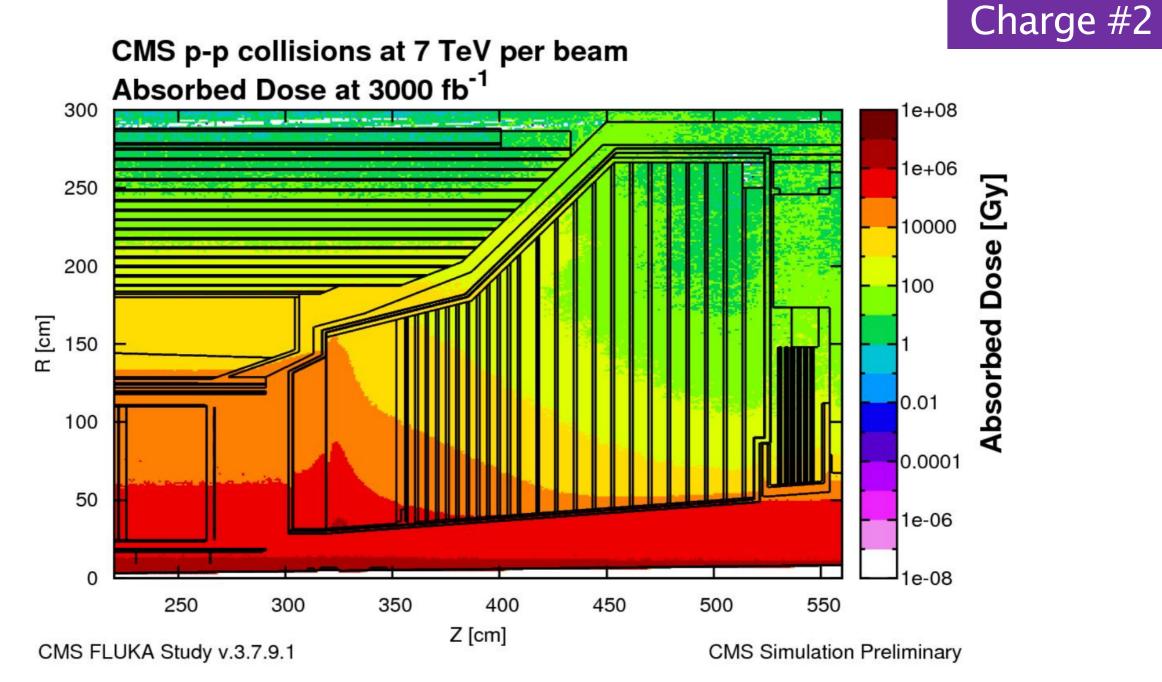

- EC-sci-engr-010: radiation tolerance for 10 year HL-LHC operation.

- EC-engr-083: ECON rad tolerant to 2 MGy, 1x10<sup>16</sup> 1MeV-equivalent neutrons/cm<sup>2</sup>, with SEU compliance

- expect maximum of 300 kGy and 3x10<sup>16</sup>/cm<sup>2</sup> on-detector

- EC-sci-engr-011: fit within evolving CMS HL-LHC upgrade requirements of interfacing systems.

- EC-engr-084: ECON power consumption ≤5mW/channel

- EC-sci-engr-008: provide trigger info at 40 MHz w/ 5µs latency

- EC-sci-engr-012: readout bandwidth to accommodate luminosities up to 7.5e34/cm<sup>2</sup>/s and trigger rates up to 750 kHz.

- EC-engr-081: ECON TRG data transmission at 40MHz and DAQ data transmission at 750 kHz

- EC-engr-082: ECON max latency is 16 BX

- Link: <u>https://cms-docdb.cern.ch/cgi-bin/DocDB/ShowDocument?docid=13447</u>

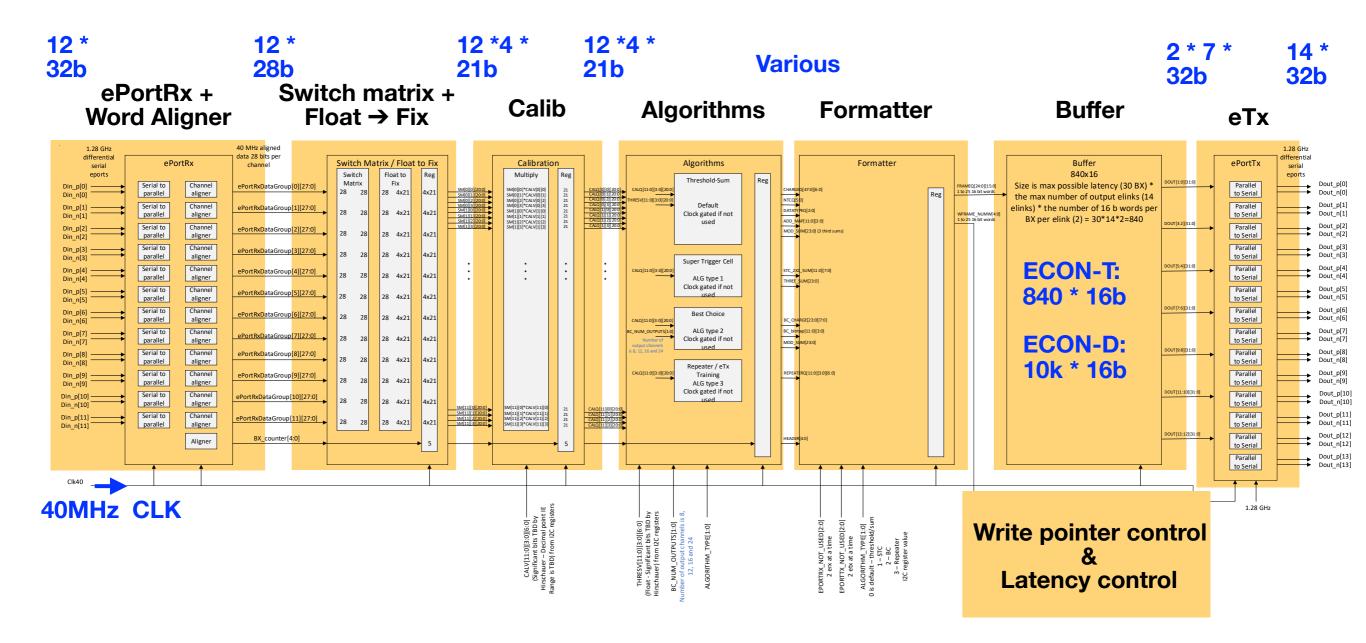

# **Basic ECON reqs/specs**

- Trigger data transmission at 40 MHz

- DAQ data transmission at 750 kHz

- 16 BX latency for TRG path

- Impacts maximum depth of buffers and architecture choices

- Radiation tolerance

- Use 65 nm TSMC process

- triple modular redundancy for registers and clocks

- standard cell libraries characterized for latest radiation corners

- extensive testing at prototype stage

- Low power

- Use 65 nm TSMC process

- Use power optimized design and algorithms

- Numbers of inputs/outputs

- 12 inputs (1.28 Gbps), 14 outputs (1.28 Gbps)

Charge #2

### ECON architecture choice Charge #2,8

ECON-related comments and recommendation from March 2019 CD-1 Director's Review (Dave Christian, Paul Derwent, Ping Gui):

#### **Comments**:

- ECON P1 consists of many analog, mixed signal and digital circuit blocks in a single chip with a BGA package with close-to-final pinout. Although some of the circuit blocks will be based on the existing ones in LpGBT as a starting point, it will still take much effort to understand the existing design, make necessary modifications, integrate, simulate and verify the performance. The design, verification and integration of all the blocks in a single chip takes large amount of manpower and coordination. The manpower of ASIC designers allocated to the project right now is barely minimal to complete the prototype I ASIC with the scheduled time period.

- Putting three channels of 10Gbps SCR+ENC+SER on a single chip not only increases the design complexity, but also introduces issues such as crosstalk and significantly increases the design risk.

- We are worried that, as currently envisioned, the first prototype of the ECON concentrator ASIC will take much longer to design than anticipated and will still have a significant risk of failure. We believe it would be safer to first design a prototype with 36 1.28 Gbps inputs and 7 1.28 Gbps outputs. This is the configuration required for ECON-D, and this configuration could also be used for ECON-T, albeit at the cost of a more complex printed circuit board design requiring more LpGBTs.

Recommendation: Consider the approach described above for the ECON ASICs to reduce schedule and performance risks.

#### • Summary :

- ECON (P1) is a complex chip composed of analog, mixed, and digital blocks.

- Person power for design and verification is barely sufficient.

- Including 3x 10Gbps transmitter greatly increases design complexity and risk.

- Consider design without 10Gbps transmitters.

- Based on this recommendation, extensive internal review, and comprehensive system optimization studies, we have simplified ECON plan without impacting physics performance.

- New ECON architecture:

- Inputs : 36x @ 1.28 Gbps → 12x @ 1.28 Gbps

- **Outputs** : 3x 10.24 Gbps → 14x\*\* @ 1.28 Gbps

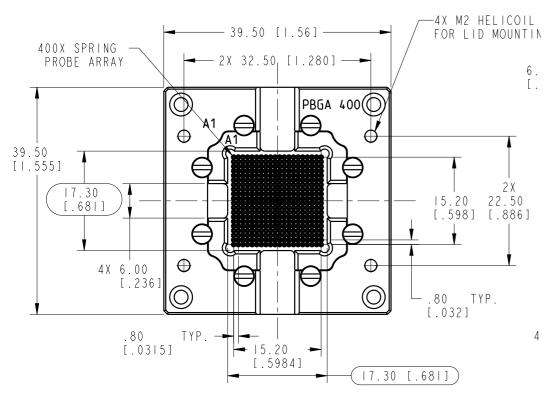

- **Package** : 18x18 Ball grid array  $\rightarrow$  176-pin thin quad flat package

- **Common pinout** for ECON-D and ECON-T

- Basic system idea : Use 1 ECON-T and 1 ECON-D per 8" module

\*\* >12 needed to accommodate data headers in case that all channels are readout without supression.

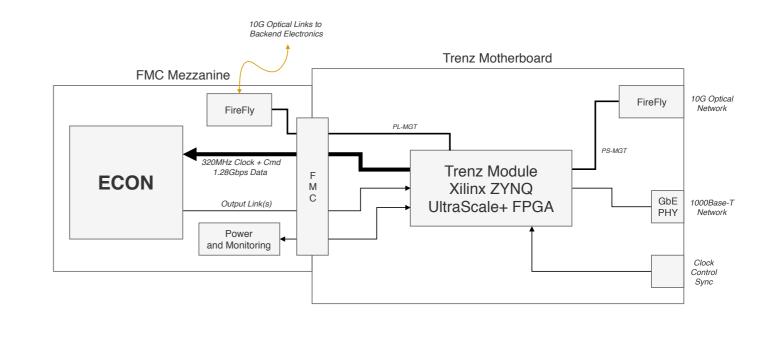

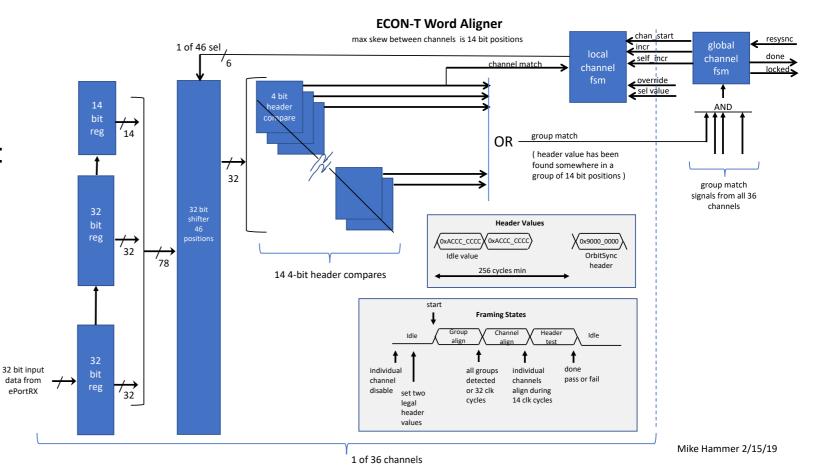

## **ECON-T** concept

- ECON-D inputs/outputs and architecture is the same, but RTL within each block differs.

- ePortRx + phase aligner from lpGBT

# ECON development plan

|                       |   |   |      |         |      | 201     | 19     |       |     |         |       |       |      |      |      |        |       | 20     | 20     |        |       |      |       |       |       |        |        |       |      | 202    | 21     |       |      |      |       |       |       | 2   | 022   |       |   |

|-----------------------|---|---|------|---------|------|---------|--------|-------|-----|---------|-------|-------|------|------|------|--------|-------|--------|--------|--------|-------|------|-------|-------|-------|--------|--------|-------|------|--------|--------|-------|------|------|-------|-------|-------|-----|-------|-------|---|

|                       | J | F | М    | Α       | Μ    | J       | J      | Α     | S   | 0       | Ν     | D     | J    | F    | М    | Α      | М     | J      | J      | Α      | S     | 0    | Ν     | D     | J     | F      | М      | Α     | М    | J      | J      | Α     | S    | 0    | Ν     | D     | J     | F   | Μ     | Α     | М |

| Receivers             |   |   | Desi | ign + l | mple | ement   | tation | 1     |     |         |       |       |      |      |      |        |       |        |        |        |       |      |       |       |       |        |        |       |      |        |        |       |      |      |       |       |       |     |       |       |   |

| Transmitters          |   |   | Desi | ign + l | mple | ement   | tation | า     |     |         |       |       |      |      |      |        |       |        |        |        |       |      |       |       |       |        |        |       |      |        |        |       |      |      |       |       |       |     |       |       |   |

| Control/Monitoring    |   |   | Desi | ign + l | mple | ement   | tation | า     |     |         |       |       |      |      |      |        |       |        |        |        |       |      |       |       |       |        |        |       |      |        |        |       |      |      |       |       |       |     |       |       |   |

| Algos / Data handling |   |   |      |         |      | Desig   | gn + I | Imple | mer | ntatior | ı     |       |      |      |      |        |       |        |        |        |       |      |       |       |       |        |        |       |      |        |        |       |      |      |       |       |       |     |       |       |   |

| Verification          |   |   |      |         |      | Verific | catio  | n     |     |         |       |       |      |      |      |        |       |        |        |        |       |      |       |       |       |        |        |       |      |        |        |       |      |      |       |       |       |     |       |       |   |

| Full chip assembly    |   |   |      |         |      |         |        |       |     |         | Integ | ratio | n    |      |      |        |       |        |        |        |       |      |       |       |       |        |        |       |      |        |        |       |      |      |       |       |       |     |       |       |   |

| ECON MPW              |   |   |      |         |      |         |        |       |     |         |       |       |      |      |      |        | Fab   |        |        | Pack   | age   | Radi | ation | / Bei | nch t | esting | g      |       |      |        |        |       |      |      |       |       |       |     |       |       |   |

| HGCROC                |   |   |      |         |      |         |        |       |     |         |       |       |      | Fab  |      |        | Pac   | kage   | Rad    | iation | / Ber | nch  |       |       |       | Syste  | em te  | est   |      |        |        |       |      |      |       |       |       |     |       |       |   |

| Adjust / finalize     |   |   |      |         |      |         |        |       |     |         |       |       |      |      |      |        |       |        |        |        |       |      |       |       |       | Desig  | gn +   | Imple | emen | tation | 1      |       |      |      |       |       |       |     |       |       |   |

| Verification          |   |   |      |         |      |         |        |       |     |         |       |       |      |      |      |        |       |        |        |        |       |      |       |       |       | Verifi | icatio | n     |      |        |        |       |      |      |       |       |       |     |       |       |   |

| ECON Production       |   |   |      |         |      |         |        |       |     |         |       |       |      |      |      |        |       |        |        |        |       |      |       |       |       |        |        |       |      | Fab    |        |       | Pack | kage | QC    |       |       |     |       |       |   |

| System testing        |   |   |      |         |      |         |        |       |     |         |       |       |      | Full | chip | verifi | catio | n con  | nplete | е      |       |      |       |       |       |        |        |       |      |        |        |       |      |      | Radia | ation | / sys | tem |       |       |   |

| Milestones            |   |   |      |         |      |         |        |       |     |         |       |       |      |      |      |        |       |        |        |        |       |      |       |       |       |        |        |       |      |        |        |       |      |      |       |       |       |     |       |       |   |

|                       |   |   |      |         |      |         |        |       |     |         | Rece  | iver  | comp | lete |      |        | Sub   | mit pr | rototy | /pe    |       |      |       |       | Prot  | otype  | com    | plete |      | Subm   | nit pr | roduc | tion |      |       |       |       | ECO | V cor | nplet | e |

|                       |   |   |      |         |      |         |        |       |     |         |       |       |      |      |      |        | ECC   | N re   | ady f  | or CE  | 0-2   |      |       |       |       |        |        |       |      |        |        |       |      |      |       |       |       |     |       |       |   |

- Initial plan (CD-1 Director's Review, March 2019) included two prototypes

- prototype 1 : verify complex 10.24 Gbps transmitters

- prototype 2 : verify whole chip

- With removal of 10.24 Gbps eTx, now planning single prototype for whole chip

- Second prototype included as risk with 50% probability

Charge #3

- Simplified ECON ASICs as much as possible without sacrificing physics performance.

- Use common architecture and pinout for ECON-D and ECON-T.

- ECON ASICs are almost 100% digitial

- Primary mixed-signal components taken from IpGBT

- Investment in top-end Cadence tools shifts resource needs from implementation  $\rightarrow$  RTL

- Verification is critical : capitalize on tools and extensive verification experience developed for DUNE ASICs.

- Modular design simplifies timing closure and interactions among the team.

- Parallelism of modular design allows large team to make simultaneous progress.

- Functionality built in to allow independent and easy testing of individual blocks.

- PRBS generator and comparator

- Scan chains for testing triplicated components

### Cost and schedule

J. Hirschauer | CE Concentrator -- DOE CD1 Review

Oct 23, 2019 18

### Schedule

|                                                                           | FY2022 FY2020 | FY2021                                             | FY2022                                         | FY2023                        | <b>■</b> /2021 | FY2022                                   | FY2023                    | FY2024                   |

|---------------------------------------------------------------------------|---------------|----------------------------------------------------|------------------------------------------------|-------------------------------|----------------|------------------------------------------|---------------------------|--------------------------|

| FQ1 FQ2 FQ3 FQ4 FQ1 FQ2 FQ3 FQ4 FQ1 FQ2 FQ3 FQ4 FQ1 F                     |               |                                                    |                                                | FQ1 FQ2 FQ3 FQ4               | FQ1 FQ2 FQ3 F  |                                          |                           | FQ1 FQ2 FQ3 FQ4 FQ       |

|                                                                           |               | sys p1:4 submit for fat                            |                                                |                               |                | ECE: ECON v1 : ven                       |                           |                          |

| 0% 📚 ECE - T5 - 1 ECON start<br>— ECE: ECON p1 : 1 transmitter simulation |               | Ň test sys p1:5 vendor<br>Ň p1:3 verification full |                                                |                               | -              | ECE: ECON v1 : ven<br>ECE: ECON v1: subm |                           | ea parts                 |

| ECE: ECON p1 : 1 receiver verilog                                         |               | k;p1:3 venincation rui<br>k;p1:4 full chip assemt  |                                                | -<br>-<br>                    |                | ECE: ECON V1: V                          |                           |                          |

| ECE: ECON test sys p1: 1 spec                                             |               | cpordinate with internat                           | -                                              | -<br>1<br>1                   |                |                                          | éndor delivers packag     | ed parts                 |

| ECE: ECON alg : basic trg algorithm development (PD1)                     |               | ECE: ECON p1 : HGRO                                |                                                | hasic test                    |                |                                          | test parts (first 25%) (F |                          |

| ECE: ECON alg : basic trg algorithm development (PD2)                     |               | N test sys p1:6 vendor                             |                                                |                               |                |                                          | test parts (first 25%) (G |                          |

| ECE: ECON alg : basic trg algorithm development (PD3)                     |               | ÉCON test sys v1 : 1 s                             |                                                | 1                             |                |                                          | test parts (first 25%) (G | 1                        |

| ECE: ECON test sys p1 : emulation design                                  |               | ÉCON p1 Full chip ver                              |                                                |                               |                | ECE: ECO                                 | N v1: system radiation    | test                     |

| ECE: ECON p1 : 2 control/monitoring verilog                               | ■ *_          | ÖN p1 : 3 verification f                           |                                                |                               |                | ECE: ECO                                 | Ń v1: test balance of p   | varts (PD)               |

| ECE: ECON p1 : 3 verification spec                                        | • •           | ÉCON p1 : 5 finalize foi                           |                                                |                               |                | ECE: ECO                                 | Ŋ v1: test balance of p   | parts (GS1)              |

| ECE: ECON p1 : 3 verification framework                                   |               | ÉCON p1 : submit for fa                            |                                                |                               | •              | ECE: ECO                                 | N v1: test balance of p   | parts (GS2)              |

| ECE: ECON p1 : 1 receiver simulation                                      | 📕 0% 📩 T5-E   | CE - Concentrator ASI                              | ;<br>C ready for CD2 (Tech                     | nical)                        |                | · · ·                                    | 1                         | ailable for PCB assembly |

| ECE: ECON p1 : 3 transmitter implementation                               | 📕 0% 📩 ECE -  | T5 - 4 ECON p1 : subr                              | nit                                            | -<br>-<br>-<br>-              | •              | 0% ᄎ ECE - T5 -                          | 9 ECON : complete         |                          |

| ECE: ECON test sys p1 ; emulation implementation                          | 1 <b>–</b>    | ÉCE: ECON p1 : vendo                               | þr fabs                                        | 1                             |                |                                          |                           |                          |

| ECE: ECON p1 : 3 control/monitoring implementation                        |               | ÉCE: ECON test sys v1                              | : 2 design                                     | 1                             |                |                                          |                           |                          |

| ÉCE: ECON test sys p1: 2 design                                           | -             | ECE: ECON test s                                   | ýs v1 : 3 layout                               | 1                             |                |                                          |                           |                          |

| ECE: ECON alg : final trg algorithm development (Pl                       | D1)           | ECE: ECON                                          | p1 : HGROC-DV2 inc                             | ,<br>prporate into sys rad to | est 🖉          |                                          |                           |                          |

| ECE: ECON alg : final trg algorithm development (Pl                       | D2) 📕         | ÉCE: ECON p1 : vendo                               | or delivers unpackage                          | d parts                       |                |                                          |                           |                          |

| ECE: ECON alg : final trg algorithm development (Pl                       | D3)           | ÉCE: ECON p1 : submi                               | t for packaging                                |                               |                |                                          |                           |                          |

| ECE: ECON p1 : 2 DAQ data handling verilog                                |               | ECE: ECON p1 : ver                                 | idor packages                                  |                               |                |                                          |                           |                          |

| ECE: ECON p1 : 2 TRG data handling verilog                                |               | <u>.                                    </u>       | ndor delivers package                          | d parts                       |                |                                          |                           |                          |

| 0% 💲 ECE - T5 - 1 ECON data handling start                                | •             | ECE: ECON p1 :                                     |                                                |                               |                |                                          |                           |                          |

| ECE: ECON p1 : 3 receiver implementation                                  |               |                                                    | p1 : radiation test                            |                               |                |                                          |                           |                          |

| ECE: ECON test sys p1 : emulation verification                            |               | ECE: ECON p1 :                                     |                                                | -<br> <br> <br>               |                |                                          |                           |                          |

| ECE: ECON p1 : 3 verification blocks                                      |               |                                                    | ys v1 : 4 submit for fab                       |                               |                |                                          |                           |                          |

| ECE: ECON p1 : 3 transmitter integration                                  | -             |                                                    | test sys v1 : 5 vendor                         | fabs                          |                |                                          |                           |                          |

| ECE: ECON test sys p1: 3 layout                                           | 2             | 0% \$ ECE - T5 - 5                                 |                                                | 1                             |                |                                          |                           |                          |

| ECE: ECON p1 : 3 TRG data handling imple                                  |               |                                                    | ECON v1 : verify desig                         |                               |                |                                          |                           |                          |

| ECE: ECON p1 : 3 DAQ data handling imple                                  | mentation     |                                                    | ECON v1 : adjust and                           |                               |                |                                          |                           |                          |

| ECE: ECON p1 : 3 receiver integration                                     |               | ; <u>u</u>                                         | p1 : system radiation                          |                               |                |                                          |                           |                          |

| ECE: ECON alg : develop SystemVerilog m                                   | -             |                                                    | test sys v1 : 6 vendor                         | -                             |                |                                          |                           |                          |

| 0% ᄎ ECE - T5 - ECON p1 Receiver integration comp                         | Diete         |                                                    | ECON v1 : submit for f<br>T4 - Final ECON subn |                               |                |                                          |                           |                          |

|                                                                           |               |                                                    | T5 - 8 ECON v1 : sub                           |                               |                |                                          |                           |                          |

|                                                                           |               | 0% <u>♦</u> ECE •                                  | 10-SECON VI : SUD                              | inic                          |                |                                          |                           |                          |

ECON interfaces to rest of project by supplying prototype and production ASICs for motherboard assembly → each connection occurs in RLS at appropriate milestone.

| Activity ID | Level | Activity                                             | Date        |

|-------------|-------|------------------------------------------------------|-------------|

| ES30037C1   | Т5    | Full chip verification complete                      | 20-Feb-2020 |

| ES30110     | Т5    | Submit ECON prototypes for fabrication               | 08-May-2020 |

| ES10280     | Т5    | ECON prototypes complete                             | 20-Jan-2021 |

| ES30120     | Т5    | Submit ECONs for production fabrication              | 20-May-2021 |

| ES10660     | Т5    | First 25% of production ECONs ready for PCB assembly | 22-Nov-2021 |

| ES19990     | Т5    | ECON complete                                        | 23-Feb-2022 |

### **Cost estimate**

| WBS                                                      | Direct M&S (\$) | Labor (Hours) | FTE    | Direct + Indirect + Esc.<br>(\$) | Estimate Uncertainty<br>(\$) | Total Cost (\$) |

|----------------------------------------------------------|-----------------|---------------|--------|----------------------------------|------------------------------|-----------------|

| DOE-CD1-402.4 402.4 CE - Calorimeter Endcap (at DOE CD1) | 21,051,786      | 332579        | 188.11 | 40,672,474                       | 10,143,585                   | 50,816,059      |

| DOE-CD1-402.4.2 CE - Management                          | 1,934,243       | 82022         | 46.39  | 3,807,266                        | 622,019                      | 4,429,285       |

| DOE-CD1-402.4.3 CE - Sensors                             | 7,501,635       | 14846         | 8.40   | 8,393,032                        | 1,722,630                    | 10,115,663      |

| DOE-CD1-402.4.4 CE - Modules                             | 2,932,730       | 96412         | 54.53  | 8,405,886                        | 1,435,046                    | 9,840,932       |

| DOE-CD1-402.4.5 CE - Cassettes                           | 3,677,813       | 47416         | 26.82  | 9,422,794                        | 3,065,143                    | 12,487,937      |

| DOE-CD1-402.4.6 CE - Scintillator Calorimetry            | 2,084,047       | 60875         | 34.43  | 4,196,710                        | 1,244,785                    | 5,441,494       |

| DOE-CD1-402.4.7 CE - Electronics and Services            | 2,921,318       | 31008         | 17.54  | 6,446,786                        | 2,053,962                    | 8,500,748       |

| DOE-CD1-402.4.7.1 CE - Concentrator ASIC                 | 1,516,100       | 27168         | 15.37  | 4,444,957                        | 1,471,236                    | 5,916,193       |

| DOE-CD1-402.4.7.2 CE - Power System                      | 1,405,218       | 3840          | 2.17   | 2,001,829                        | 582,726                      | 2,584,555       |

- Cost drivers (direct+indirect+esc):

- ECON production & prod. packaging (M&S) : \$0.752M + \$0.568M

- ECON design & verification (labor) : \$1.874M (prototypes + production)

- ECON testing (labor) : \$0.859M (prototypes + production)

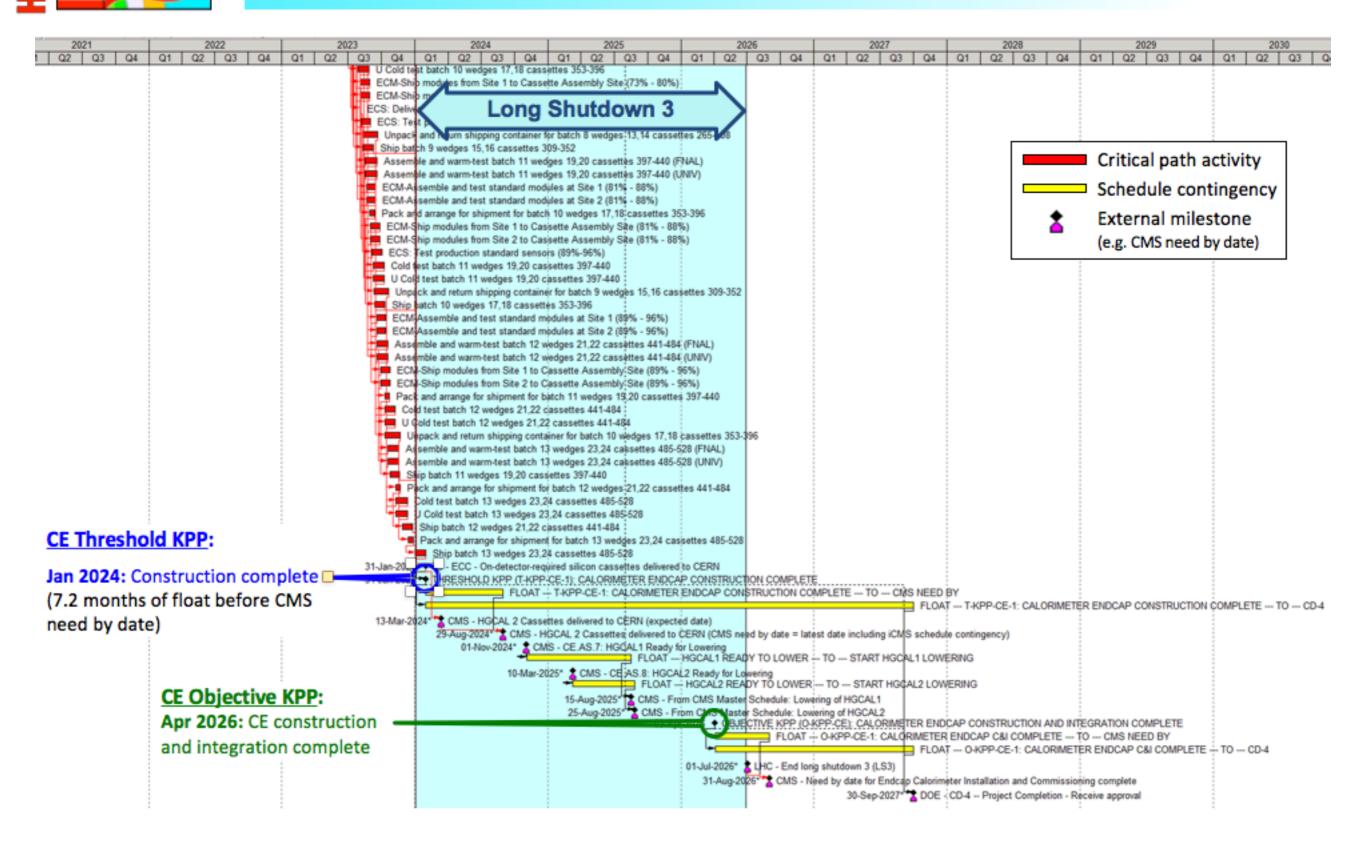

### Critical path and float

22

Charge #3

- 7 (2) month float for providing ECON prototype for scintillator (silicon) prototype motherboard verification.

- 3 (-1) month float for providing final ECON for scintillator (silicon) motherboard assembly.

- However, Motherboard Assembly has 4.5 months of float with respect to Cassette Assembly.

- 7.2 month total US project float

- Greatest schedule risk is need for another round of ASIC prototype :

- 7.5 month mean schedule impact

- More discussion at end of talk on how schedule can absorb ECON delays.

Charge #3

#### RT-402-4-18-D CE - Additional concentrator ASIC engineering (MPW) run is required

| Risk Rank:                       | 3 (High) Scores: Probability : 4 (H) ; Cost: 2 (M) Schedule: 3 (H))                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Risk Status:                                                                                                                                                                        | Open                                                                                                                                                                                                                                                                                                                        |

|----------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Summary:                         | Current planning includes the cost of two Multi-Project Wafer (MPW) prot<br>cycle may be required. This risk addresses the need an additional single ru                                                                                                                                                                                                                                                                                                                                                                                                                                              | 6                                                                                                                                                                                   | nt flaw is observed after the second run, a third                                                                                                                                                                                                                                                                           |

| Risk Type:                       | Threat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Owner:                                                                                                                                                                              | James F Hirschauer                                                                                                                                                                                                                                                                                                          |

| WBS:                             | 402.4 CE - Calorimeter Endcap                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Risk Area:                                                                                                                                                                          | Technical Risk / Quality                                                                                                                                                                                                                                                                                                    |

| Probability (P):                 | 50%                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>Technical Impact:</b>                                                                                                                                                            | 0 (N) - negligible technical impact                                                                                                                                                                                                                                                                                         |

| Cost Impact:                     | PDF = 3-point - triangular                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Schedule Impact:                                                                                                                                                                    | PDF = 3-point - triangular                                                                                                                                                                                                                                                                                                  |

|                                  | Minimum = $164 \text{ k}$ \$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                     | Minimum = 6.0 months                                                                                                                                                                                                                                                                                                        |

|                                  | Most likely = 241 k\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                     | Most likely = 7.50 months                                                                                                                                                                                                                                                                                                   |

|                                  | Maximum = $385 k$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                     | Maximum = 9.0 months                                                                                                                                                                                                                                                                                                        |

|                                  | Mean = 263.3 k\$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                     | Mean = 7.5 months                                                                                                                                                                                                                                                                                                           |

|                                  | P * <impact> = 132.0 k\$</impact>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                     | P * <impact> = 3.75 months</impact>                                                                                                                                                                                                                                                                                         |

|                                  | flaw is fairly easy to fix and the exact time needed depends on when when additional testing is assumed to be modest and covered by the labor inclue The min/likely/max cost is hence 164/209/295 k\$.                                                                                                                                                                                                                                                                                                                                                                                               | ded for ASIC testing in the                                                                                                                                                         | e baseline.                                                                                                                                                                                                                                                                                                                 |

|                                  | additional testing is assumed to be modest and covered by the labor inclue                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ded for ASIC testing in the                                                                                                                                                         | e baseline.                                                                                                                                                                                                                                                                                                                 |

| Cause or Trigger:                | additional testing is assumed to be modest and covered by the labor include<br>The min/likely/max cost is hence 164/209/295 k\$.<br>The L3 burn rate due to the delay of downstream activities is \$21k/month<br>cassette assembly is affected. therefore:<br>Min cost = \$164k + 0 = \$164k.<br>Likely cost = \$209k + 1.5 months * \$21k burn rate = \$241k.                                                                                                                                                                                                                                       | ded for ASIC testing in the                                                                                                                                                         | e baseline.<br>here are 6 months of float available before<br>JM: Implemented in P6 between 'ECON p2 tes                                                                                                                                                                                                                    |

| Cause or Trigger:<br>Start date: | additional testing is assumed to be modest and covered by the labor include<br>The min/likely/max cost is hence 164/209/295 k\$.<br>The L3 burn rate due to the delay of downstream activities is \$21k/month<br>cassette assembly is affected. therefore:<br>Min cost = \$164k + 0 = \$164k.<br>Likely cost = \$209k + 1.5 months * \$21k burn rate = \$241k.                                                                                                                                                                                                                                       | ded for ASIC testing in the                                                                                                                                                         | e baseline.<br>here are 6 months of float available before                                                                                                                                                                                                                                                                  |

| Start date:                      | additional testing is assumed to be modest and covered by the labor include<br>The min/likely/max cost is hence 164/209/295 k\$.<br>The L3 burn rate due to the delay of downstream activities is \$21k/month<br>cassette assembly is affected. therefore:<br>Min cost = \$164k + 0 = \$164k.<br>Likely cost = \$209k + 1.5 months * \$21k burn rate = \$241k.<br>Max cost = \$295k + 3 months * \$21k burn rate = \$385k.                                                                                                                                                                           | ded for ASIC testing in the<br>(CMS-doc-13481), but th<br>Impacted Activities:<br>End date:<br>eering (MPW) runs are su                                                             | e baseline.<br>here are 6 months of float available before<br>JM: Implemented in P6 between 'ECON p2 tes<br>parts' and 'ECON v1 finalize design'<br>30-Aug-2021<br>ifficient. We will be using some code blocks from                                                                                                        |

|                                  | additional testing is assumed to be modest and covered by the labor inclue<br>The min/likely/max cost is hence 164/209/295 k\$.<br>The L3 burn rate due to the delay of downstream activities is \$21k/month<br>cassette assembly is affected. therefore:<br>Min cost = \$164k + 0 = \$164k.<br>Likely cost = \$209k + 1.5 months * \$21k burn rate = \$241k.<br>Max cost = \$295k + 3 months * \$21k burn rate = \$385k.<br><u>31-Aug-2020</u><br>We will work closely with engineers to make sure that two planned engine<br>the lpGBT that would have undergone some testing before the two MPW r | ded for ASIC testing in the<br>(CMS-doc-13481), but the<br>Impacted Activities:<br>End date:<br>eering (MPW) runs are su<br>uns, and we will be include<br>educe the needed testing | e baseline.<br>here are 6 months of float available before<br>JM: Implemented in P6 between 'ECON p2 tes<br>parts' and 'ECON v1 finalize design'<br>30-Aug-2021<br>ifficient. We will be using some code blocks from<br>ding the prototype ECON ASIC in a major system<br>time. Accelerate or parallelize the production of |

Charge #3,7

#### **RT-402-4-04-D CE - Concentrator does not meet specifications**

| Risk Rank:             | 2 (Medium) Scores: Probability : 2 (L) ; Cost: 3 (H) Schedule: 3 (H))                                                                                                                                                                                                                                                                                                                               | Risk Status:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Open                                                                                                                                         |

|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|

| Summary:               | If the concentrator ASIC does not meet specifications after the production<br>produced and additional engineering effort is required to adjust the design<br>how many engineering/multi-project wafer runs are done and tested befor<br>the design (progress made), and on the schedule, e.g. if all irradiation tests<br>packaging costs are realized only once since we would find the problem be | n so that the ASIC meet sp<br>ore the production masks a<br>s can be done before the p                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ecifications. The risk probability depends on<br>are produced, and also on the exact maturity of<br>roduction masks are fabricated. The full |

| Risk Type:             | Threat                                                                                                                                                                                                                                                                                                                                                                                              | Owner:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | James F Hirschauer                                                                                                                           |

| WBS:                   | 402.4 CE - Calorimeter Endcap                                                                                                                                                                                                                                                                                                                                                                       | Risk Area:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Technical Risk / Requirements                                                                                                                |

| Probability (P):       | 10%                                                                                                                                                                                                                                                                                                                                                                                                 | Technical Impact:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2 (M) - significantly substandard                                                                                                            |

| Cost Impact:           | PDF = 3-point - triangular                                                                                                                                                                                                                                                                                                                                                                          | Schedule Impact:                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | PDF = 3-point - triangular                                                                                                                   |

| cost impact.           | Minimum = 907  k                                                                                                                                                                                                                                                                                                                                                                                    | Seneral mpace                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Minimum = 6.0 months                                                                                                                         |

|                        | Most likely $= 971 \text{ k}$ \$                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Most likely = 7.50 months                                                                                                                    |

|                        | Maximum = $1,035 \text{ k}$ \$                                                                                                                                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Maximum = 9.0 months                                                                                                                         |