# B02 - Trigger algorithm development, performance, and demonstration

Nhan Tran HL LHC CMS CD-1 Review October 22-24, 2019

## **Technical design**

- Algorithms overview and physics performance

- Algorithm design

- Firmware demonstration

### **Management aspects**

Risk, quality assurance Milestones and progress *Cost and schedule (see talk later by Jeff)*

### Nhan Tran

### Wilson Fellow (Fermilab)

- L3 Manager: Correlator trigger

- Development of Particle Flow and PUPPI in L1 trigger

- Lead on hls4ml: high level synthesis for machine learning

### Postdoc (Fermilab)

Track trigger ASIC development and testing for Vertically Integrated Pattern Recognition Associative Memory (VIPRAM)

**Development of PUPPI algorithm**

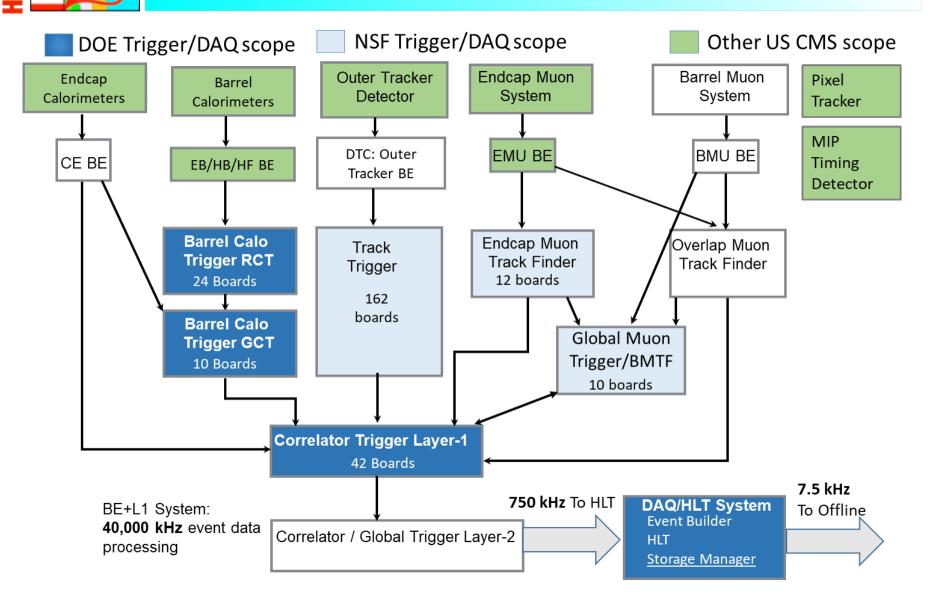

# **Trigger Scope Overview**

#### Maintain performant trigger under high luminosity conditions

Upgrade L1 trigger accept rate: 750 kHz Upgrade L1 trigger total latency: 12.5 µs

#### **Detector/Trigger Upgrades**

Tracking trigger for tracks with pT > 2 GeV

New high granularity endcap calorimeter

Full crystal readout of barrel ECal

New muon detectors for improved high  $\eta$  coverage and higher granularity readout

### **DOE trigger scope**

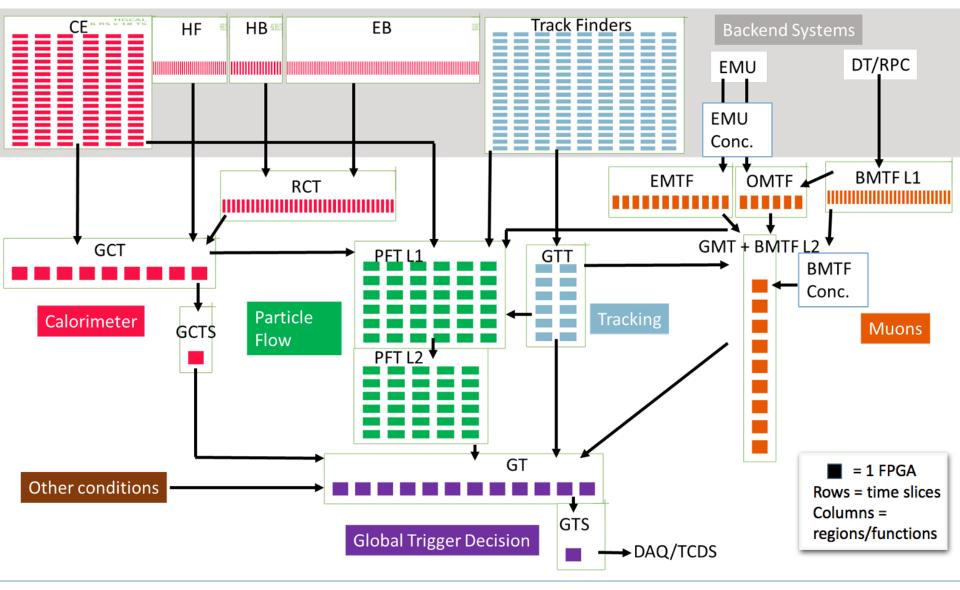

402.6.3: Calorimeter (regional barrel and forward calorimeter, global) 402.6.5: Correlator trigger (combining muon, calorimeter, tracker inputs)

Deliver a suite of algorithms which cover both **robustness** and **optimized physics performance**

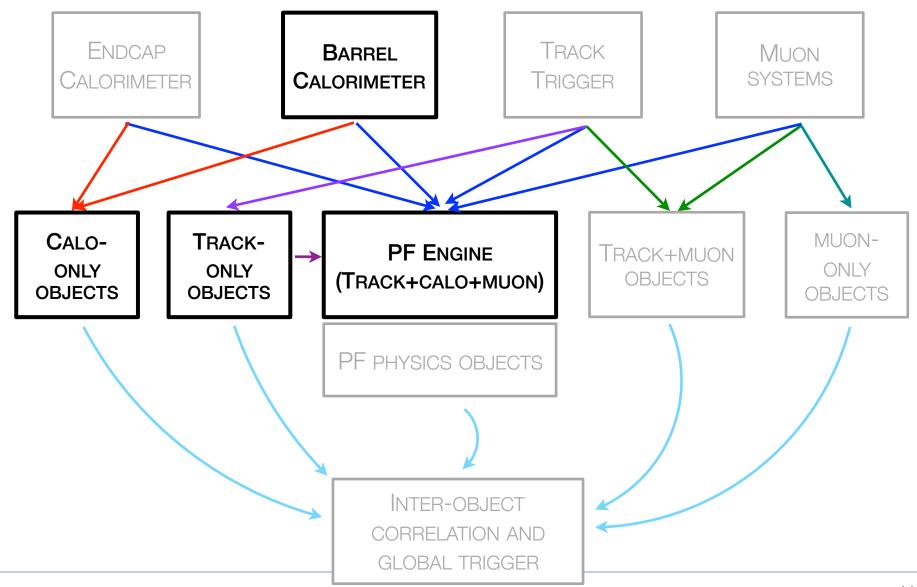

### Single system triggers\*

Robust, simpler algorithms Global Calorimeter Trigger objects Track-only Trigger objects \* muon system only triggers in NSF scope

### Multi-system optimized reconstruction

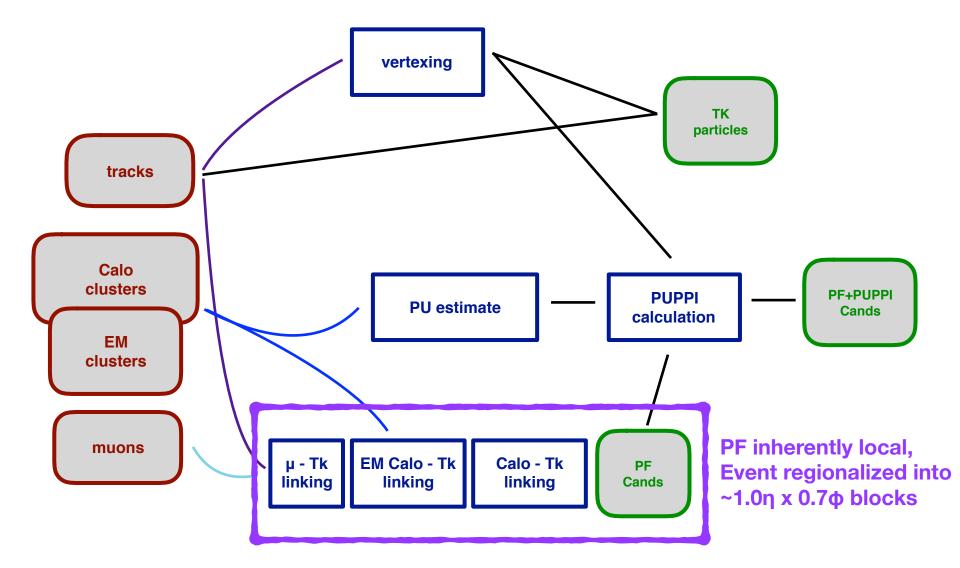

More complex, performant algorithms Track + muon + calorimeter correlated (particle flow and PUPPI) trigger objects

Devise algorithms and study physics performance for the correlator (Particle Flow) and calorimeter triggers

Implement and integrate algorithms into firmware Within latency, bandwidth, and resource requirements

From *robust*, single-system algorithms to *optimized* multi-system algorithms

- Calorimeter and Track-only objects

- Particle Flow with PUPPI

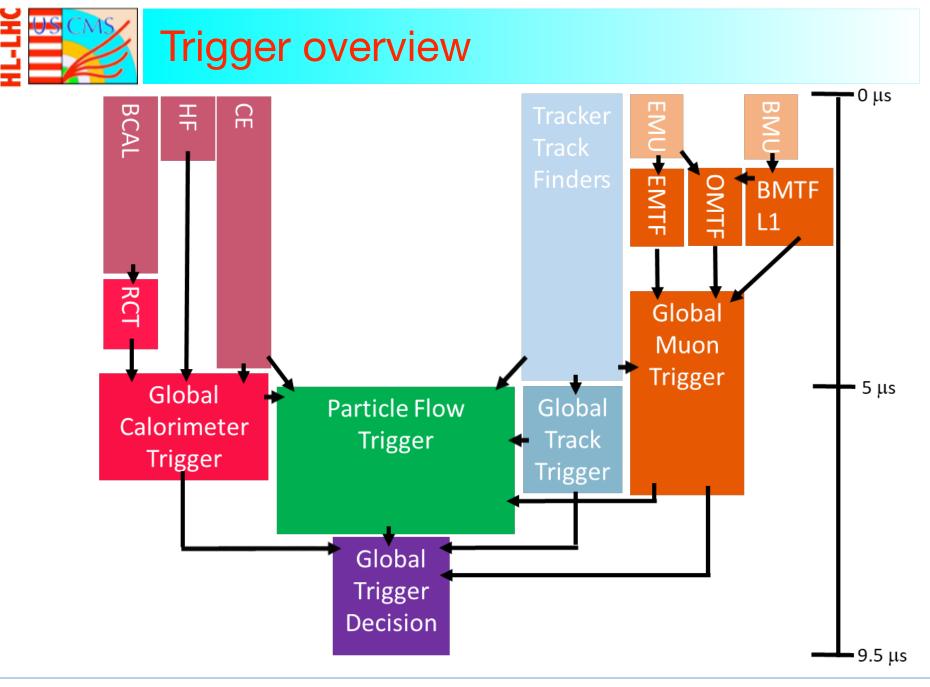

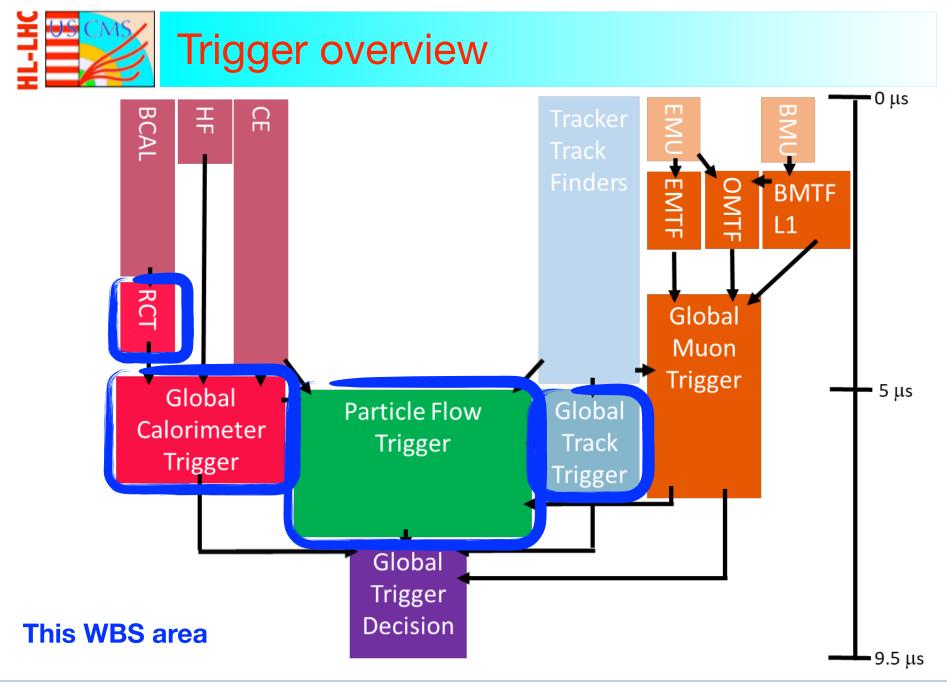

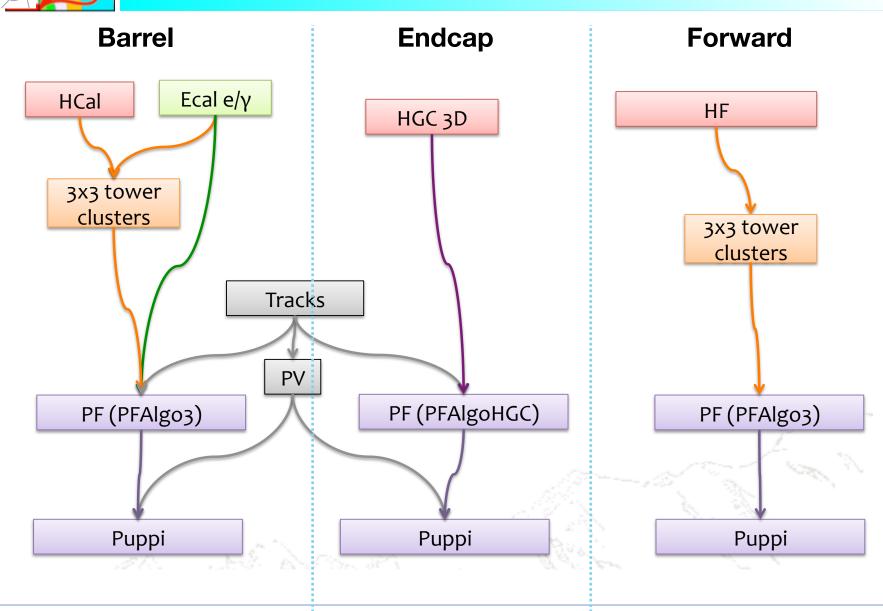

# Functional algorithm diagram

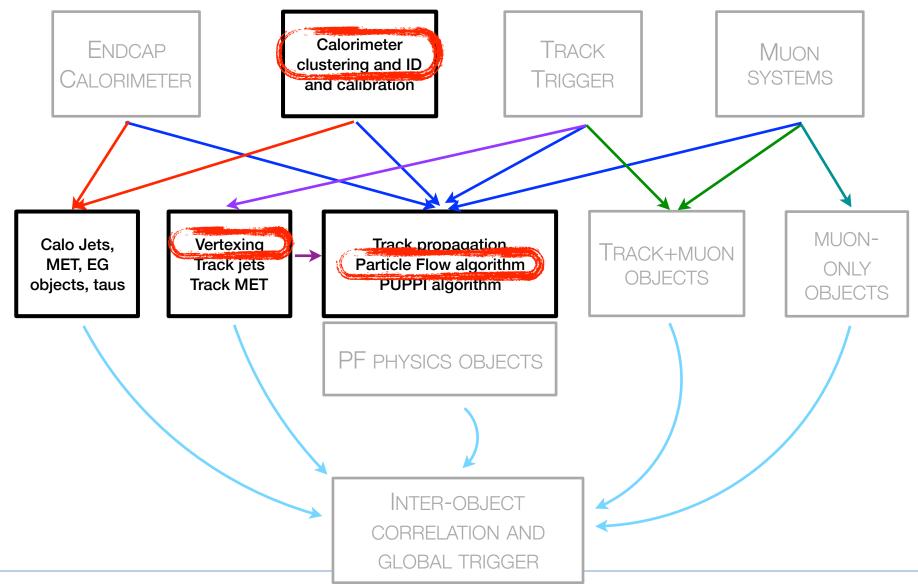

# Functional algorithm diagram

### **Steps of algorithm development path:**

- Understand physics case

- Define algorithm and interfaces (inputs & downstream) Develop firmware, estimate latency and resources Integrate within full trigger architecture Demonstrate full implementation feasibility

- n.b. difficult to present all steps for all algorithms

- 1) Calorimeter clustering example

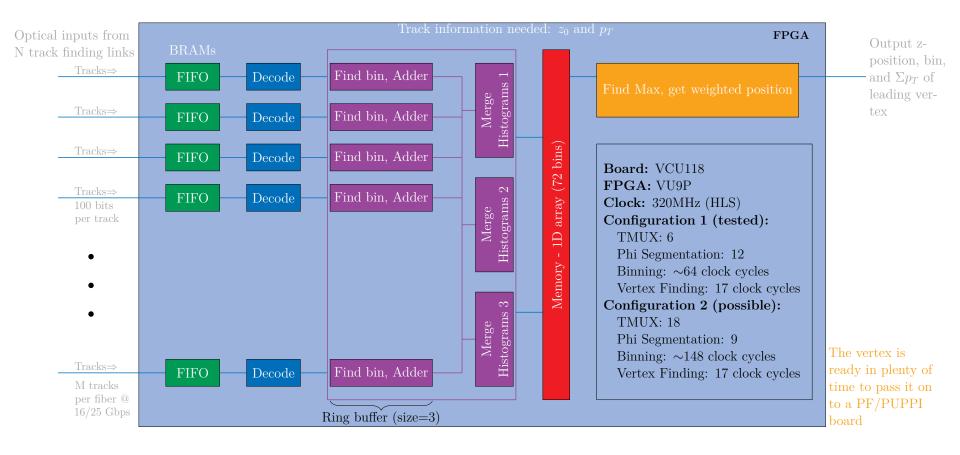

- 2) Vertexing example

- 2) **Particle flow** example larger focus, most complex in terms of algorithm size and input interfaces

# A note on algorithm development

FPGA development of algorithms in languages like VHDL or Verilog (RTL) have long development cycles and require a lot of engineering support

### New tools: HLS, high level synthesis

C-level programming with specialized preprocessor directives which synthesizes optimized firmware

### **Particle flow example:**

Core first version of firmware developed in 2-3 months using HLS, only physicists

Engineering firmware support still required (of course!) — our experience: system interfaces, infrastructure, and signal routing, etc.

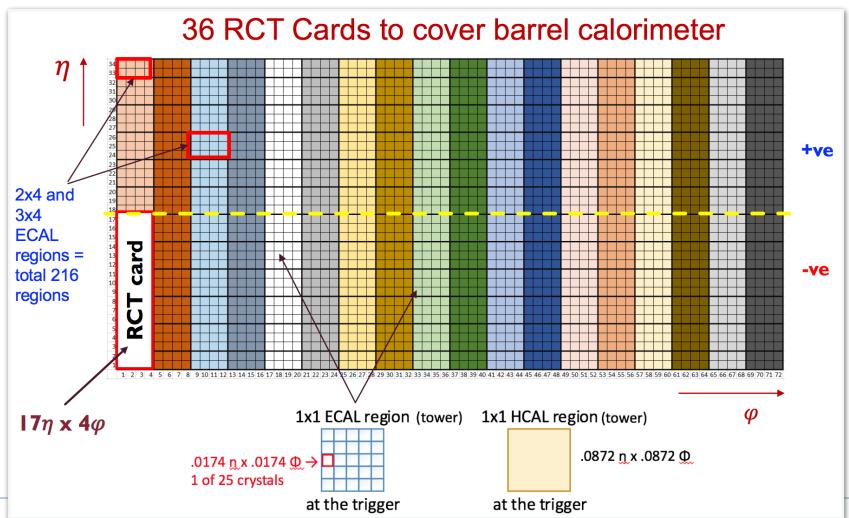

Barrel **Regional Calorimeter Trigger** takes as input single ECal crystals and HCal towers to build clusters

# **Calorimeter clustering**

- Input: 17x4x5x5 ECAL crystals and 16x4 HCAL towers.

- > 1-RCT card covers  $17\eta \ge 4\varphi$  towers

- > Divide card in regions of  $3\eta \ge 4\varphi$  towers to make clusters.

- > Building clusters in  $3\eta \ge 4\varphi$  region:

- Search for seed crystal > 1 GeV

- Make 3x5 clusters at crystal level

- $\circ$  Select maximum of 5 highest ET cluster in  $3\eta \ge 4\varphi$  region

- Move to next 3x4 towers and then do the merging around the neighbors if cluster is at the boundary of the tower

- > For 1-RCT card, there are  $5 (3\eta \times 4\varphi)$  regions = 30 clusters

- Sort and send a maximum of 12 highest ET clusters

- To these 12 highest ET clusters, if there is a HCAL tower behind the ECAL tower, HCAL ET is also added to the cluster.

- Output: 12 Clusters (ECAL + HCAL)

### First Barrel RCT algorithm has reasonable resource usage and latency of 40 clock cycles @ 240 MHz for large resource FPGA (VU9P)

Two 17x2 blocks split across SLRs for better floor planning

# Candidate for smaller form factor FPGA

#### Xilinx VU9P, 240 MHz

| = Utilization Est | 360 MH    | 1Z      |         |         |      |

|-------------------|-----------|---------|---------|---------|------|

| Summary:          | ++        | +       | +       |         |      |

| Name              | BRAM_18K  | DSP48E  | FF      | LUT     | URAM |

| <br>DSP           | -         | +<br> - |         |         | _    |

| Expression        | -         | -1      | 0       | 504     | -    |

| FIFO              | -         | -1      | -       | -       | -    |

| Instance          | 0         | -1      | 46529   | 35250   | -    |

| Memory            | -         | -1      | -       | -       | -    |

| Multiplexer       |           | -1      | -       | 8106    | -    |

| Register          | 0         | -1      | 32007   | 7680    | -    |

| Total             | 0         | 0       | 78536   | 51540   | 0    |

| Available         | 4320      | 6840    | 2364480 | 1182240 | 960  |

| Utilization (%)   | ++<br>  0 | +       | 3       | 4       | 0    |

Similar resource utilization for clock @ 240 MHz

# Vertexing can be done in parallel to particle flow but is needed for pileup mitigation techniques

First "fast histogramming" algorithms implemented as a baseline

Algorithm implemented in HLS with VHDL wrapper to support feeding in tracks and reading out results

| VU9P                      |         | FF             | LUT                   |                           | BRAM                                      |       | DSP   |                                       |

|---------------------------|---------|----------------|-----------------------|---------------------------|-------------------------------------------|-------|-------|---------------------------------------|

| Vertexin                  | ng      | 117735         |                       | 154979                    |                                           | 1     |       | 1                                     |

| Availabl                  | е       | 2364480        |                       | 1182240                   |                                           | 2160  |       | 6840                                  |

| % used                    |         | 5              |                       | 13                        |                                           | 0     |       | 0                                     |

| rst track<br>arrives<br>0 | Buffer- | I<br>⊦Addition | Last track<br>arrives | is do<br>histogr<br>Merge | $pT sum$ $pne \Rightarrow$ $am in Z$ $48$ | Verte | exing | Vertex<br>position<br>is found<br>166 |

|                           |         | 110            |                       | 38                        | ~                                         | 17+   | 1     |                                       |

Algorithm finished in time to pass to PF+PUPPI

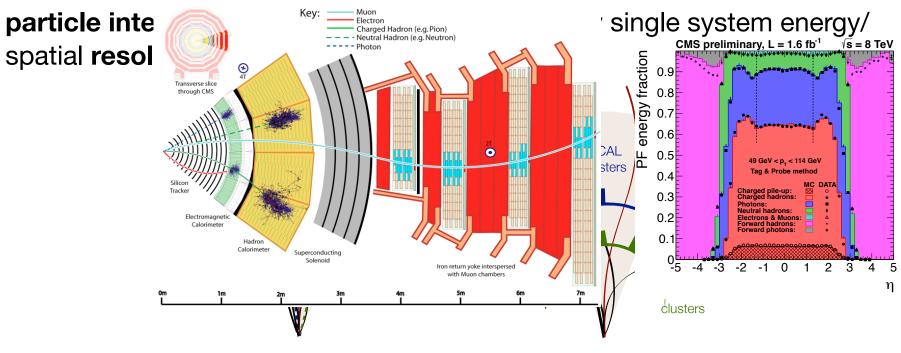

Use inspiration from offline reconstruction for best performance **Particle Flow:**

efficient combination of complementary detector subsystems

| Detector | p <sub>T</sub> -resolution               | η/Φ-segmentation                  |  |

|----------|------------------------------------------|-----------------------------------|--|

| Tracker  | 0.6% (0.2 GeV) – 5% (500 GeV)            | 0.002 x 0.003 (first pixel layer) |  |

| ECAL     | 1% (20 GeV) – 0.4% (500 GeV)             | 0.017 x 0.017 (barrel)            |  |

| HCAL     | 30% (30 GeV) – <mark>5%</mark> (500 GeV) | 0.087 x 0.087 (barrel)            |  |

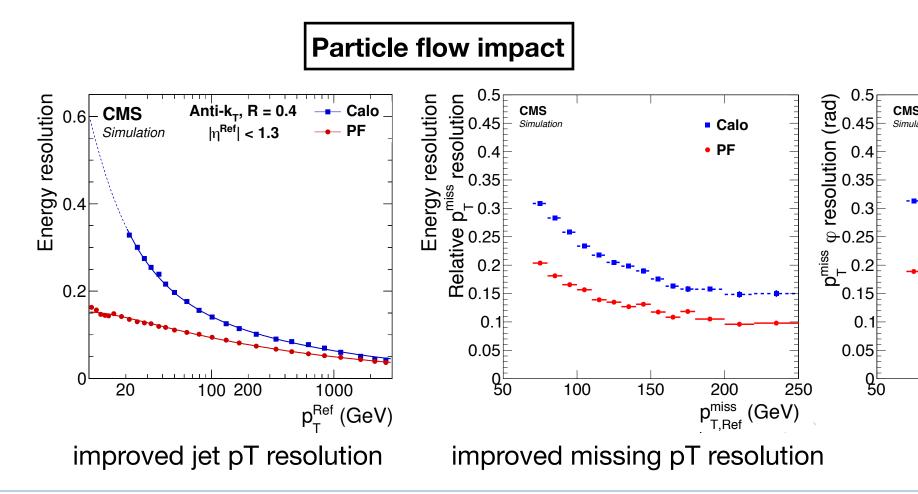

## Large gains from PF on jet and MET resolutions

arXiv:1706.04965 [PF paper]

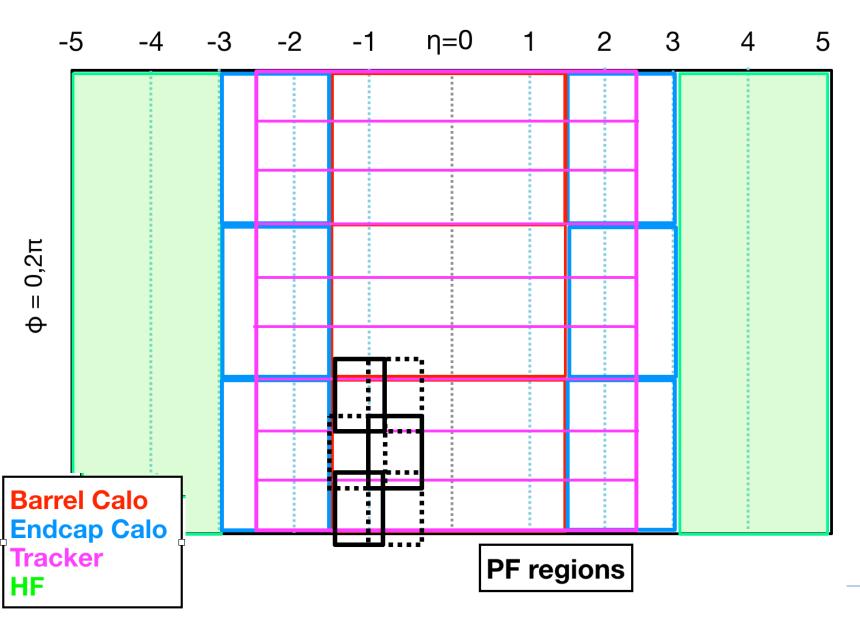

# Particle flow regions

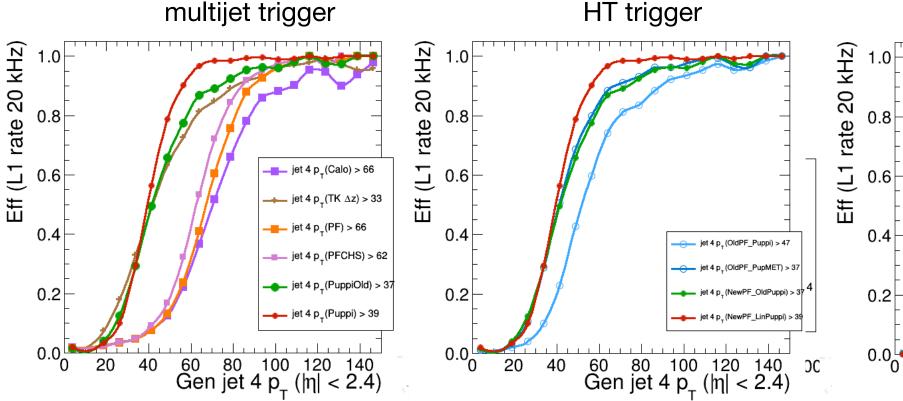

# Jet and MET performance

objects

Continual improvements to algorithms

Jet algorithms still offline style, work in progress

## Input definitions

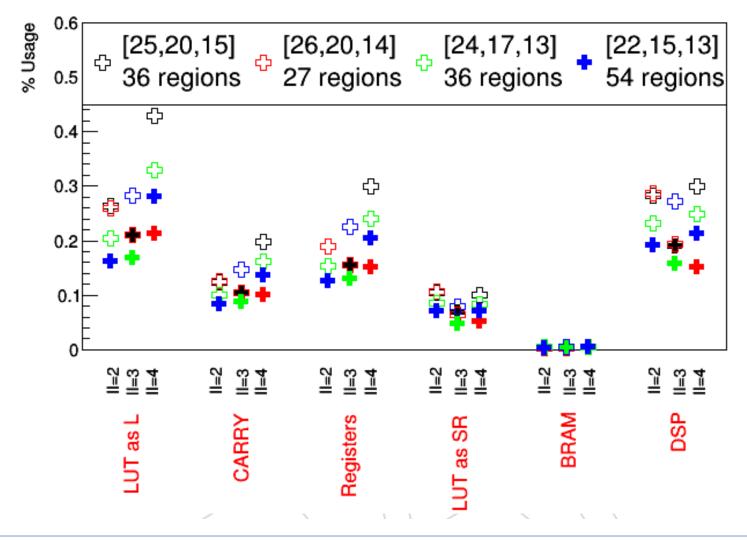

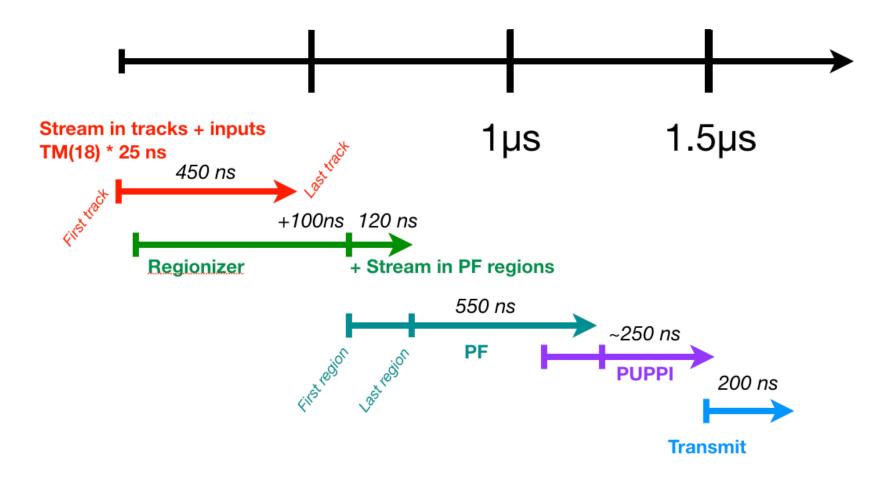

#### Implementation, VU9P, 240 MHz, 18 FPGAs (barrel)

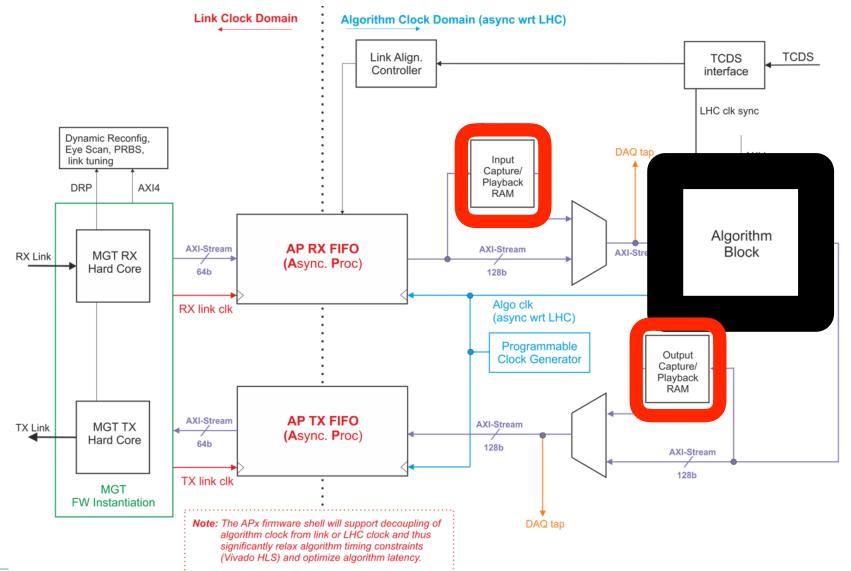

# Architecture (Exploded View)

(More in Sridhara's talk)

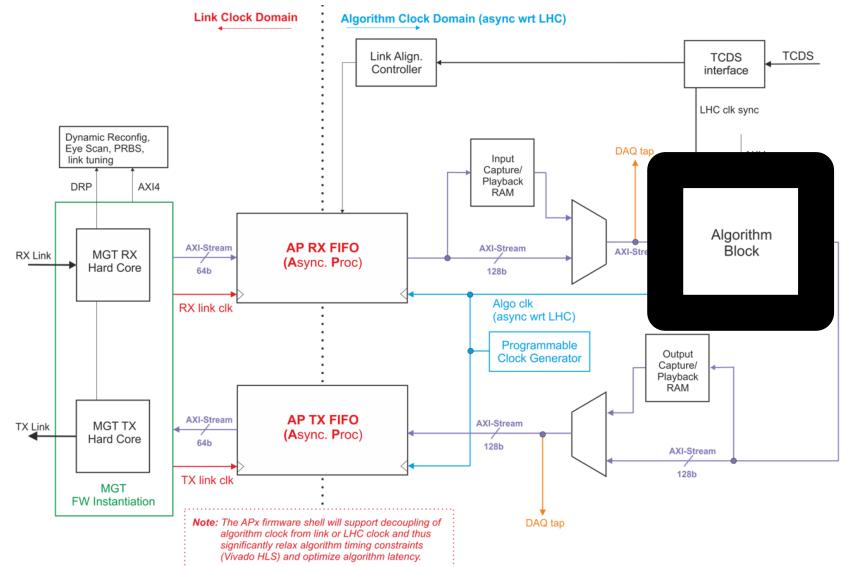

- Gen-0 (in operation at UW and CERN)

- CTP7-based (3 cards, 96 total active links @ 10.0G available)

- HLS interface grafted onto Phase 1 8b10b link infrastructure

- 64-bit link interfaces

- Gen-1 (in operation at UW)

- APd1 single card setup

- Iridis-style 64b66b transport

- Early APx shell functionality

- Asynchronous processing clock

- Gen-2 (underway)

- Multicard test setup

- Iridis-style signaling and APx shell environment

- Common emulated TCDS timebase in ATCA/MicroTCA crates using CTP7

## **Demonstration**

## **Demonstration**

# **Bitwise simulation**

| Name                       | Value                                   |    | 1,430            | ns            | 1,440 ns | 5          | 1,450 ns  | 1,460 ns          | 1,470_ns 1,48           |

|----------------------------|-----------------------------------------|----|------------------|---------------|----------|------------|-----------|-------------------|-------------------------|

| V 🖬 link_object_in         | 39b,008,0,0,000,0007                    | 0) | (39b, <b>0</b> 0 | з 🛛 06        | d,04d    | (          | 000,000,0 | , 0, 000, 0000, 0 | 00, (2, 9, 18) , 214748 |

| > 👹 .phi[9:0]              | -101                                    | 0  | -10              | - X           | 109      | < <u> </u> |           |                   | 0                       |

| > 👹.eta[9:0]               | 8                                       | 0  | ( 8              |               | 77       | < <u> </u> |           |                   | 0                       |

| 🕌 .quality                 | 0                                       |    |                  |               |          |            |           |                   |                         |

| 🕌 .lsEM                    | 0                                       |    |                  |               |          |            |           |                   |                         |

| > 👹.z0[9:0]                | 0                                       |    |                  |               |          |            |           | e                 |                         |

| > 👹 .otherPt[15:0]         | 7                                       | 0  | $\leftarrow$     | 7             |          | < <u> </u> |           |                   | 0                       |

| > 👹.pt[15:0]               | 76                                      | 0  | 876              | · · · · · X • | 8        |            |           |                   | ©                       |

| > Washington .small_region | 2,9,18                                  |    | <u> </u>         | 0-            | C        | )          |           | 2,9,18            |                         |

| 🕌 .source_fiber            | 0                                       | 2) | $\leftarrow$     | Θ             |          |            |           |                   | 2147483647              |

| isource_event_index        | 0                                       | 2) | $\leftarrow$     | Θ             |          |            |           |                   | 2147483647              |

| > # din[63:0]              | 000e6c080007004c                        | 0) | 000e6c           | ∍X00          | э́1Ь44   |            |           | 000               | 00000000000000          |

| ₩ wr_en                    | 1                                       |    |                  |               |          |            |           |                   |                         |

| ₩ rd_en                    | 0                                       |    |                  |               |          |            |           |                   |                         |

| > 🖬 dout[63:0]             | 000000000000000000000000000000000000000 |    |                  | 00000000      | 00000000 |            | X         |                   | 000e6c080007004c        |

| ₩ full                     | 0                                       |    |                  |               |          |            |           |                   |                         |

| 🕌 almost_full              | 0                                       |    |                  |               |          |            |           |                   |                         |

| 🖟 empty                    | 1                                       |    |                  |               |          |            |           |                   |                         |

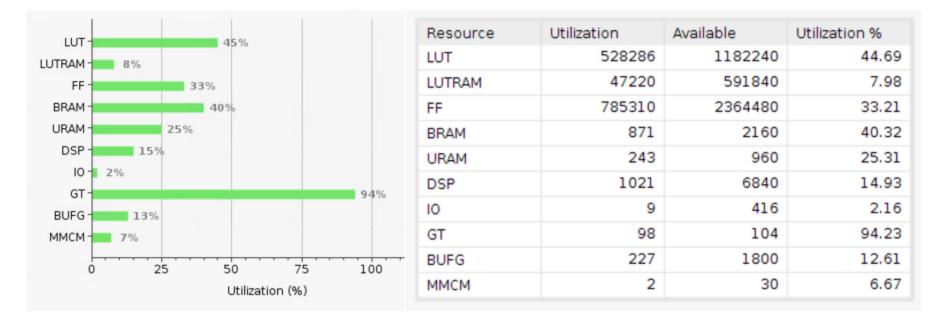

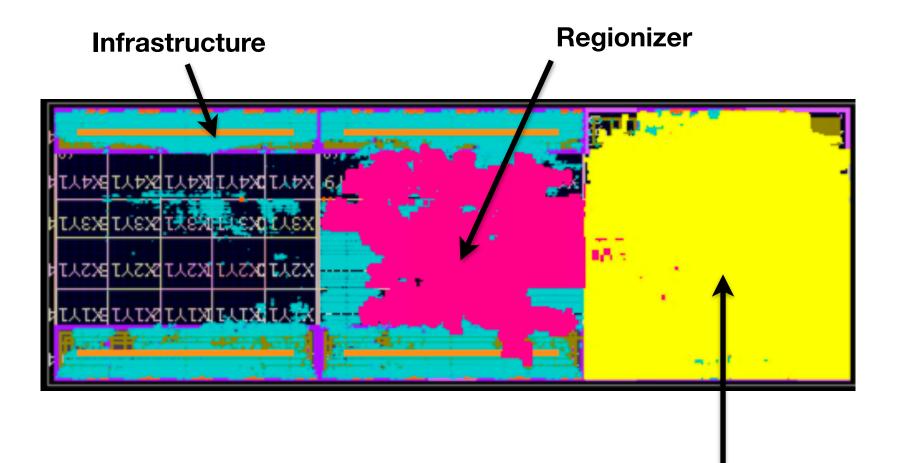

Utilization within project requirements Less than 50% (70%) for algorithm (total) firmware Recent milestone: all elements integrated and meeting timing with full place & route

## **Demonstration**

**Particle Flow and PUPPI**

# Summary of algorithm status

|             | baseline algo | firmware |

|-------------|---------------|----------|

| Clustering  |               |          |

| ID          |               |          |

| Calibration |               |          |

| Track prop  |               |          |

| PF block    |               |          |

| Vertexing   |               |          |

| PUPPI       |               |          |

| trk jet     |               |          |

| τ's         |               |          |

| calo e/γ    |               |          |

Suite of algorithms to meet physics needs (menu) demonstrated

Firmware for most resource intensive algorithms within system requirements to meet mission need

## Achieved

- Full simulation framework for studying algorithm physics performance

- Algorithm development with High Level Synthesis (HLS) tools and bitwise validation of firmware/software

- Integration of HLS IP blocks into firmware infrastructure in multiple modes (direct to infra, through intermediate VHDL)

## **Needed before production**

Final specification of algorithm interfaces for board-to-board communication (with USCMS and iCMS technologies)

## **Contributing institutions**

- Clustering and ID: UW

- Calibration: MIT, Fermilab, UIC

- Track propagation: TAMU

- Muon-track correlation: UCLA, UF, TAMU, Fermilab

- Vertexing and track-based objects: CU Boulder, Rutgers

- Particle Flow and PUPPI: MIT, Fermilab, UIC

- Calo-based objects: UW

## **Risk register**

| Threat | RT-402-6-02-D | TD - Board or parts vendor non-performance (DOE)            |

|--------|---------------|-------------------------------------------------------------|

| Threat | RT-402-6-03-D | TD - I/O performance does not meet requirements (DOE)       |

| Threat | RT-402-6-04-D | TD - Additional board redesign is required (DOE)            |

| Threat | RT-402-6-05-D | TD - Additional firmware development is required (DOE)      |

| Threat | RT-402-6-06-D | TD - Baseline FPGA does not satisfy requirements (DOE)      |

| Threat | RT-402-6-90-D | TD - Key Trigger or DAQ personnel need to be replaced (DOE) |

| Threat | RT-402-6-91-D | TD - Shortfall in Trigger or DAQ scientific labor (DOE)     |

RT-402-6-05: Risk Rank = Medium, firmware does not meet technical specifications Probability: 20%, Impact: \$10-60k Mitigation: allocate more time to on-project engineering, or new hire RT-402-6-90: Risk Rank = Low, due to lack of base funding Probability: 30%, Impact: \$0-292k Mitigation: replace with costed labor, other USCMS or iCMS institutions

Quality assurance plan (<u>cms-doc-13093,cms-doc-13318</u>) Flows down from the engineering requirements Acceptance plans based on QC activities For algorithms, basic requirements on resource and latency met with each firmware release Important: SW and FW stored and maintained in repositories

| TD-QC-004 | Design<br>Verification and<br>Measurement/<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>Testing<br>T | 50%) of activities that verify that the firmware fits within the chin |

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------|

As with entire project, we follow the Integrated Safety Management Plan (<u>cms-doc-13395</u>) and have documented our hazards in the preliminary Hazard Awareness Report (<u>cms-doc-13394</u>)

# Algorithm performance and firmware have progressed since 2018 CD1

Algorithms for: barrel calorimeter trigger, global calorimeter trigger, correlator (including vertexing, track-based objects)

# Full demonstration system for algorithm firmware progressing

First demonstration performed

## In sync with iCMS milestones for TDR in 2019