## DUNE FE ASIC Cold Studies: Ledge Threshold

Dan Douglas, Twymun Safford, Dean Shooltz Kendall Mahn, Carl Bromberg

> MICHIGAN STATE UNIVERSITY

#### What is the ledge effect?

After receiving large pulses, the ASIC tends to "lock up"

Scales with input charge

RMS noise decreases

## Instigating the Ledge

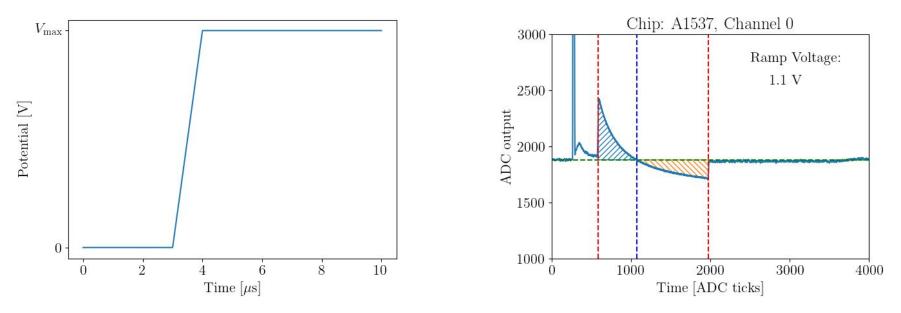

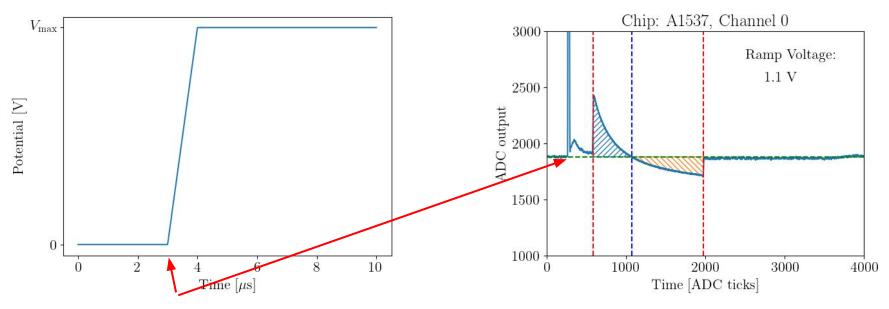

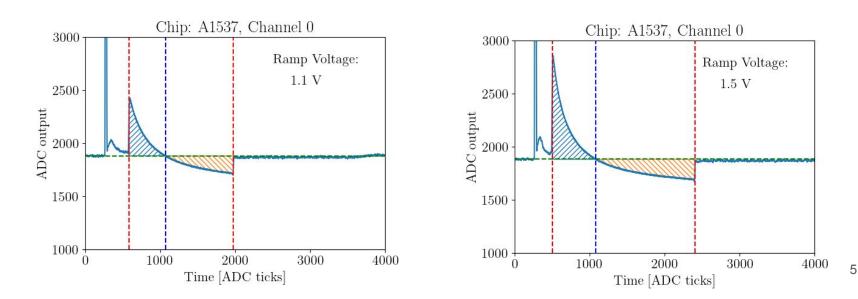

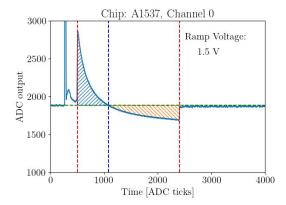

We use an arbitrary waveform generator to make a 1µs voltage ramp.

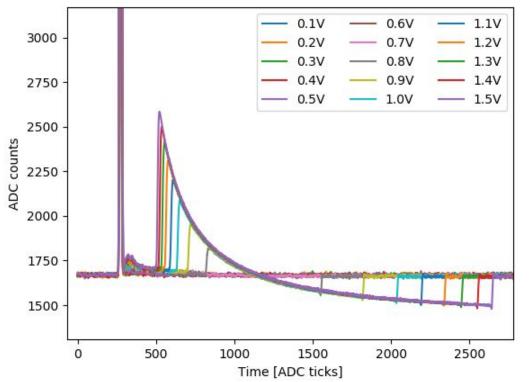

We scan through voltages ( $0.1V \rightarrow 1.5V$ ) and record the waveform.

## Instigating the Ledge

We use an arbitrary waveform generator to make a 1µs voltage ramp.

We scan through voltages (0.1V  $\rightarrow$  1.5V) and record the waveform.

Waveform readout is synchronized with pulser.

#### • Scaling in time (start, stop & duration)

- Scaling in magnitude

- Scaling in area

ASTER

6

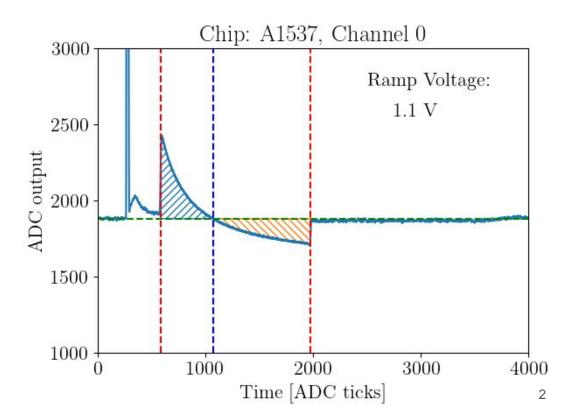

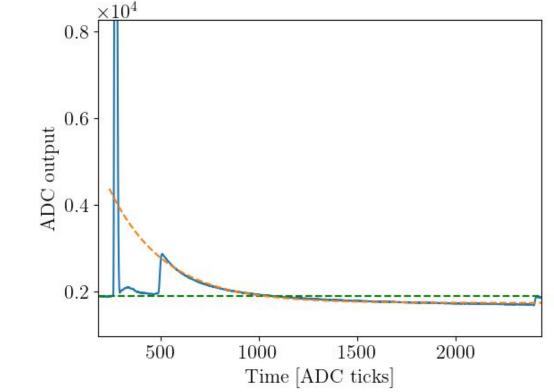

Ledges follow the same shape (exponential decay from peak?)

Only start/stop times change based on input charge.

Fitting an exponential yields a poor match.

Some other kind of decay from the peak?

Find peaks and zero crossing

Ledge

Area Under

Calculate area (in ticks × counts)

Fit to quadratics (force them to have the same zero crossing)

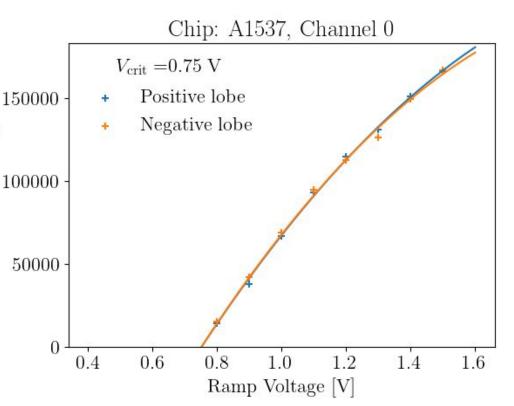

## Finding V<sub>crit</sub> (continued)

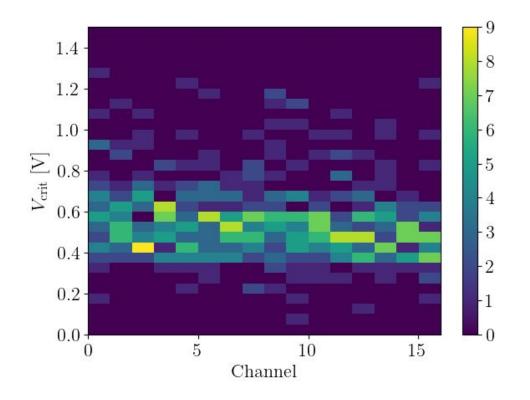

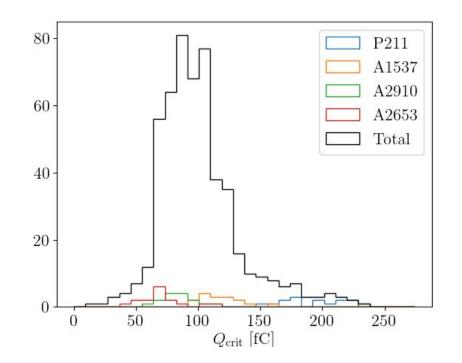

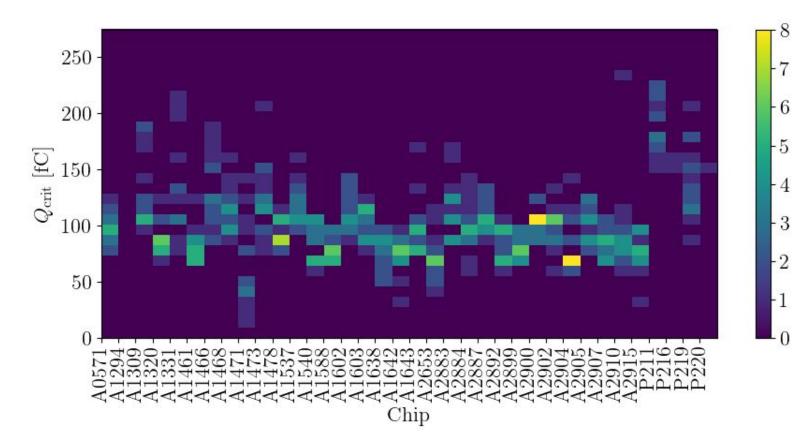

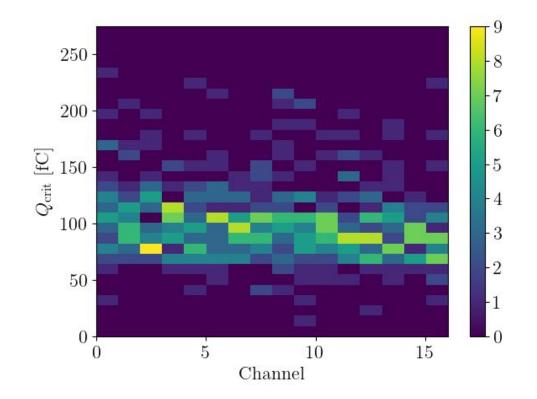

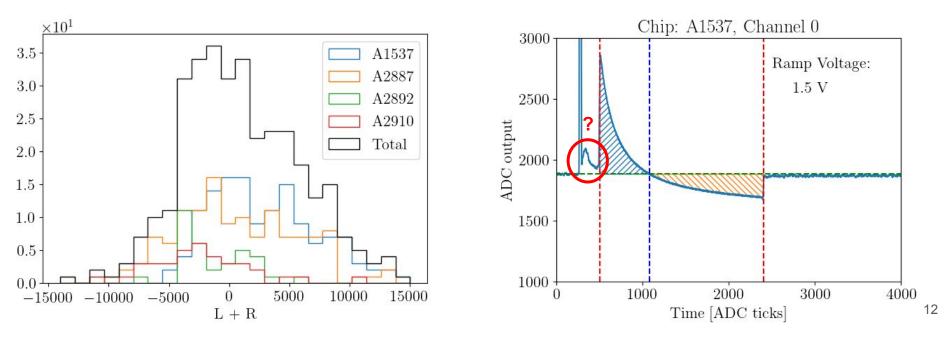

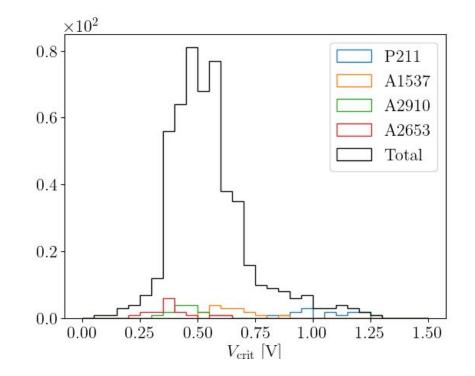

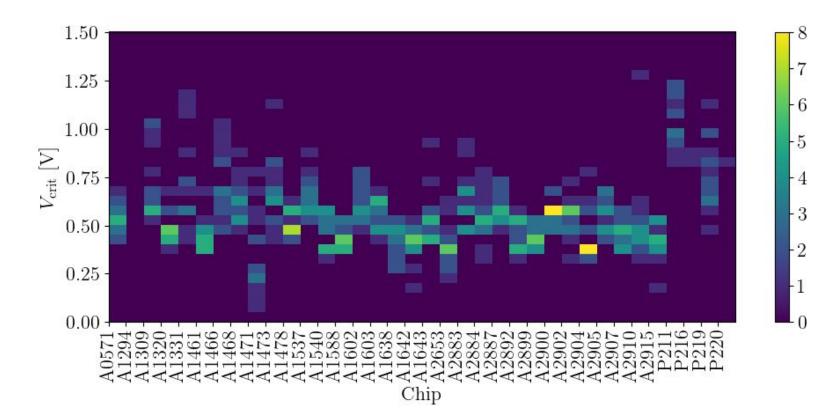

Critical voltage varies a lot from chip to chip and from channel to channel.

Some chips don't really show the ledge (A1294 is the only one we found with no ledge), and others barely show "non-ledge" behavior

## Finding $V_{crit}$ (continued)

DUNE

10

# Finding V<sub>crit</sub> (continued)

By eye, the two lobes look to have the same area, but the left lobe seems to have slightly more area, on average. Maybe to do with weirdness post-pulse?

13

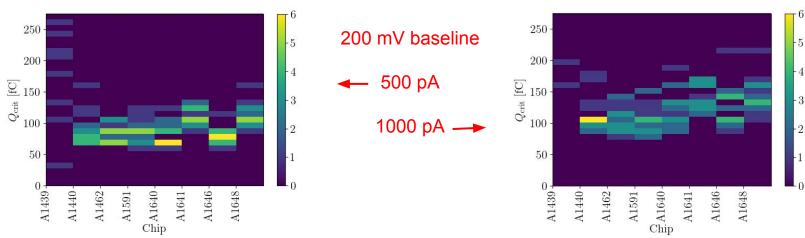

Still a WIP, different settings introduce baseline noise and jitter, so writing a generalized ledge-finding algorithm is difficult...

Look into mitigation, e.g., which baseline/leakage settings yield the highest thresholds?

#### Thank For Listening!

## Plots in Input Voltage

## Plots in Input Voltage

**D**

## Plots in Input Voltage