# DIGITAL LOW LEVEL RF DEVELOPMENT AT DIAMOND LIGHT SOURCE

P Gu<sup>+</sup>, C. Christou, P. Hamadyk, G. B. Christian, D. Spink, L. T. Stant and A. Tropp, Diamond Light Source, Oxfordshire, UK A. Salom and F. Perez, CELLS-ALBA Synchrotron, Cerdanyola del Vallès, Barcelona, Spain

### Introduction

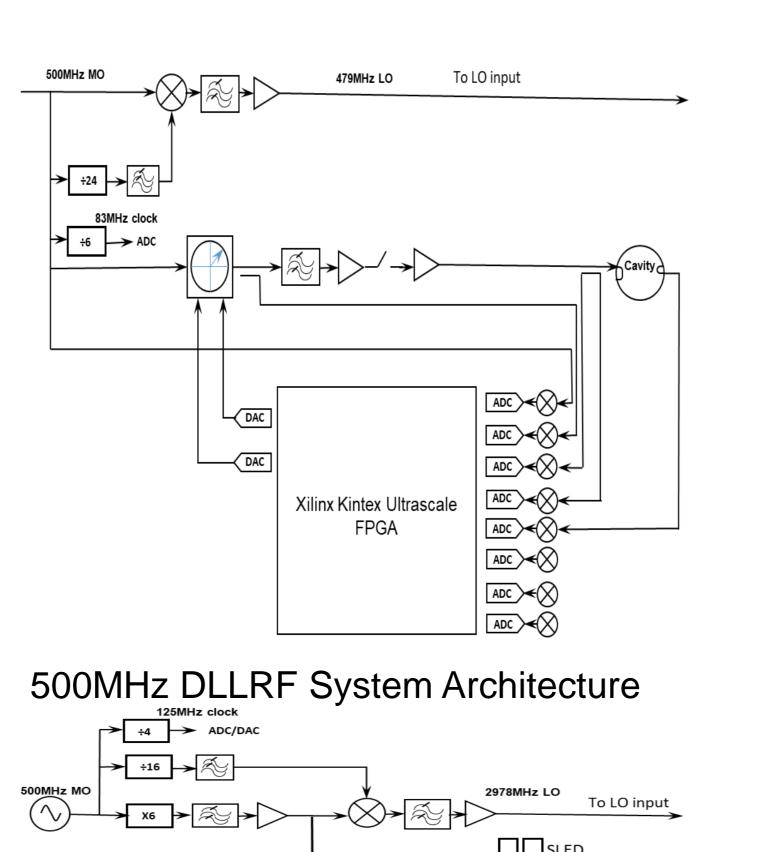

DLLRF was successfully tested on the booster cavity of Diamond and is in routine operation with two normal conducting HOM-damped cavities in the Diamond stor-age ring. Six systems were built in total and three have been deployed. In the last few years, MTCA rear-transition-modules (RTM) with integrated RF front-ends working at 500 MHz and 3 GHz have become available. This offers more integrated solution for DLLRFs. The new SIS8300-KU with RTM was chosen for the next stage of the DLLRF development. Firmware, software and supporting hardware are being developed and tested. We are aiming to develop a common platform for the different RF systems in Diamond, including

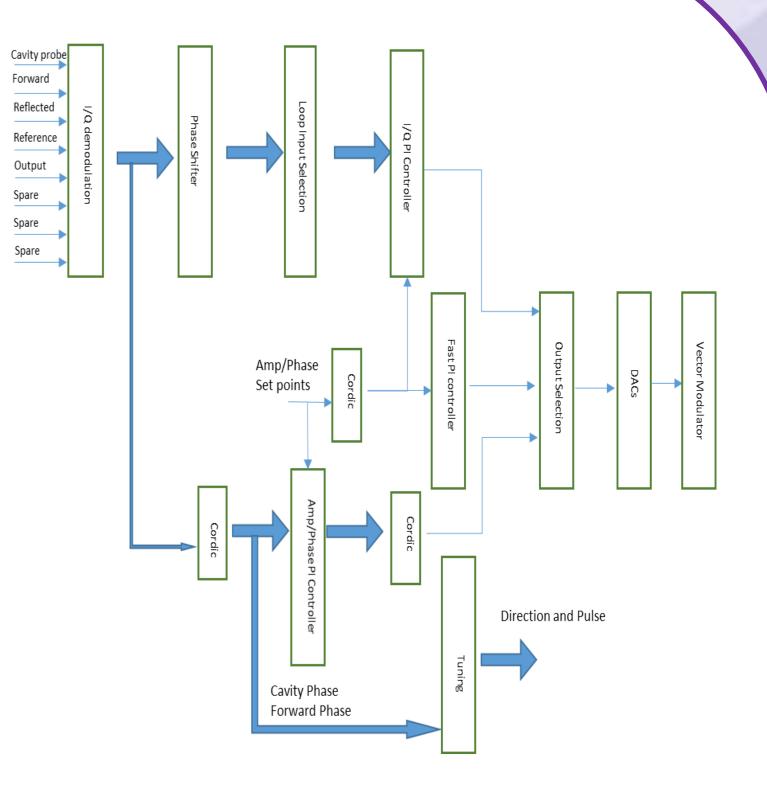

## **DLLRF** Firmware

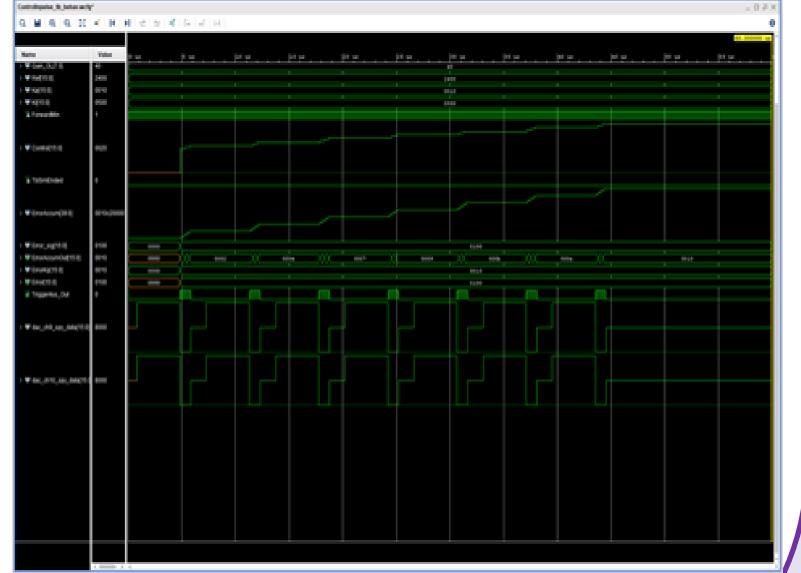

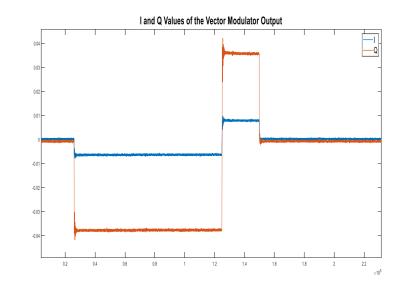

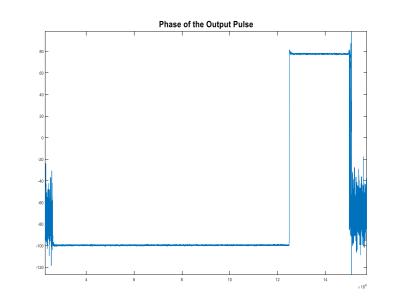

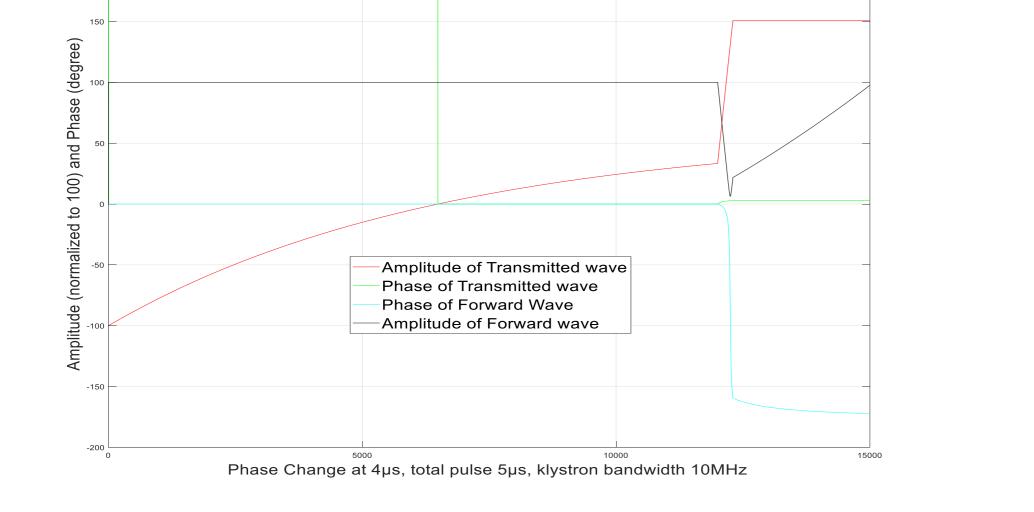

The 500MHz DLLRF and 3GHz DLLRF share many common modules, like IQ demodulation, Cordic, PI loop etc. . The 500MHz DLLRF can be configured to run 3 namely the normal modes, conducting booster cavity mode, superconducting storage ring cavity mode normal and conducting storage ring cavity mode. 3GHz DLLRF works in pulse mode. SLED operation requires the DLLRF to generate a pulse with phase and amplitude modulation. Phase and amplitude feedback will be needed to correct the pulse to pulse variation and long term drift. Phase and amplitude modulation is required in the final 1µs. A simulation in Xilinx Vivado is shown in Figure on the right. A simple phase switch with feedback control is implemented. This can be easily extended to full phase and amplitude modulation pulse.

#### the storage ring, the booster and the linac.

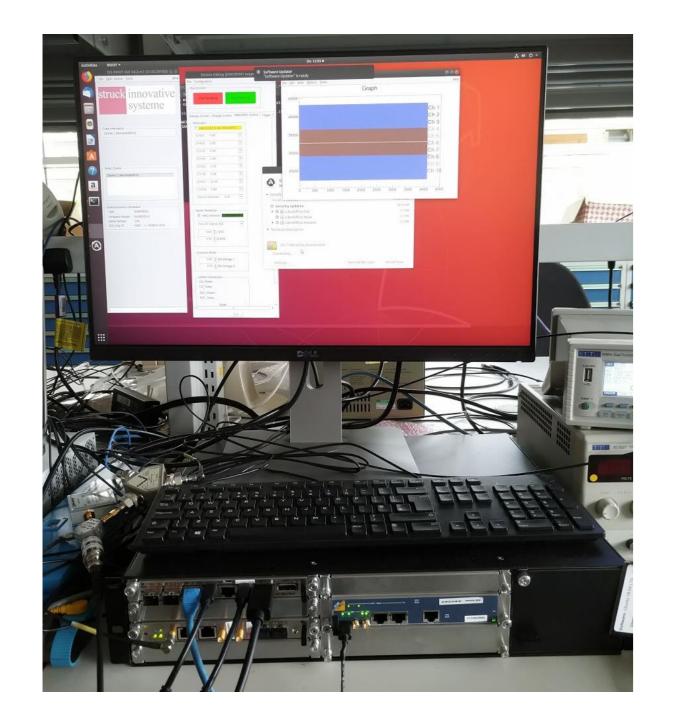

# DLLRF Hardware

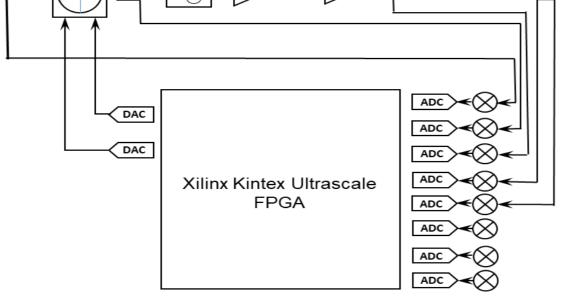

The DLLRF consists of a 2U MTCA.4 chassis, a MCH, an AMC computer board, a Struck SIS8300-KU card, a Struck DWC8VM1 RTM with supporting clock/local oscillator generation (LO)/reference RF circuits.

To Linac

3GHz DLLRF System Architecture

## SLED Operation Requirement

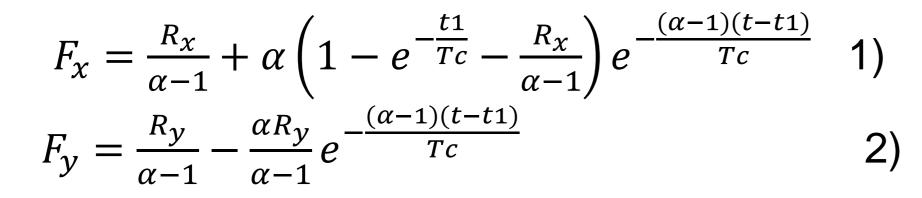

When operating in top-up mode for user beam the linac accelerates a single bunch of electrons, which is compatible with the generation of a peaked power pulse in the simplest mode of SLED operation. To fill the ring, from empty, however, the linac must accelerate a train of up to 120 bunches. A standard phase switch mode operation results in around 7% energy spread and so a flat-top pulse is required. I and Q components of SLED input pulse should follow the equations below.

SLED Input and Output with Optimized Coupling Coefficient

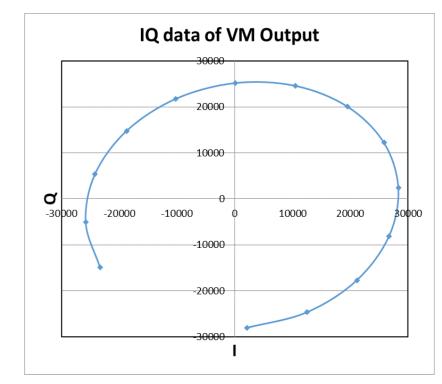

The test of vector modulator output is shown in figure 6. IQ imbalance and offset can clearly be seen. This is not a problem for the storage ring as the feedback loops will correct the output. The 3GHz DLLRF for the Linac may need calibration to compensate these errors.

The first results of the 3GHz DLLRF are shown in Figure on the right. The top plot shows the IQ data, while the bottom plot shows the phase during the pulse. A phase switch of 180° during the final 1µs can be seen clearly. This IQ profile is to accomplish sufficient pulse compression for single bunch linac operation. This can be easily extended to a phase and amplitude modulation pulse.

Vector Modulator Test

**3GHz DLLRF Test**

## References

NEW DLLRF TESTS

Pengda Gu, C. Christou et al., "Digital Low Level RF Systems for Diamond Light Source", in Proc. 8th Int. Particle Accelerator Conf. (IPAC '17), Copenhagen, Denmark, May 2017, pp. 4089-4091.

Benjamin Woolley, Igor Syratchev et al, "Control and performance [2] improvements of a pulse compressor in use for testing accelerating structures at high power", in PHYSICAL RE-VIEW ACCELERATORS AND BEAMS 20, 101001 (2017).