# An Arria10 SOM based FPGA Controller for LLRF Applications

P. Varghese\*, B. Chase, E. Cullerton, S. Raman, D. Klepec Fermilab, Batavia, IL, USA

S2-32

### Introduction

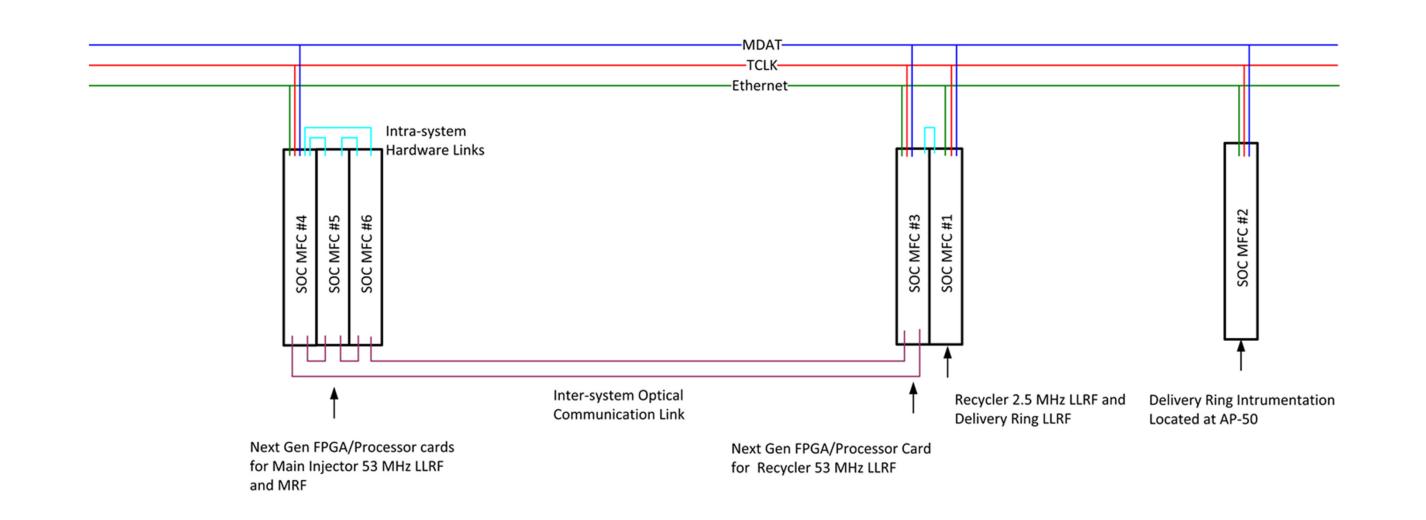

SOM(System On a Module) based FPGA boards allow the simplification of the LLRF hardware design to SOM carrier cards with primarily analog components and connectors. The SOM module contains a large SoC FPGA with a dual core ARM microprocessor and other digital components such as DDR4 SDRAM, flash memory, power management and clock generators. The Fermilab LLRF controller board is a network attached device (NAD) targeted for use in a variety of LLRF applications in new and upgrade projects.

| Device Feature                | Specifications    | Number of Channels                 |

|-------------------------------|-------------------|------------------------------------|

| High Speed ADC                | 16-bit, 125 MSPS  | 16                                 |

| High Speed DAC                | 14-bit, 125 MSPS  | 8                                  |

| Low speed DAC                 | 16-bit, 200 kSPS  | 4                                  |

| FPGA                          | ARRIA10           | 660k LE                            |

| Processor                     | Dual Core ARM     | 1.6 GHz                            |

| DDR4 (Processor)              | 32-bit, 2400 MT/s | 4 GB                               |

| DDR4 (FPGA)                   | 32-bit, 2400 MT/s | 4 GB                               |

| Software/Configuration        | eMMC/EPCQ         | $32 \; \mathrm{GB}/512\mathrm{MB}$ |

| 18x19 multipliers             | Fixed Point       | 3,376                              |

| Variable-precision DSP blocks | SP Floating Point | 1,688                              |

| Digital Inputs (Triggers)     | TTL, 50 $\Omega$  | 8                                  |

| Digital Outputs               | TTL, 50 $\Omega$  | 16                                 |

| Gbit Ethernet                 | RJ45              | 2                                  |

| High Speed Xcvrs              | QSFP, 4x10 Gbps   | 3                                  |

| USB                           | 2.0, 3.0          | 1x, 1x                             |

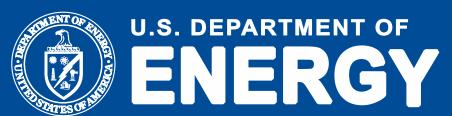

## LLRF System Configuration for Mu2e Stage I

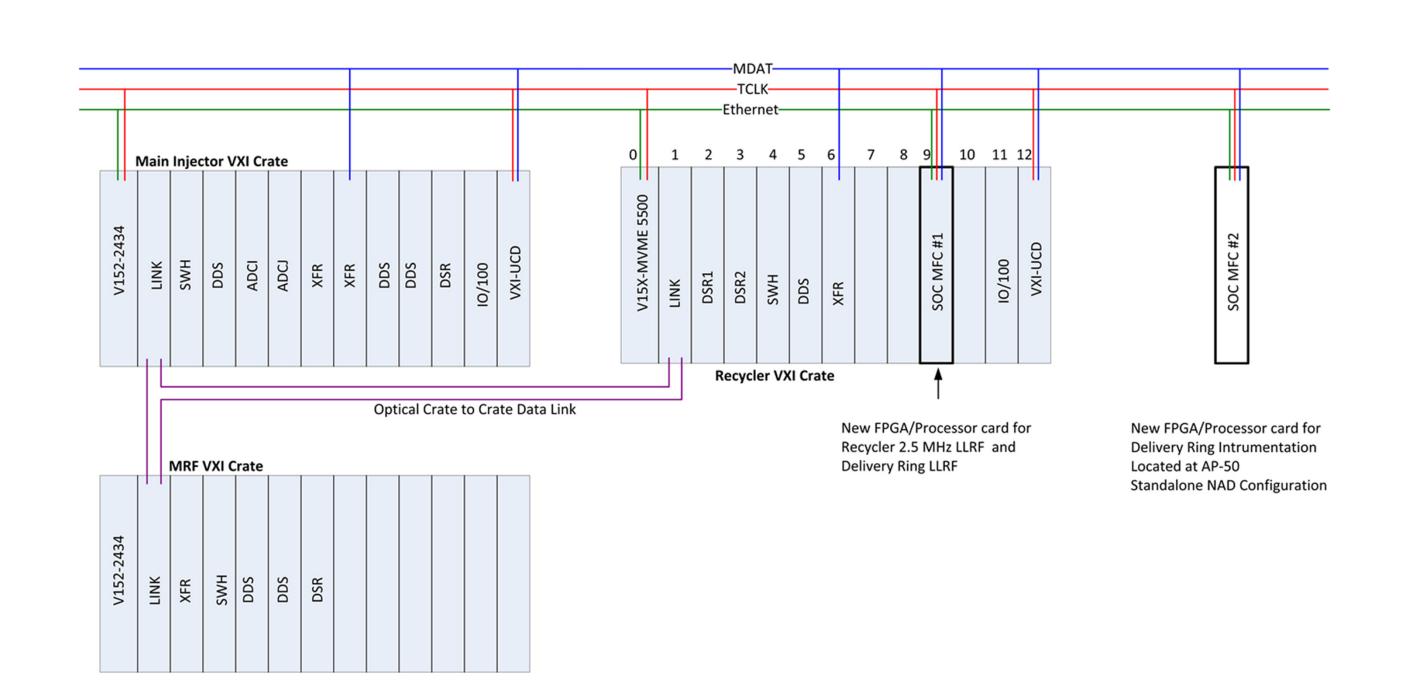

# LLRF System Upgrade for PIP-II/Mu2e Stage II

# \*varghese@fnal.gov

#### **Board Overview**

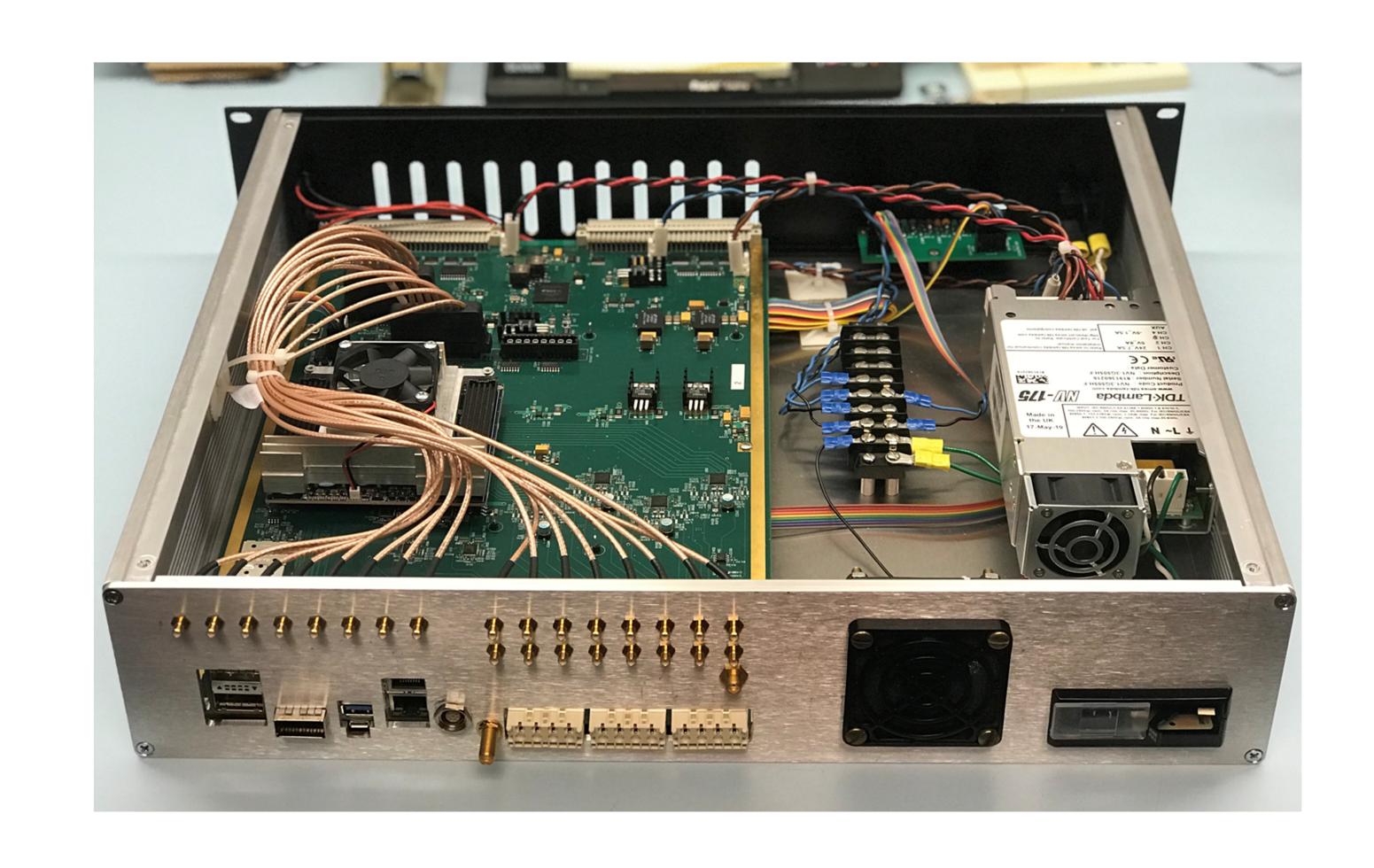

### **Chassis Prototype**

## Summary

- A general purpose network attached digitizer board with a large FPGA and multiple high speed fiber/ethernet connections has been developed targeted at new projects such as Mu2e and PIP-Il as well as an upgrade path for older LLRF systems.

- A prototype is being tested and a production board will be released by the end of the year.