####

## Fermilab PIP-II Era Booster LLRF Upgrade

Ed Cullerton LLRF 2019 Workshop 9/30/2019

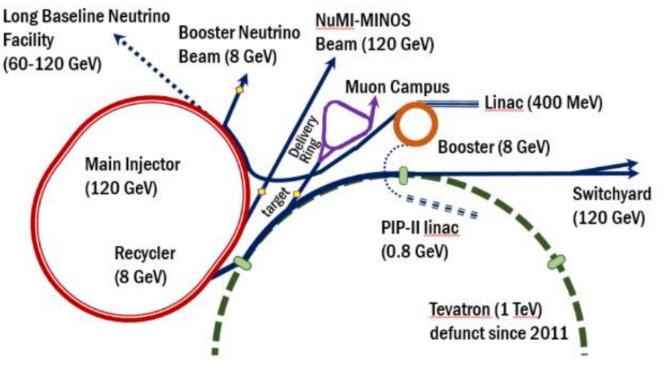

#### **Fermilab PIP-II**

Planned PIP-II 800 MeV Linac to replace the current 400 MeV Linac

#### **Fermilab Booster**

Fermilab Accelerator Complex

# **Fermilab Booster PIP-II Requirements**

| Performance Parameter                                                | Present               | PIP II Requirement   | Units         |

|----------------------------------------------------------------------|-----------------------|----------------------|---------------|

| Input (H <sup>-)</sup> Beam Energy (Kinetic)                         | 400                   | 800                  | MeV           |

| Output Beam Energy (Kinetic)                                         | 8.0                   | 8.0                  | GeV           |

| Protons per Pulse (injected)                                         | 5.0×10 <sup>12</sup>  | 7.0×10 <sup>12</sup> |               |

| Protons per Pulse (extracted)                                        | 4.75×10 <sup>12</sup> | 6.4×10 <sup>12</sup> |               |

| Beam Pulse Repetition Rate                                           | 15                    | 20                   | Hz            |

| RF Frequency (injection)                                             | 37.9                  | 44.7                 | MHz           |

| RF Frequency (extraction)                                            | 52.8                  | 52.8                 | MHz           |

| Injection Time                                                       | .04                   | 0.6                  | msec          |

| Injection Turns                                                      | 18                    | 315                  | Turns         |

| Beam Emittance (6 $\sigma$ , normalized; $\epsilon_x = \epsilon_y$ ) | <18                   | <18                  | $\pi$ mm-mrad |

| RF Volts (Max)                                                       | 1100                  | 1200                 | V             |

| Delivered Longitudinal Emittance (97%)                               | .08                   | 0.08                 | eV-sec        |

| Booster RF Stations                                                  | 22                    | 22                   | Count (A&B)   |

LLRF System must be capable of the following:

- Rep rate increased from 15 Hz to 20 Hz.

- Injection time lengthened from 40 us to 600 us.

- RF frequency sweep changed from 37.9-52.8 MHz to 44.7-52.8 MHz.

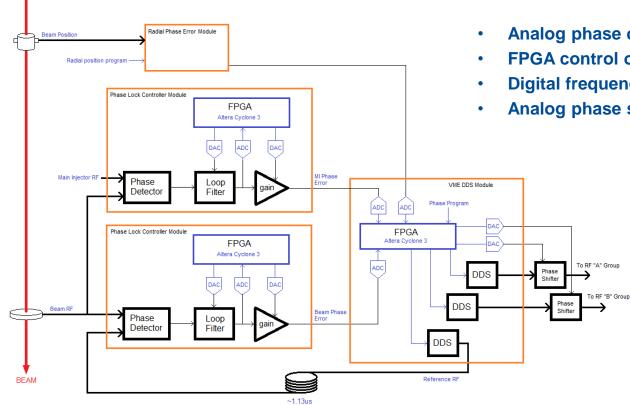

### **Current Booster LLRF System**

- Analog phase detectors and feedback gain

- **FPGA** control of analog feedback

- **Digital frequency control and synthesis**

- Analog phase shifters for radial position control

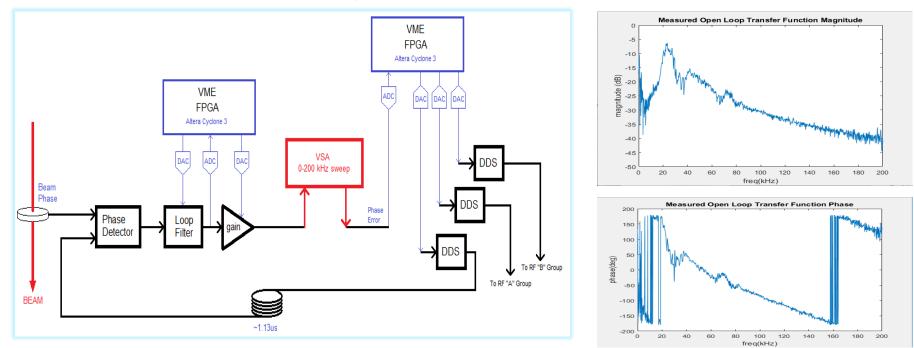

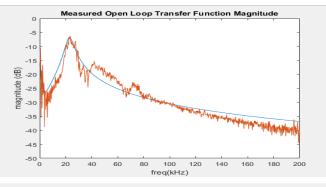

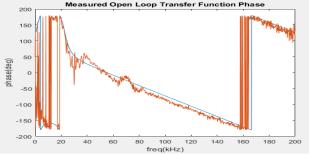

#### **Current Booster LLRF System Open Loop Measurement**

Total Loop delay = 4.5 us Calculated delay of LLRF system = 3.37 us

#### **Open Loop Response – MATLAB Model vs Measured Data**

Model Parameters:  $\omega_s = 2 \cdot \pi \cdot 23e3$ Q = 3.5 $G_r = 0$

Blue = MATLAB model Red = Measured data

### Fermilab Booster LLRF Upgrade Goals

- Reduce delay through the system

- Increases closed loop gain

- Simplify architecture

- Reduce number of FPGA's from 3 to 1

- Complete controller logic on single FPGA.

- Simplify hardware layout.

- Simplify integration to PIP-II control system, timing system.

- Increase digital and RF system diagnostics.

- Ability to run at 20 Hz.

- Simplify future control system configuration upgrades.

- Simplify future FPGA hardware upgrades.

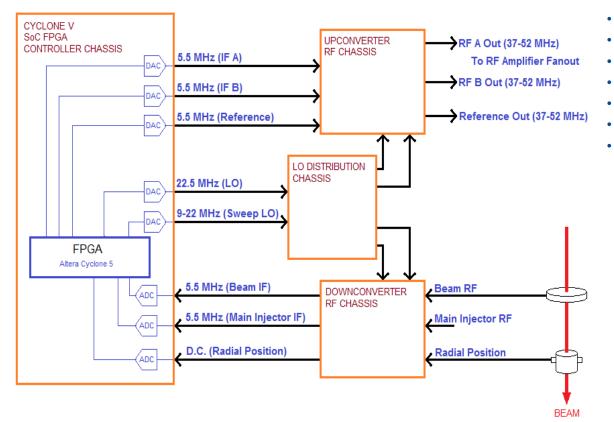

## **Proposed Booster LLRF System**

- Single FPGA

- Fully digital feedback system

- Increased digital and analog diagnostics

- Increased system control

- Upgradable

- Low cost

- Reduced electrical

- Simple Hardware Layout

|     | Booster Upconve<br>Fermilab Proton \$                          | rter RF Chassis<br>Source LLRF                  |                      |                      |               |                        |                 | 0                  |

|-----|----------------------------------------------------------------|-------------------------------------------------|----------------------|----------------------|---------------|------------------------|-----------------|--------------------|

|     | 22.5 MHz LO                                                    | RF A (5.5 MHz)                                  | RF A (28 MHz)        | RF A (37-52 MHz)     | REF (5.5MHz)  | REF (28 MHz)           | REF (37-62 MHz) |                    |

|     | 9-24 MHz Sweep LO                                              | RF B (5.5MHz)                                   | RF B (28 MHz)        | RF B (37-52 MHz)     |               |                        |                 | © +5V 👝            |

|     | Booster LO Distri<br>Fermilab Proton S                         | bution Chassis<br>Source LLRF                   |                      |                      |               |                        |                 | -                  |

|     | 22.5 MHz LO                                                    | 9-24 MHz Sweep LC                               |                      |                      |               |                        |                 |                    |

| -   | terminate all m                                                | anitors 50 Ohm                                  |                      |                      |               |                        |                 | <sup>⊙</sup> +5V 🕳 |

|     | Booster Downcor                                                | werter Chassis                                  |                      |                      |               |                        |                 | 0                  |

|     | Fermilab Proton S                                              | Source LLRF                                     |                      |                      |               |                        |                 | _                  |

|     | 22.5 MHz LO                                                    | Source LLRF<br>BEAM (5.5 MHz)                   | BEAM (28 MHz)        | BEAM (37-52 MHz)     | RADIAL POSITI |                        |                 |                    |

| 0   | 22.5 MHz LO                                                    | BEAM (5.5 MHz)                                  |                      |                      |               | ON<br>terminate all mo | nitors 50 Ohm   | • +5V _            |

| 0   | 22 5 MHz LO<br>(0<br>9-24 MHz Sweep LO<br>(0<br>SOC-MFC FPGA ( | BEAM (6.5 MHz)<br>(Co<br>MI RF (5.5 MHz)<br>(Co | ()<br>MI RF (28 MHz) | ()<br>MI RF (52 MHz) |               |                        |                 |                    |

| 0   | 22 5 MHz LO<br>(0)<br>9-24 MHz Sweep LO<br>(0)                 | BEAM (6.5 MHz)<br>(Co<br>MI RF (5.5 MHz)<br>(Co | ()<br>MI RF (28 MHz) | ()<br>MI RF (52 MHz) |               |                        |                 | • +5V              |

| 0 0 | 22 5 MHz LO<br>(0<br>9-24 MHz Sweep LO<br>(0<br>SOC-MFC FPGA ( | BEAM (6.5 MHz)<br>(Co<br>MI RF (5.5 MHz)<br>(Co | ()<br>MI RF (28 MHz) | ()<br>MI RF (52 MHz) |               |                        |                 |                    |

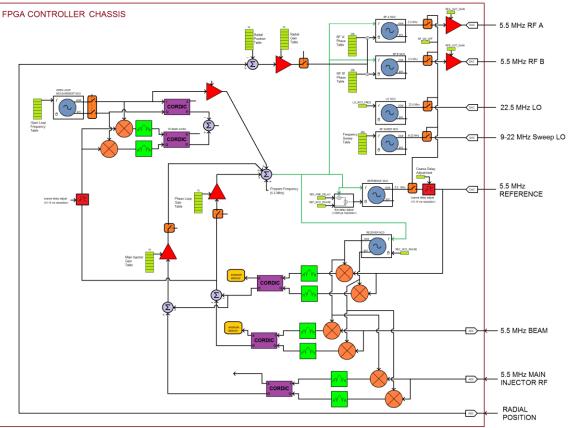

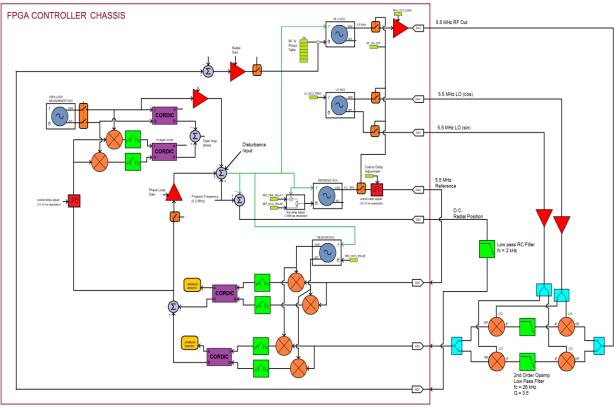

#### **FPGA Controller**

- NCO's for RF signal generation

- I/Q receivers.

•

•

- CORDIC amplitude and phase measurement.

- Internal digitally delayed reference.

- Open loop measurement circuit.

- ~1.2 us delay through FPGA chassis (includes ADC's and DAC's).

- 5.5 MHz IF chosen because running the ADC's at 66 MHz, implementing downconverter CIC filters at fs/6 is simple.

- Low 5.5 MHz IF allows for low cost ADC/DAC components.

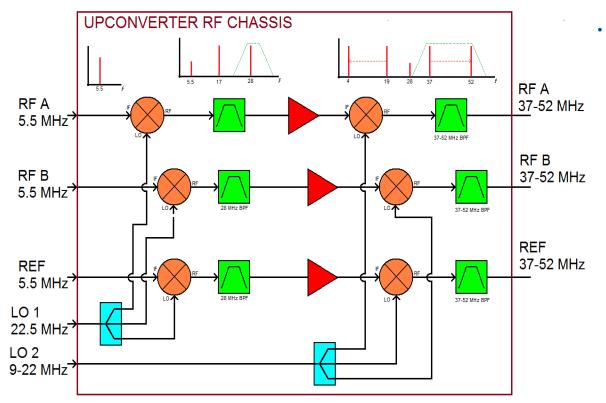

# **RF Signal Processing - Upconverter**

IF/LO frequencies chosen for simplified analog and digital filter implementation

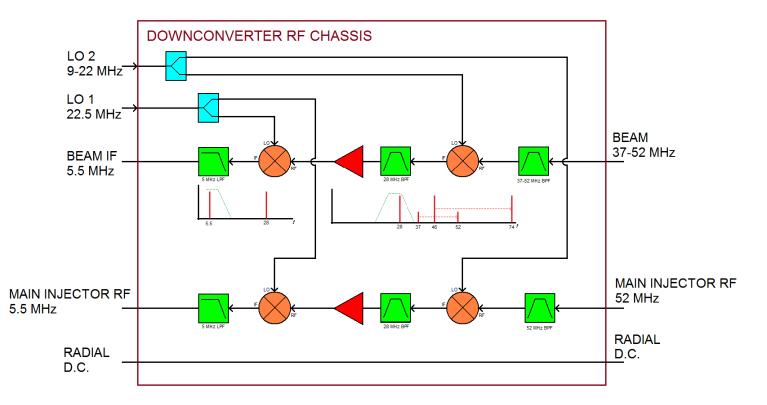

# **RF Signal Processing - Downconverter**

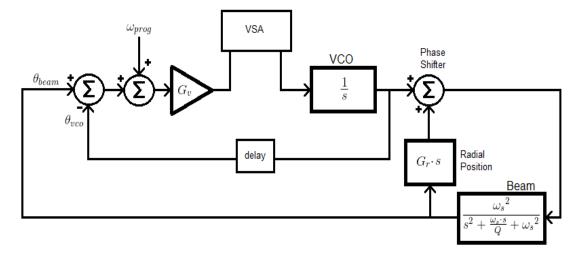

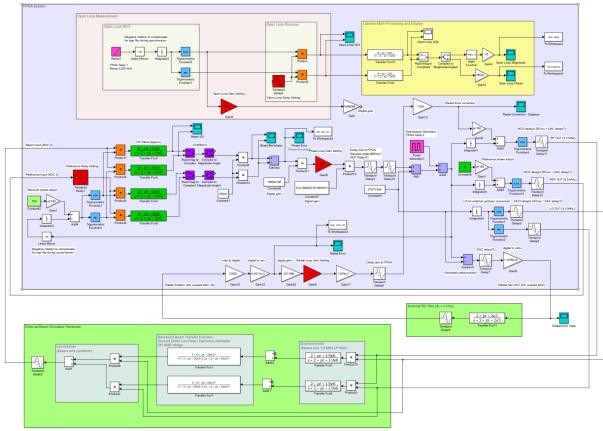

# **Simulink Time Domain Simulation**

#### Simulink model features:

- Radial position simulation included.

- External radial position low pass filter.

- External beam simulation circuit uses I/Q down conversion to baseband, followed by second order low pass filters, then upconverted back to IF.

- Open loop simulation circuit included in the FPGA block.

#### Simulations:

- Simulation of open loop transfer function for comparison to measured data.

- Simulation with disturbance added to the frequency input of NCO's to measure the feedback suppression of phase error and radial position error.

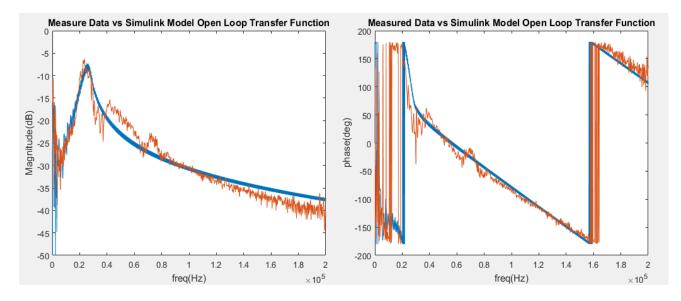

## **Simulink Open Loop Simulation**

To match measured data, the model has the following parameters:

- 4.5 us of total electrical delay

- Beam simulation circuit has fc of 23 kHz and a Q of 3.5.

Simulink model showing good agreement with measured data.

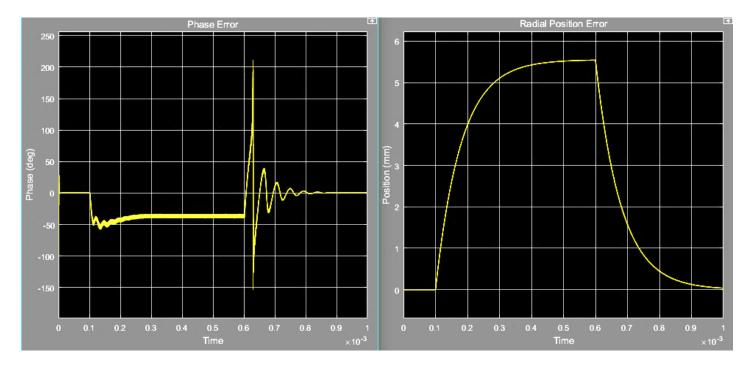

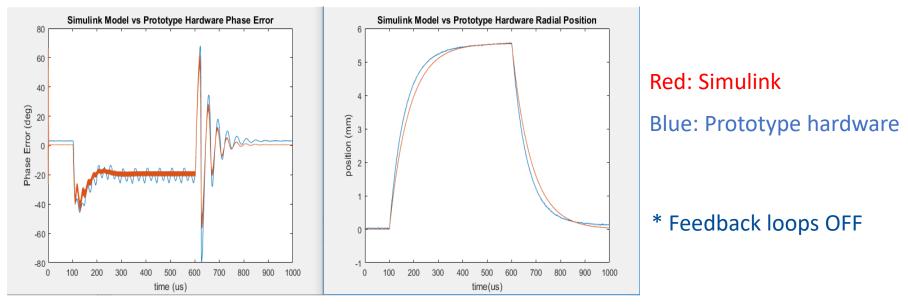

#### **Simulink Disturbance Response**

- 20 kHz step at frequency input of NCO

- Phase and radial feedback loops OFF

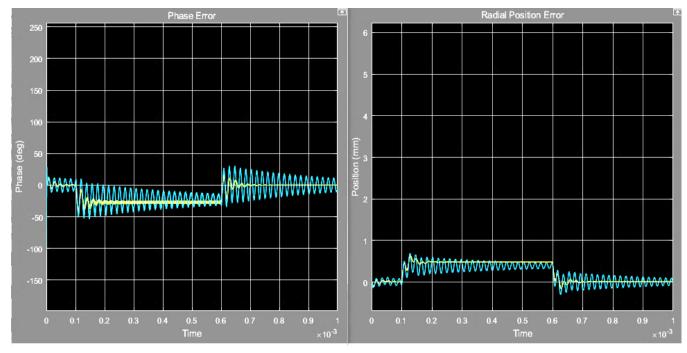

## **Simulink Disturbance Response**

#### Yellow:

- Phase loop gain of ~670 Hz/deg

- Stable operation

#### Blue:

Phase loop gain of 830 Hz/deg

Fermilab

Instabilities starting

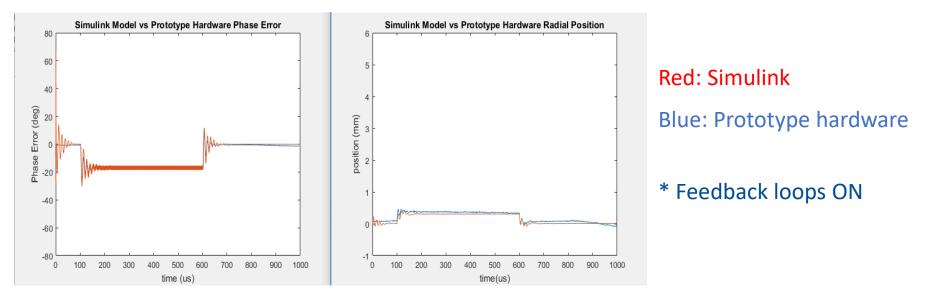

- 20 kHz step at frequency input of NCO

- Phase and radial loops ON

- Radial loop gain held constant

- Phase loop electrical delay = 4.5 us

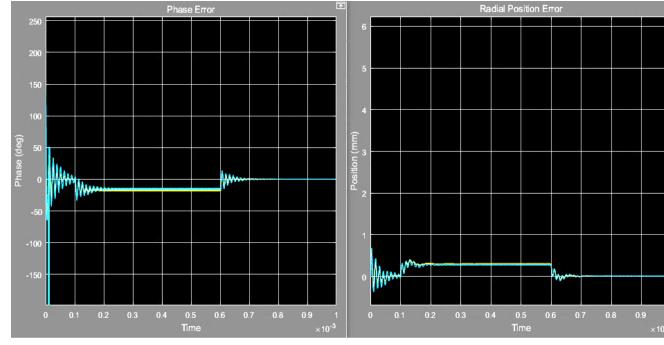

#### Simulink Disturbance Response – reduced electrical delay

#### Yellow:

- Phase loop gain of 1120 Hz/deg

- Stable operation

#### Blue:

• Phase loop gain of 1230 Hz/deg

🛠 Fermilab

Instabilities starting

- 20 kHz step at frequency input of NCO

- Phase and radial feedback loops ON

- Radial loop gain held constant

- Phase loop electrical delay = 2.8 us

\* 30% increase of phase error suppression by reducing electrical from 4.5 us to 2.8 us

# **Hardware Prototyping and Testing**

#### Hardware Test setup features:

- Signal processing done at 5.5 MHz.

- Radial position simulation included.

- External radial position low pass RC filter.

- External beam simulation circuit uses I/Q down conversion to baseband, followed by second order low pass OP-Amp filters, then upconverted back to IF.

- Open loop simulation circuit included in the FPGA block.

#### Testing:

- Measure open loop transfer function for comparison to measured data and Simulink model data.

- Measure phase error and radial error with disturbance added to the frequency input of NCO's, then compare to Simulink model data.

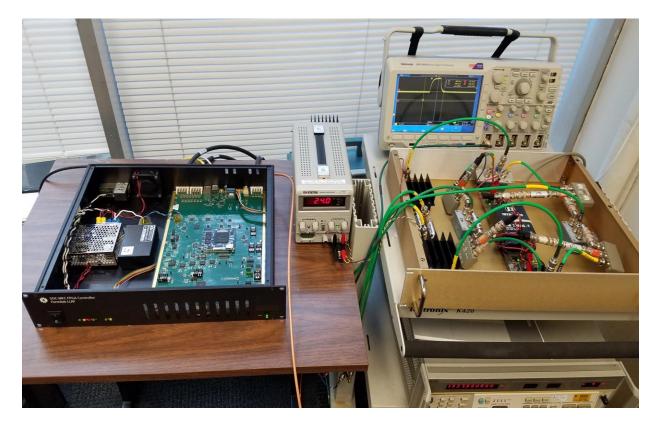

#### Hardware Prototype Testing Setup

#### **FPGA Controller Chassis Features:**

- Altera Cyclone 5 System on Chip (SoC)

- 16x 14 bit ADC's @ 66 MHz

- 8x 14 but DAC's @ 66 MHz

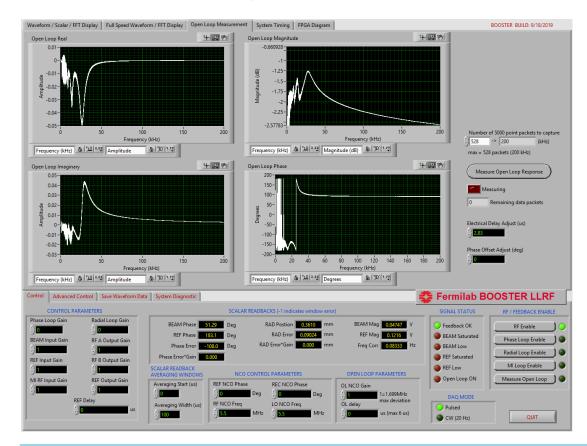

#### Hardware Prototype Open Loop Measurement

Measurement shows a phase loop electrical delay of ~2.8 us. (This is the electrical delay used in the previous Simulink simulations showing 30% phase suppression improvement)

## Hardware Prototype vs Simulink Model Disturbance Response

Good agreement between hardware prototype and Simulink model

## Hardware Prototype vs Simulink Model Disturbance Response

Hardware shows stable operation at phase loop gain of 1230 Hz/deg in agreement with Simulink model.

## Conclusions

- A prototype of a proposed hardware FPGA controller for the Fermilab PIP-II Era Booster has been developed and has completed initial testing.

- The prototyped controller shows improvement over the current system by reducing the electrical delay through the system by 1.7 us and improving disturbance suppression by over 30%.

- A MATLAB model and Simulink model have also been developed that show good agreement with the hardware prototype and measured data.

- A feasible Booster LLRF system to interface with the PIP-II Linac has been demonstrated.