## **LArTPC Pixelated Readout**

### Brooke Russell (LBNL)

with contributions from Jonathan Asaadi (UTA) and Dan Dwyer (LBNL)

DUNE P5 Strategy: Phase II Detector R&D Neutrino Physics Frontier, SNOWMASS Community Summer Study July 20, 2022

## Why pixels?

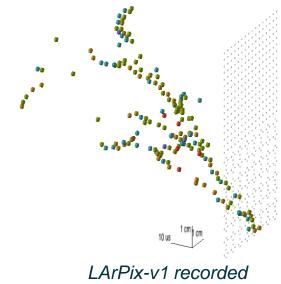

- True 3D imaging

*Unambiguous, inherently 3D <u>raw</u> data*

- Self-triggered pixel-by-pixel data ~100% livetime

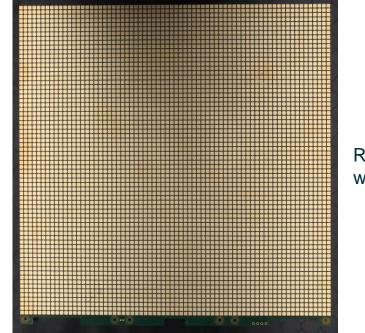

Technical challenge: instrumenting ~2000 m<sup>2</sup> anode area at 4 mm granularity  $\rightarrow$  requires scalable design

Two existing LAr pixel readout efforts discussed here:

QPix

LArPix

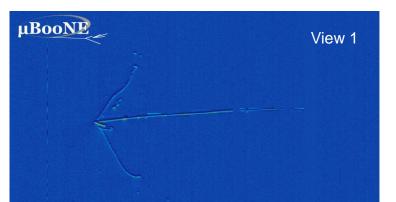

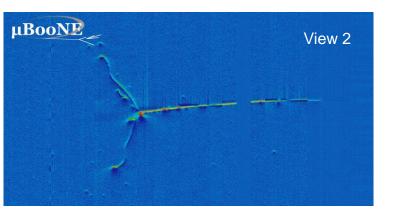

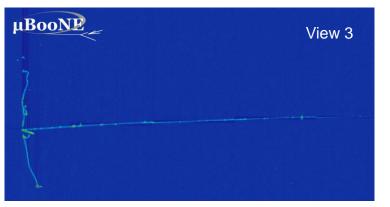

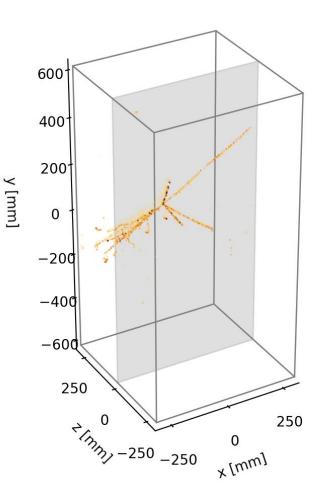

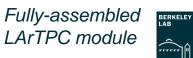

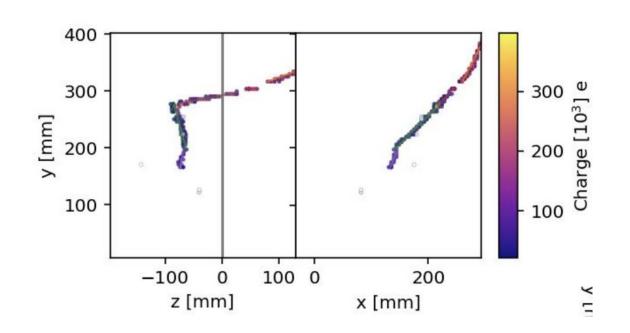

Pixel readout (LArPix cosmics data)

Traditional wire readout (MicroBooNE v data)

## QPix

The University of Manchester

**‡**Fermilab

Argonne

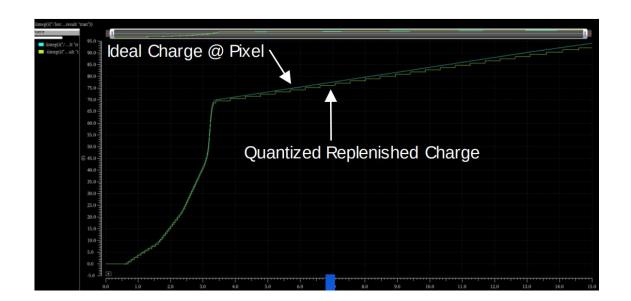

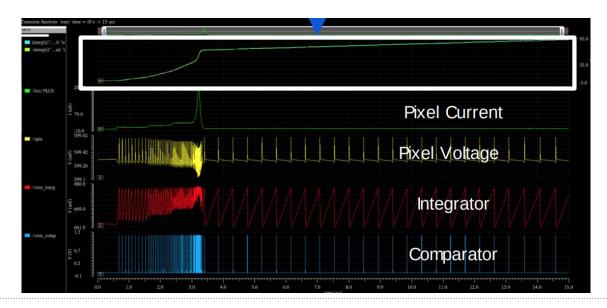

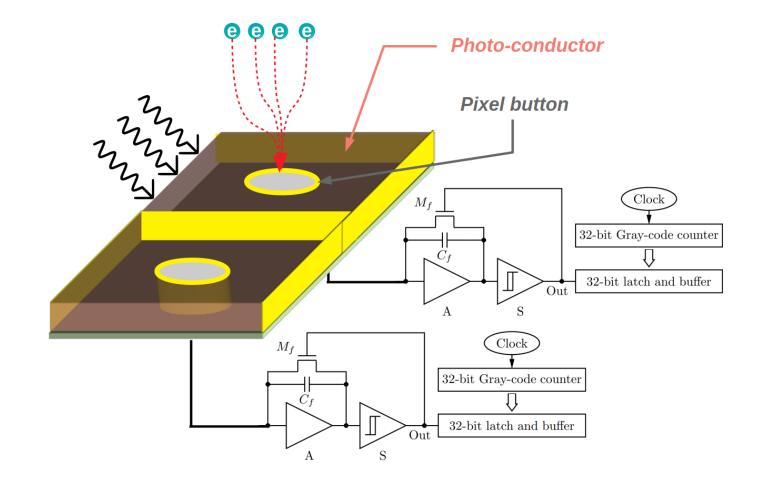

## **QPix Concept**

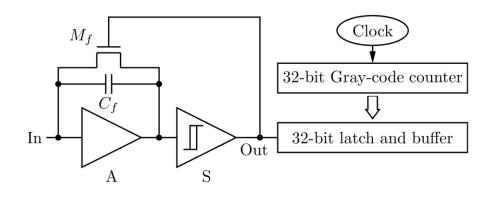

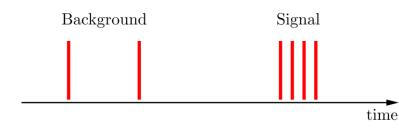

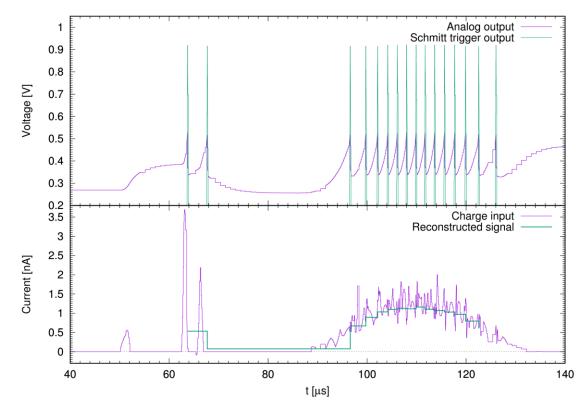

Original QPix scheme delineated by Dave Nygren (UTA) and Yuan Mei (LBNL) <u>1809.10213</u>

Datum:

- $\Delta Q = Reset Time Difference (RTD)$

- 64 bits (including 32 bit timestamp)

Transistor-level charge integration simulation for minimum-ionizing track in LAr for 1 fC threshold

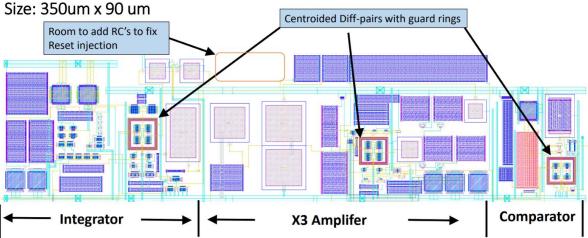

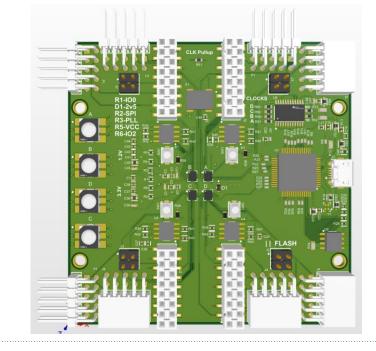

## **QPix ASIC** 180 nm Implementation

- Front-end prototype (Penn)

- charge replenishment

- "basic" reset

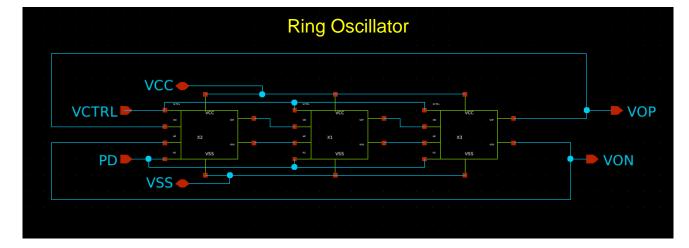

- Ring oscillator and 10-bit r2r DAC (Hawaii)

- FPGA-implemented digital readout (Hawaii)

- 4 (2x2) digital FPGAs with 16 optional IO pins per FPGA

- Optional 50 MHz "global" clock or 4x48 MHz internal clock

- → Submission targeted for August 2022

test structures and 16 channel chip

QPIX Layout: Integrator + Amplifier + Comparator

### QPix ASIC 65 nm Implementation

- Front-end design (FNAL)

- charge replenishment circuit evaluation

- Bandwidth study with ideal components

- First version of the low power front end amplifier

- dynamic vision sensing evaluation for asynchrounous photon detection

- Further work dependent on resource availability at FNAL

- → Submission targeted in 12-15 months timescale (16 channel chip)

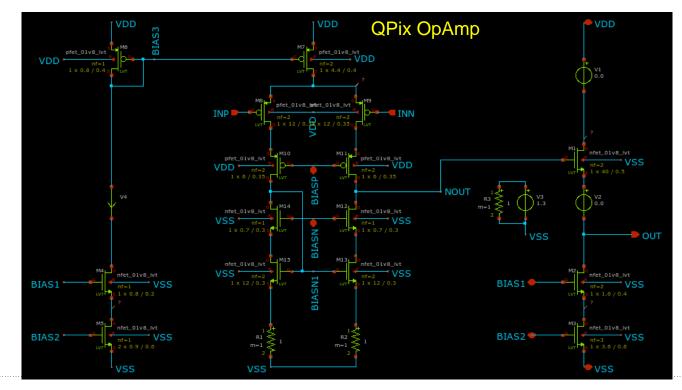

## **QPix ASIC** 130 nm Implementation

- Using eFabless + Skywater + Google open source process design

- Front-end prototype (UTA)

- · Ring oscillator

- · Relaxation oscillator

- · QPix OpAmp

- → May 2022 submission

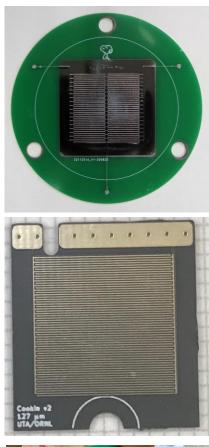

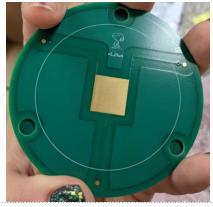

## **QPix Dual Light-Charge Readout**

Commercial PCB with 127 μm trace spacing 5 V/μm max field UTA/ORNL

Commercial PCB with 127 μm trace spacing 5 V/μm max field UTA/ORNL

Custom PCB with 25 μm trace spacing 40 V/μm target field UCSC/UTA/FNAL

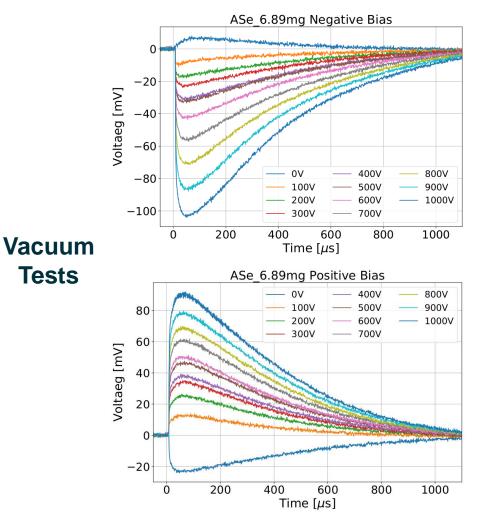

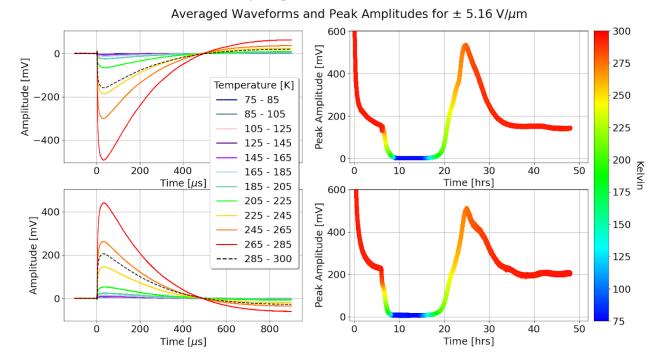

## QPix a-Se R&D

#### **Cryogenic Tests**

LArPix

B. Russell | SNOWMASS Summer Study | 7-20-2022

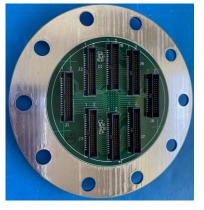

## **LArPix System Architecture**

A contained, end-to-end system focused on reliability & robustness

- Limit single-point failures

- Scalable to O(M) channel systems

- **Design features**

- Single active component in cryo environment

- Minimal and redundant connections to outside cryostat

- Mechanically and cryogenically robust

PACMAN Warm Controller

Feedthrough

32 cm by 32 cm anode PCB tile

Timing

Fiber

Ethernet

Switch

Warm

Cont oller

Timing

Master

DAQ

Power

Supply

**Pixel Tile**

Pixel Tile

LRO

Trigger

Clock

Sync

External

Trigger

Feed-

through

**Pixel Tile**

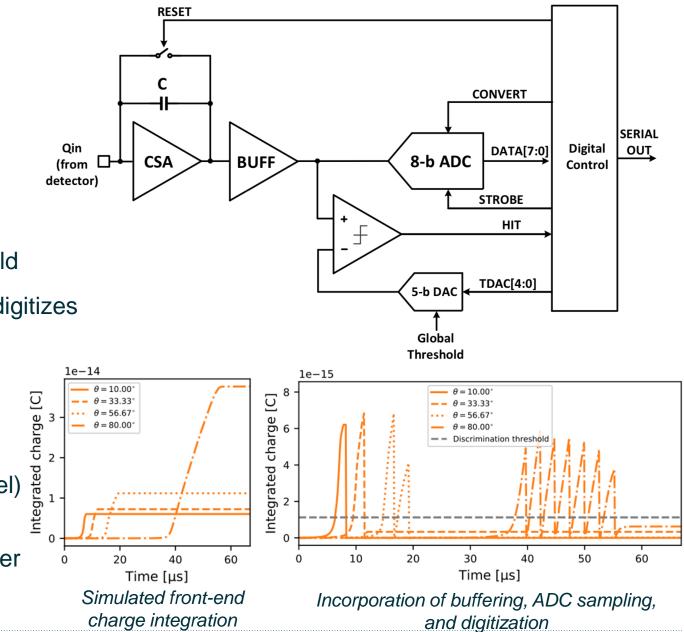

## LArPix ASIC Concept

Low-power, integrating amplifier with self-triggered digitization and readout

Pixel dormant until signal exceeds tunable threshold

- Integrates charge for  $\sim 3\mu s$  ( $\sim 4$  mm drift), then digitizes

- Ready for next signal

Pixels are continuously active

- Serial I/O data rate is slow (~5 Mb/s per channel) to limit digital power

- Modest data volumes: ~1 MB/s per square meter of anode in surface cosmic flux

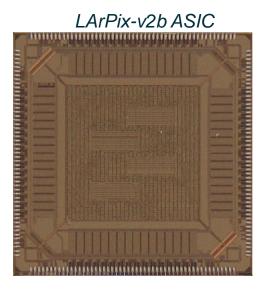

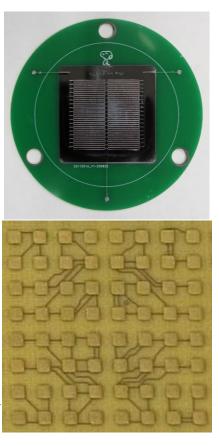

## LArPix ASIC Implementation

#### LArPix ASIC

- 64-channel CSA with self-triggered ADC

- Includes amplification, digitization, and readout ٠

- Implemented in 180 nm; migrating to 130 nm ۲

#### Design drivers

- Low power

- Low leakage

- Low noise •

- **Digital multiplexing** ۰

*O*(100 μ*W*) / channel

- < 5 e- / 500 µs

- 850 e- ENC

- O(1k) pixels / I/O channel

13

cosmic EM shower

*"LArPix-v2: a commercially scalable large-format 3D"* charge-readout scheme for LArTPCs" publication in preparation

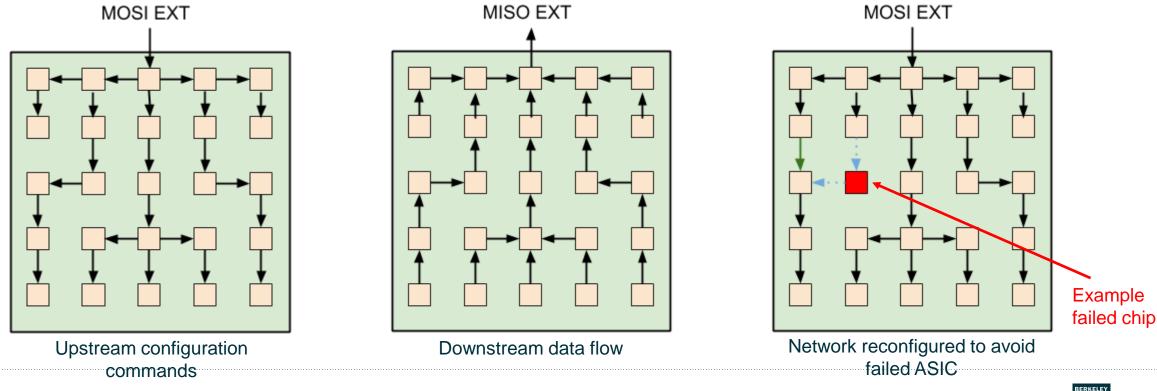

### Hydra IO Dynamic I/O routing

AD-HOC NETWORK OF READOUT APPLICATION-SPECIFIC INTEGRATED CIRCUITS FOR RELIABLE DETECTOR INSTRUMENTATION U.S. Patent Application Ser. No: 63/140,434

- I/O can occur between any neighboring chips on pixel tile

- Network constructed by explicitly connecting neighboring ASICs in a determined fashion

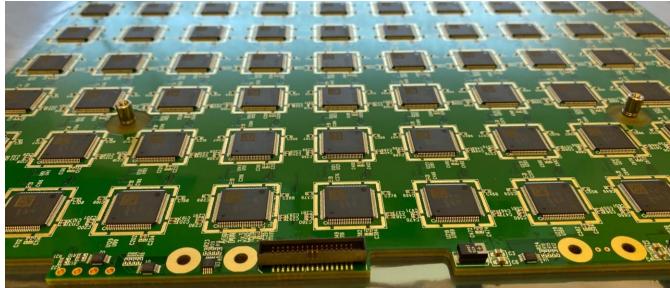

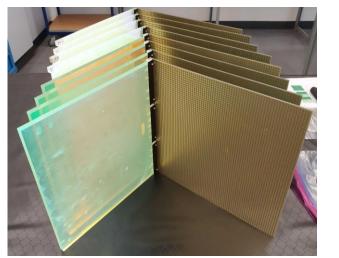

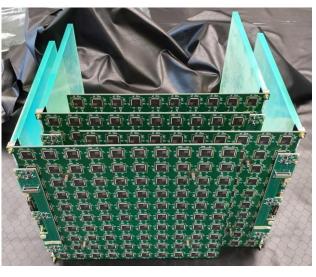

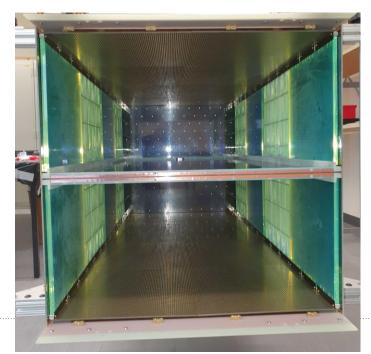

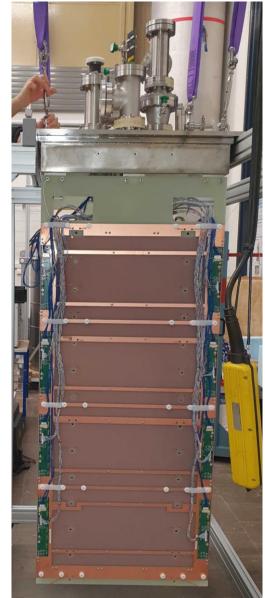

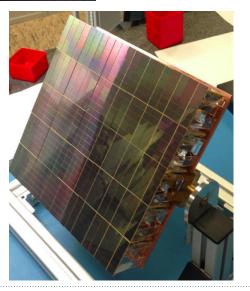

## System **Prototyping**

- All production and assembly performed by industry

- Individually tested O(10k) ASICs, O(100) pixel tiles

- Two ton-scale TPCs built and tested

Single pixel tile & light module assemblies

One anode, fully-assembled

15 Two anodes installed inside field cage

## System Prototypes .

٠

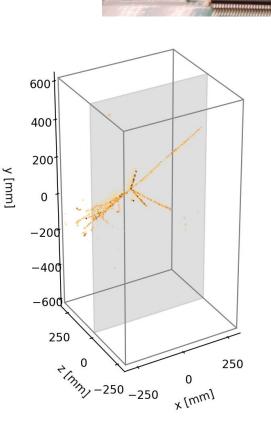

Raw data

- Successful deployment and operation of two O(100k) channel systems

- >100M cosmic ray events recorded

- Improved tracking threshold O(100 keV)/pixel

- Quick-turn industry fabrication at competitive cost O(\$0.10/channel) at large O(10 M) channel system

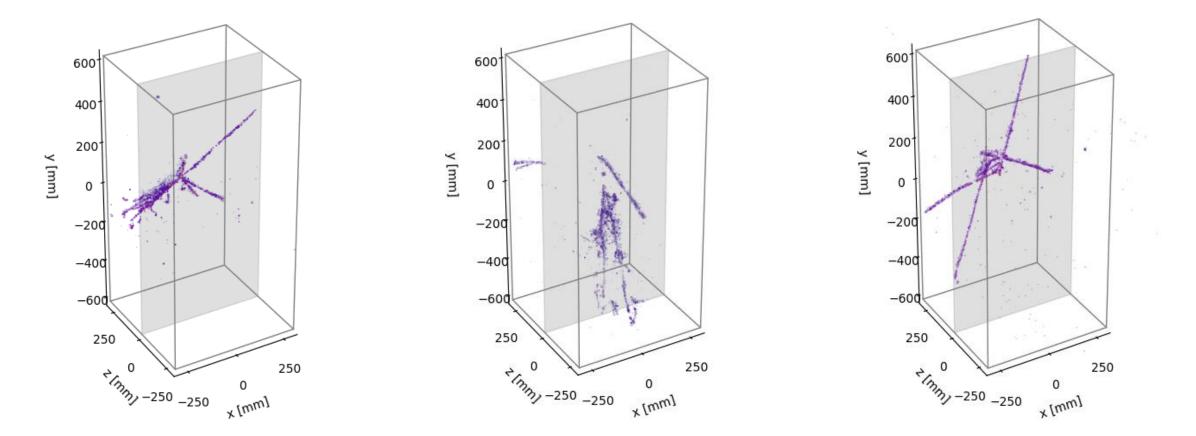

## **Physics Studies**

*"Performance of a modular ton-scale pixel-readout liquid argon Time Projection Chamber"* publication in preparation

## LightPix Concept

- Low-power cryogenic-compatible scalable (>10<sup>6</sup>)

SiPM readout electronics at very low system cost

- Adapting existing LArPix system architecture

- Shared cabling, feedthrough, warm electronics

- LightPix ASIC re-uses majority of LArPix design, but replaces ADC with TDC

- Provide a path for highly-granular photodetection systems for very large detectors

Example of light trap SiPM detector format *LCM*

Replace pixel pads with SiPMs

Example of direct SiPM detector format DarkSide-20k

#### LightPix ASIC Implementation LightPix-v1b TDC evaluation for SPE from commercial 3 mm x 3mm SiPMs RESET Linear to <1 ns over the full 100 ns ٠ С 1 PE SiPM Bias Voltar CONVERT timing range -53 V 10<sup>3</sup> -54 V TDC 2 PE 🔲 -55 V SERIAL Digital Ουτ Qin < 1 ns jitter (from CSA IEN SPE 3 PE Control | D[7:0] RAMP Trigger Count 8-b ADC detector) GEN spectrum 4 PE < 2 ns time-walk bias STROBE < 1 ns RMS global timing accuracy TDAC[4:0] 5-b DAC Global 25 50 100 125 150 175 Threshold ADC LightPix-v2 ΔTEXT - MCLK [ns] 0.20 Dual TDC/ADC functionality in 0.175 alized) single ASIC – design complete, 20 0.150 25 30 awaiting production 35 0.125 TDC output 4 50 versus test 55 Triggers 60 0.075 pulse time offset 65 70 0.050 75 80 85 0.025 90 95 SNOWMASS Summer Study | 7-20-2 0.000 B. Russell 250

TDC

## Summary

There are two existing efforts (QPix and LArPix) actively working to realize pixel readout technology for DUNE FD implementation

Clear benefits in deploying pixel readout at DUNE FD

- True 3D imaging

- Self-triggered, 100% live data

- Unique opportunity for low-energy, off-beam physics

- Mechanically and cryogenically robust

- Scalable production via industry

C401

# Technical challenges for future FD module

C446

- Scaling production and QA/QC from 200 m<sup>2</sup> (ND) to 2000 m<sup>2</sup> (FD)

- Exploring data aggregators to reduce cabling and cryostat penetrations

- Optimal techniques for scintillation light detection

## **Observation of positron decay**

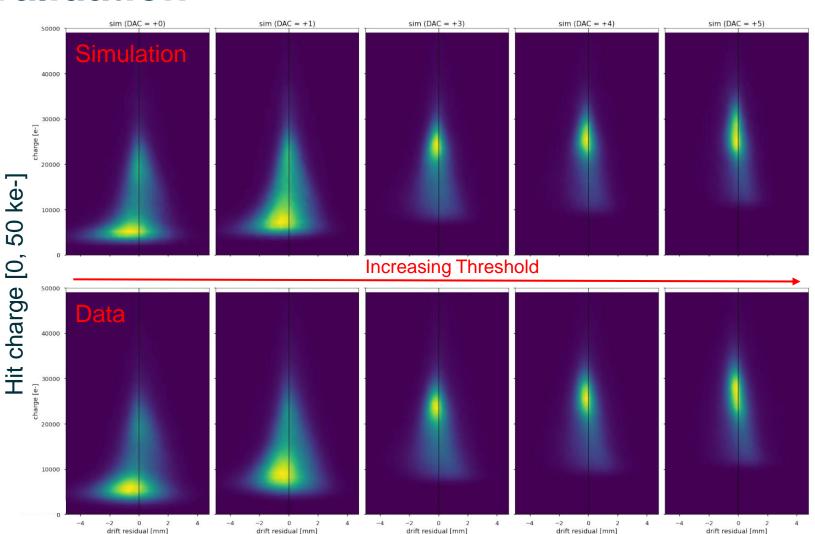

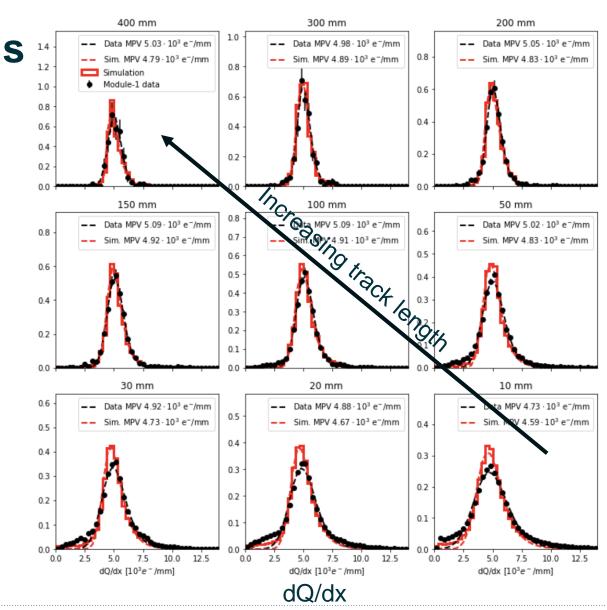

## **Pixel response validation**

- Detailed ASIC front-end charge response simulation using GPU-optimized algorithms

- To first order, good datasimulation agreement in channel threshold crossing time and charge measurement

*"Highly-parallelized simulation of a pixelated LArTPC on a GPU"* publication in preparation

Pixel trigger response versus

threshold (data versus MC)

#### Trigger time relative to track time [-3, 3 $\mu$ s]

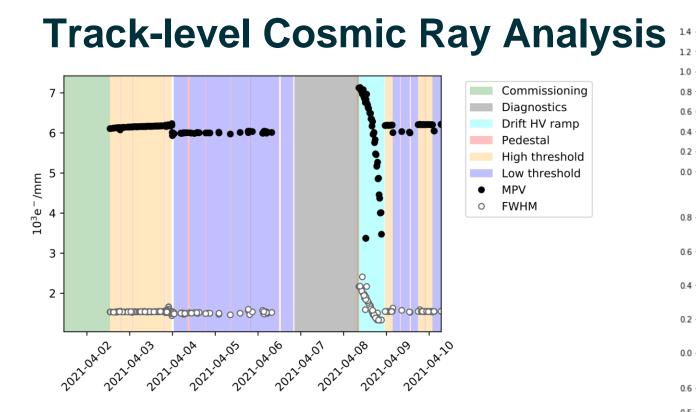

- Pixels are continuously active (>100M cosmic ray events recorded)

- Serial data packets stream out of system as channels self-trigger

- MIP response is consistent with expectation and stable throughout data taking

*"Performance of a modular ton-scale pixel-readout liquid argon Time Projection Chamber"* publication in preparation

24