#### DUNE Preliminary Design Review of Warm Interface Board and TPC Electronics System Aspects

Marco Verzocchi Fermilab 17 March 2020

#### Outline

- Introduction to DUNE

- Electronics for the readout of the TPC

- This presentation is meant as a guide for the reviewers before they look at the set of slides we had prepared for the review last week

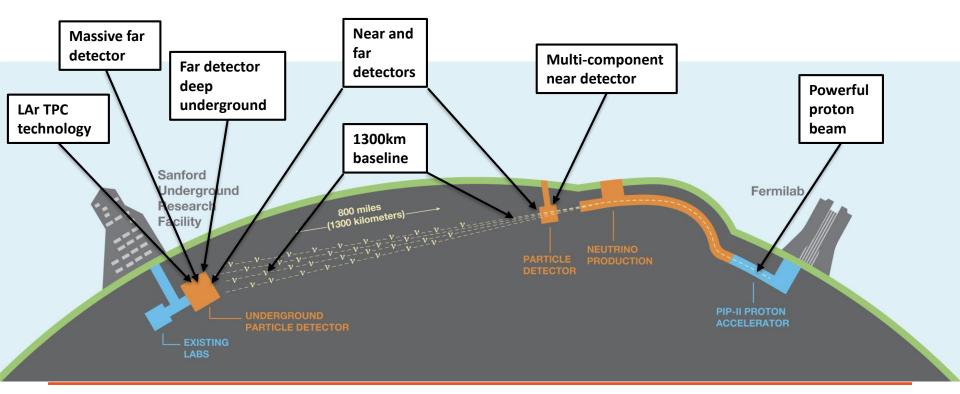

- The DUNE experiment is being built with 3 main physics goals:

- Precise measurements of neutrino oscillation parameters including study of CP violation in the neutrino system (i.e. differences in oscillation parameters between neutrinos and antineutrinos)

- Possible source for matter antimatter asymmetry in the universe

- Search for proton decay

- Physics beyond the standard model / grand unification

- Observation of neutrinos from supernova explosion

- Get a time-lapse movie of the stellar collapse

- Requirements for experiments of this kind

- Large sensitive mass, long baseline and intense neutrino source, underground

- Two technologies: water Cerenkov (HyperK, Japan), liquid argon TPC (DUNE)

- LBNF is the facility (beam from Fermilab to South Dakota, near and far site caverns, infrastructure, cryostats)

- DUNE is the experiment (liquid argon time projection chamber)

🛟 Fermilab 🖂 💦

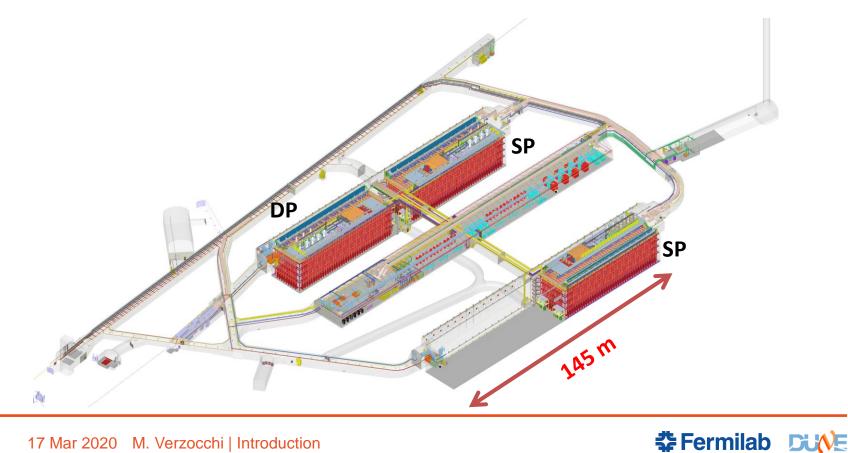

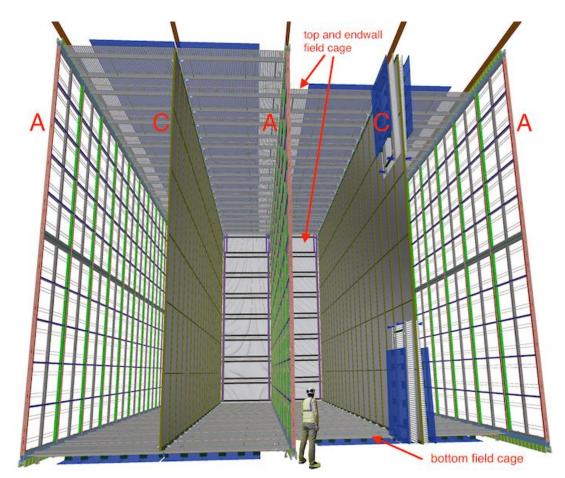

- Four separate 17 kt (> 10 kt fiducial) LAr TPCs

- 4 identically sized cryostats: 2 single phase (SP) + 1 dual phase (DP) +1 "opportunity" (this 2+1+1 plan is described in TDR)

- Single phase detector:

- 4 drift volumes of 3.5m

- Read out by a total of 150 anode plane assemblies (APAs), each with 2560 wires

- 128 channels per frontend motherboard (FEMB), 20 per APA

- Total of 384k readout channels, 3000 FEMB total

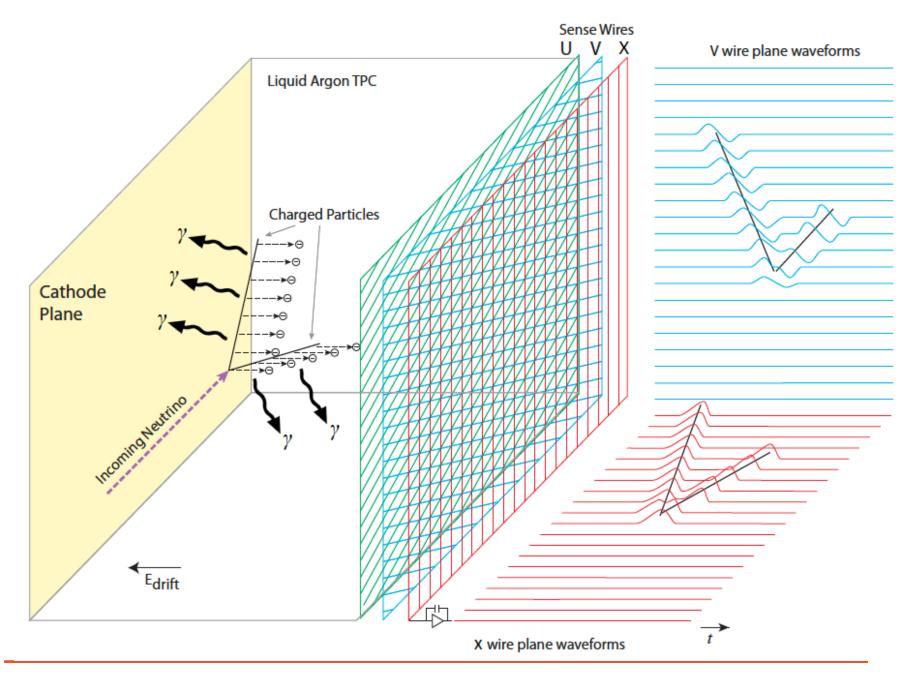

## **Signal formation**

- Wires organized in multiple readout planes (U, V, X) to allow for 3d reconstruction of ionization from tracks, unipolar signal (negative) on collection wires (X), bipolar signal (first negative then positive) on induction wires (U,V) as electron cloud travels past the wires

- Signal duration o(µs), narrower for collection plane

- 20-30k e<sup>-</sup> collected on the X wires for ionization from MIP near the cathode (3.5m distance, assume drift field 500 V/cm, 6 ms electron lifetime in Ar)

- Limited by immediate recombination (30%), losses caused by recombination along the drift distance (depends on drift field and argon purity)

- No amplification in liquid

#### 🗱 Fermilab 🛛 🖸 💦

## What we are reviewing today (i)

- Interface between the electronics inside the cryostat and the rest of the experiment

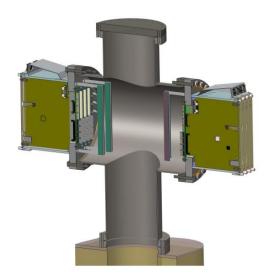

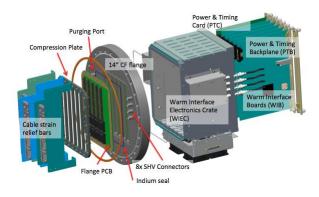

- Warm Interface Electronics Crate (WIEC, 150 of them in one detector) mounted on the flange of a cryostat penetration, houses Warm Interface Boards (WIBs) and Power and Timing Card (PTC)

- 3000 FEMBs, 6000 data paths from FEMBs to WIBs, 4 FEMB per WIB, 1 single 10 Gbps optical connection to DAQ backend per WIB (750 fibers)

- WIBs and PTC also provide clock, control, and power to the FEMBs

## What we are reviewing today (ii)

- Services for the TPC electronics

- Need to provide power to the FEMBs, provide bias voltage to the APA wires (also responsible for providing power to the field cage termination electrodes)

- Make sure that the WIECs are properly cooled down

- Make sure that there is no condensation on the flanges

- Provide detector safety

- Also ensure that the systems outside the cryostat do not spoil the excellent performance of the TPC readout electronics

- Grounding rules

# Charge (i)

- 1. Are the full specifications of the detector components, designs and complete documentations for users available in EDMS?

- 2. Does the system design address detector requirements: performance, installation, grounding, testing, calibration, commissioning, operation and maintenance? Are the impacts of detector capabilities and goals on physics performance well documented? Have design choices been fully identified and do they meet detector requirements?

- 3. Have lessons learned from ProtoDUNE been implemented both for the overall system design and for the individual design of components?

🛟 Fermilab D

# Charge (ii)

- 4. Have interfaces with other detector components (including interfaces with TPC electronics systems that have already been reviewed) been addressed and documented? Do risks of design changes in other systems have appropriate mitigation strategies?

- 5. Are engineering analyses sufficient to ensure the design is safe during all phases, and have applicable design codes and standards been satisfied?

- 6. What is the status of the procurement strategy and of the manufacturing and testing plan? Are they compatible with the current design and with meeting the detector requirements?

# Charge (iii)

- 7. Are quality assurance and testing plans sufficiently developed to proceed to final design?

- 8. Are plans for additional prototyping reasonable and sufficient?

- 9. Have appropriate cost estimates and schedule been determined? Are plans for required technical resources consistent with scope of remaining work?

## Agenda (i)

| Tuesday, 10 March 2020         |                                                                                                                                       |   |  |  |

|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|---|--|--|

| 08:00 - 08:30<br>08:30 - 08:50 | Committee closed session <i>30'</i><br>Introduction <i>20'</i><br>Speaker: Marco Verzocchi (Fermilab)                                 |   |  |  |

| 09:00 - 09:20                  | Grounding scheme 20'<br>Speaker: Linda Bagby (Fermilab)                                                                               |   |  |  |

| 09:30 - 10:00                  | Warm Interface Electronics Crate Introduction 30'<br>Speaker: Bo Yu (Brookhaven National Lab)<br>Material: Slides                     |   |  |  |

| 10:10 - 10:45                  | Experience with the WIEC, WIB, PTC in ProtoDUNE 35'<br>Speaker: Dr. Shanshan Gao (Brookhaven National Laboratory)<br>Material: Slides |   |  |  |

| 10:55 - 11:10                  | Coffee break 15'                                                                                                                      | - |  |  |

| 11:10 - 11:35                  | Intermediate WIB prototype hardware 25'<br>Speaker: Mr. Jack Fried (BNL)<br>Material: Slides                                          |   |  |  |

| 11:45 - 12:10                  | Hardware requirements for the DUNE WIB 25'<br>Speaker: Vladimir Tishchenko (BNL)<br>Material: Slides                                  |   |  |  |

| 12:20 - 13:10                  | Lunch <i>50'</i>                                                                                                                      | - |  |  |

🛠 Fermilab 🕬

## Agenda (ii)

| 12:20 - 13:10 | Lunch <i>50'</i>                                                                                                                             | - |

|---------------|----------------------------------------------------------------------------------------------------------------------------------------------|---|

| 13:10 - 14:25 | WIB firmware and software requirements 1h15'<br>Speakers: Joshua Klein (University of Pennsylvania), Joshua Klein<br>Material: <b>Slides</b> |   |

| 14:40 - 15:00 | Changes to the PTC 20'<br>Speaker: Marco Verzocchi (Fermilab)<br>Material: Slides                                                            |   |

| 15:10 - 15:30 | Coffee break 20'                                                                                                                             | - |

| 15:30 - 15:55 | Interface with the FEMBs and the ASICs 25'<br>Speaker: David Christian (Fermilab)<br>Material: Slides                                        |   |

| 16:05 - 16:35 | WIB firmware and software development plans 30'<br>Speaker: Dr. Hucheng Chen (Brookhaven National Lab)<br>Material: Slides                   |   |

| 16:45 - 17:30 | Committee closed session 45'                                                                                                                 | - |

| 18:00 - 20:00 | Dinner 2h0'                                                                                                                                  |   |

|               |                                                                                                                                              |   |

## Agenda (iii)

#### Wednesday, 11 March 2020

| 08:00 - 08:30 | Design of the bias voltage and low voltage power supply plant and cable plant 30'<br>Speaker: Marco Verzocchi (Fermilab) | • |

|---------------|--------------------------------------------------------------------------------------------------------------------------|---|

| 08:40 - 09:05 | Interface to slow controls and interlocks 25'<br>Speaker: Marco Verzocchi (Fermilab)<br>Material: Slides                 |   |

| 09:15 - 09:40 | Timeline, production and QC plans <i>25'</i><br>Speaker: Marco Verzocchi (Fermilab)                                      | • |

| 09:45 - 10:30 | Reserved for additional presentations / Time for Q&A 45'                                                                 | - |

| 10:30 - 10:45 | Coffee break 15'                                                                                                         | - |

| 10:45 - 12:15 | Committee closed session 1h30'                                                                                           | - |

| 12:15 - 13:00 | Lunch 45'                                                                                                                | - |

| 13:00 - 16:00 | Committee closed session 3h0'                                                                                            | - |

| 16:00 - 17:00 | Closeout 1h0'                                                                                                            |   |

- 1) Linda Bagby: Grounding

- Enforcing grounding rules is necessary in order to achieve the noise goals of experiment (ENC << 1000 e<sup>-</sup>)

- You can have a wonderful FE amplifier, but if your grounding scheme doesn't work, you will never see that

- Grounding rules developed based on experience with similar systems (including ATLAS LAr calorimeter)

- Already proven in ProtoDUNE

- Not going to make any changes

- Some tests (connections of cable shields) done at ProtoDUNE

- TPC electronics is not the problem, convincing the other consortia to follow the rules during design / implementation is the tough part

- 2) Bo Yu: introduction to the warm interface crate (WIEC)

- Description of the WIEC with all its parts (flange, fans, filter boards)

- Design will have minimal changes relative to ProtoDUNE

- Bo mentions it only in the last slide, we will change connectors on the flange (use fewer lines between WIB and FEMBs, see David Christian's presentation)

- Adding filters to fan system to clean up air used to cool down WIBs

- Hard to predict what the environment will be in the cavern, air filters are clearly going to be needed, will not be able to make measurements of air quality in the DUNE cavern until 2024 (or even 2025

🛟 Fermilab 🛛 🖸

Small change to filter cards to accommodate monitoring of current on ground plane of high voltage system

- 3) Shanshan Gao: lessons learned from ProtoDUNE

- More details on the hardware

- Other uses of the WIB (interface for ASICs/FEMBs testing)

- Quality control on WIBs

- WIB firmware: a tale of two versions

- Having 2 versions of firmware was an historical artifact, try to avoid this in the future

- One particular feature useful for debugging not available in the main firmware release

- Cannot rely on overcommitted group for all of FW development, need to build a team

🛟 Fermilab 🖸

## **New WIB hardware / firmware**

- ProtoDUNE WIB uses a fairly expensive and outdated FPGA

- This alone would be reason for change

- Not compatible with FEMBs with COLDATA or CRYO

- Need to adapt firmware and hardware (power distribution)

- Two plans

- Develop intermediate WIB based on lessons learned from ProtoDUNE, using cheaper FPGA (reduce cost)

- More flexibility in FEMB powering, more monitoring, more modern FPGA with Zynq CPU

- Develop detailed list of hardware / firmware requirements

- Will use hardware requirements for evolution of intermediate WIB toward DUNE

- Will use requirements document to develop new firmware that will be used first on intermediate WIB and later on DUNE WIB

🛠 Fermilab 🕞 🖯

- 4) Jack Fried: detailed description of intermediate WIB design

- 5) Vladimir Tishchenko: hardware requirements for the new WIB

- 6) Josh Klein: firmware requirements for the intermediate and new WIB

- The new WIB is here (2 prototypes in hand, need to fabricate more)

- Development of firmware requirements has taken much longer than planned, document needs to be reviewed by entire team and digested by engineer who will be leading firmware development

- Hardware requirement document for DUNE WIB at version 1, some aspects need to be expanded (FEMB power requirements, interface to PTC)

- 7) Marco Verzocchi: changes to the PTD

- We've realized that we need to change the PTC for 2 reasons

- Increase monitoring / control on power distribution from LV supplies to WIB

- Provide interface to the DUNE detector safety system (DDSS: interlocks)

- Late realization (early February), no design for DDSS

- Currently just a conceptual design, but not too implausible for the interface with DDSS

- 8) David Christian: interface WIB/FEMB

- Discuss more detail about synchronization between DUNE clock, WIB, and FEMB

- Discuss connections between WIB and FEMB for three ASIC solution (LArASIC, ColdADC, COLDATA) and for CRYO ASIC solution (single ASIC)

- Topics were left out of ASICs/FEMBs review at beginning of February

- 9) Hucheng Chen: WIB FW/SW development plans

- This is the area where we are clearly lagging behind

- For system tests in Summer 2020 we may perform more work inside the Zynq CPU than we would really like to, to ensure that we complete system tests in a timely fashion

- Slides of Hucheng discuss the need for an organization for firmware development

- 2 institutions mentioned in the slides (BNL, Penn)

- Other institutions willing to help with firmware development (leading engineer may come from one of the additional institutions)

- Clearly we are not where other experiments are for their PDR on firmware

- But we also have firmware prototype from ProtoDUNE that demonstrates that developing such firmware is not unfeasible

- Main issue is ensuring long term support / documentation

- 10)-12) Marco Verzocchi: 3 presentations on

- Bias voltage and power supplies

- Interface to DDSS

- Timeline, production and QC plan

- First two presentations have some overlap (also with PTC presentation)

- Suffer from lack of definition of slow control and DDSS

- Told about transition to OPC Unified Architecture in mid-February

- Have to fully understand consequences for the design of the fans and heaters power supplies

🛟 Fermilab D

- No design in DUNE for DDSS

- Have to make reasonable assumptions on how the system will work

- Areas least defined for the project, but also not as complicated as the WIB

## **Documentation in EDMS (i)**

Please let me know as soon as possible if you have problems accessing it (requires CERN account)

#### **Technical Documentation**

Grounding

- LBNF/DUNE grounding rules

- Detector grounding rules

- Grounding diagrams

ProtoDUNE mechanical designs:

- Mechanical assembly of the WIEC

- Mechanical assembly of the cold electronics flange and of the WIEC

🛟 Fermilab 🖸

ProtoDUNE printed circuit boards:

- · Printed circuit board for the Cold Electronics flange

- Warm Interface Board and Power and Timing Backplane

- Power and Timing Card

DUNE Prototypes printed circuit boards

First DUNE Warm Interface Board prototype

## **Documentation in EDMS (ii)**

Please let me know as soon as possible if you have problems accessing it (requires CERN account)

#### **Technical Documentation**

Cable and Wire Documentation

- · Bias voltage cables (used for APA wire bias and field cage termination electrodes)

- ProtoDUNE cold control, clock, and readout cable

- ProtoDUNE power cable

- · AWG24 wire for field cage termination board fall-back ground connection

- · Warm power cable between low voltage supplies and PTCs

- · Warm bias voltage cables (used for APA wire bias and field cage termination electrodes)

- · Complete list of TPC electronics cold and warm cables

- · Naming convention for TPC electronics cables

Requirement documents

· WIB requirements (hardware and firmware)

Chapter of the DUNE SP Technical Design Report (contains: chapter 1, overall introduction to the single phase TPC far detector module; part of chapter 4, description of the TPC electronics; plus the glossary and the references; 29 MB file, 19+61+23+16 pages)

Interface Documents

- With the DAQ/SC consortium

- · With the JT HV consortium

- · With the PDS consortium (not yet ready for review)

Other Interface Documents