## UH\_Q-Pix\_OSC\_Review

Gang Liu University of Hawaii

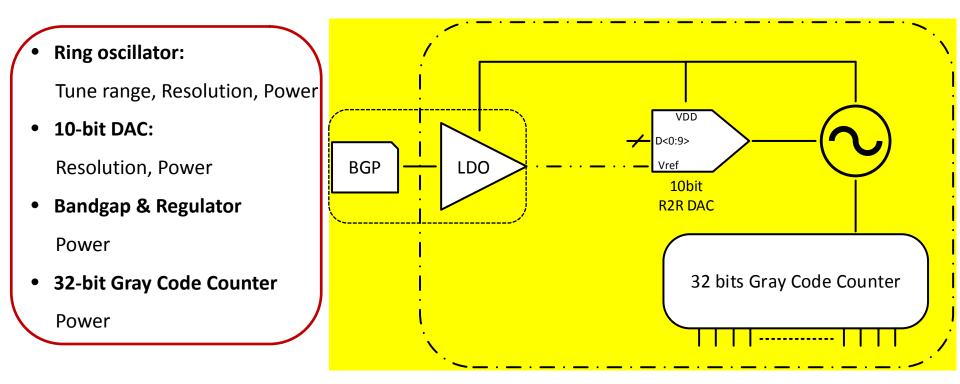

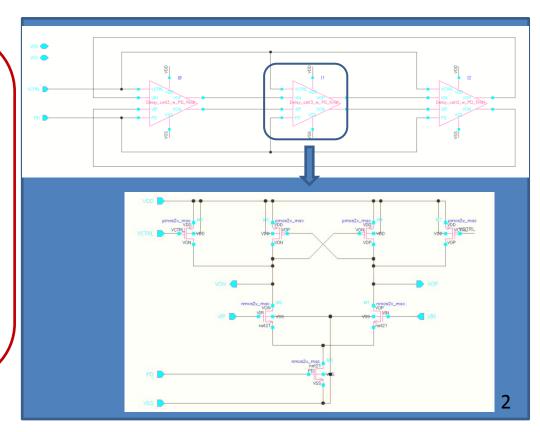

# **Oscillator Overview**

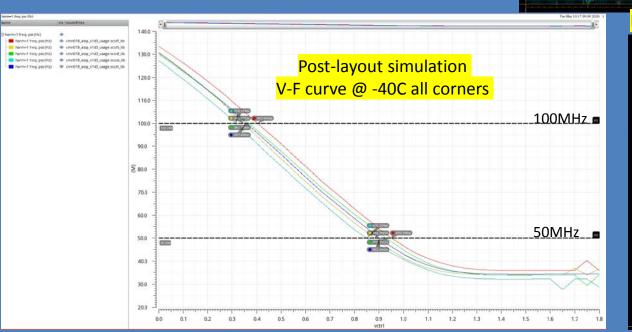

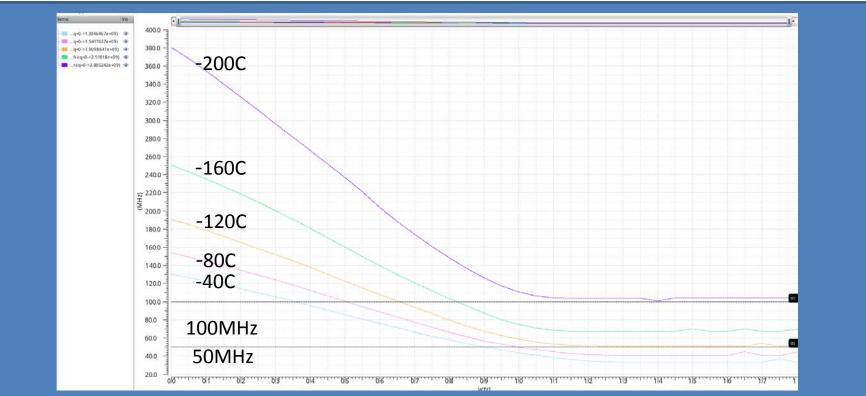

- Tune range: 50MHz ~ 100MHz

- Target resolution: 1%

- Large transistor

- Limited range and gain

- Simple structure and less component

- Differential and no bias delay cell simple, good common mode noise rejection

- Power-down mode

Turn off to test the analog performance

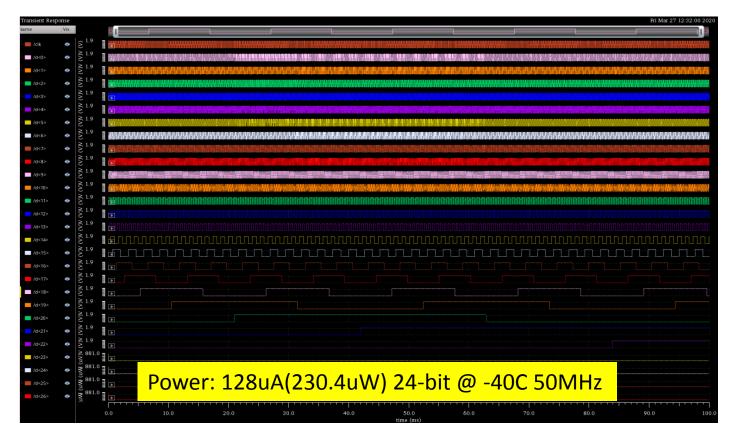

Power: 201.3uA (0.36mW) @ 50MHz -40C typical

- R2R structure, low power consumption

- Based on 1-bit DAC, cascade to 10 bit

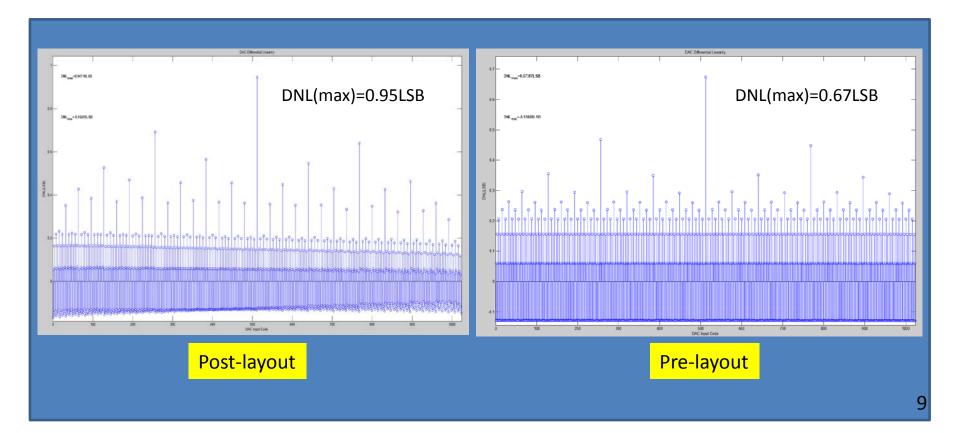

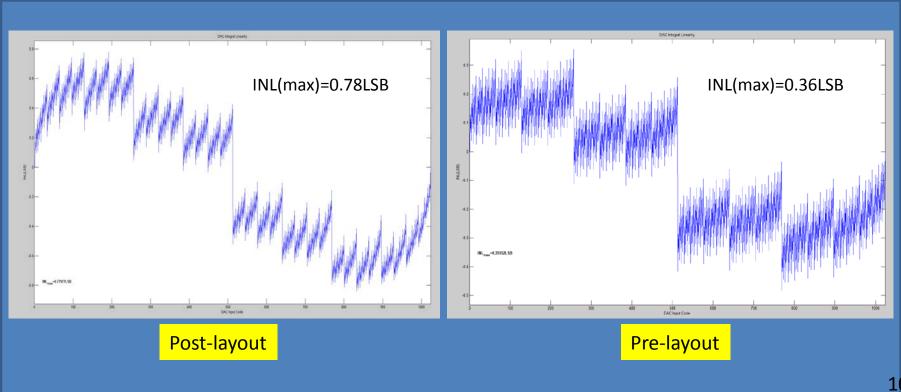

- Worst case happens in the middle of the range, when all the input digits flip.

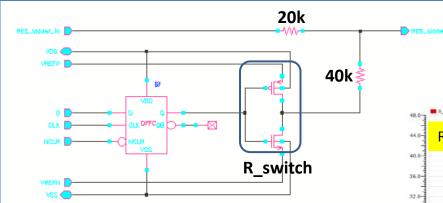

- Two relatively large resistors are chosen to ignore the resistance of the switch.

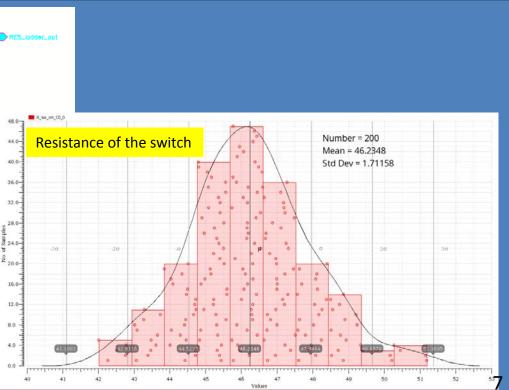

- R\_switch= 46.2ohm, only 0.12% of 40k, could be ignored.

10

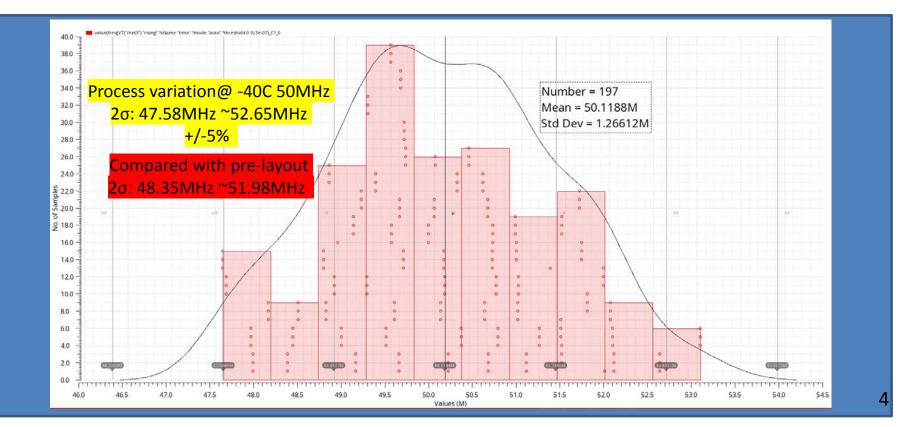

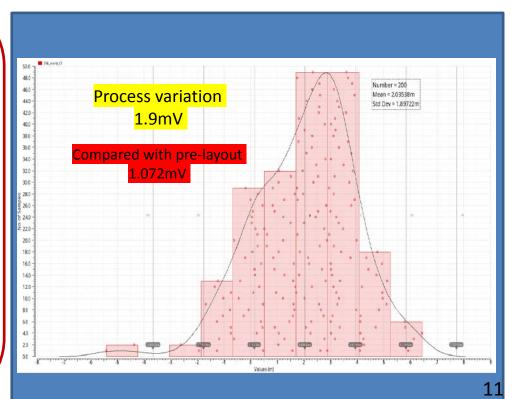

#### **Process variation**

- Run monte carlo simulation for the worst case. input=011111111, 100000000, 100000001

- Measure the two steps difference

- The Std Dev is 1.90mV.

- For a 10-bit 1.8V DAC, 1LSB=1.8/1024=1.76mV

- In the worse case 1.90mV could be added to the worst case of DNL

- That's 1.90mV + 1.67mV(0.95LSB)=3.57mV

- 9-bit DAC, 1LSB=3.52mV 8-bit DAC,1LSB=7.03mV

- Worst case 3.52mV<3.57mV<7.03mV, so we still have a 8-bit DAC

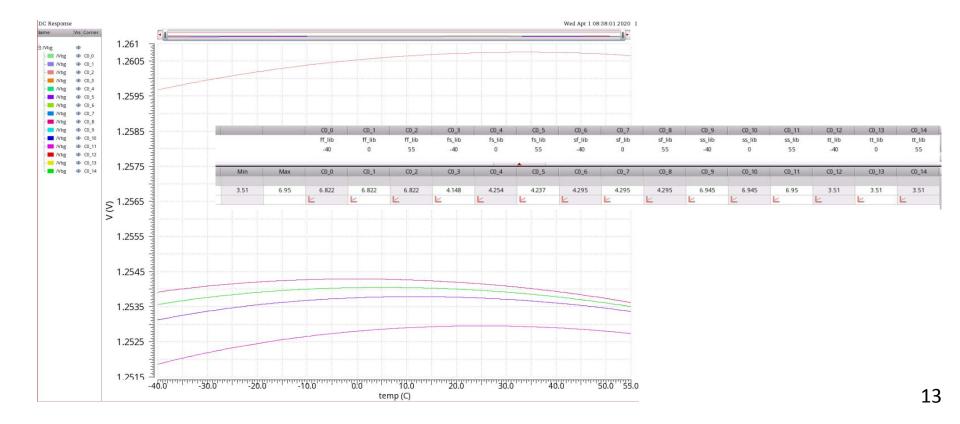

# Bandgap

- First-order temperature compensation

- -40C to 55C temperature coefficient < 7ppm

- Power: 0.34mW @ -40C

### Bandgap

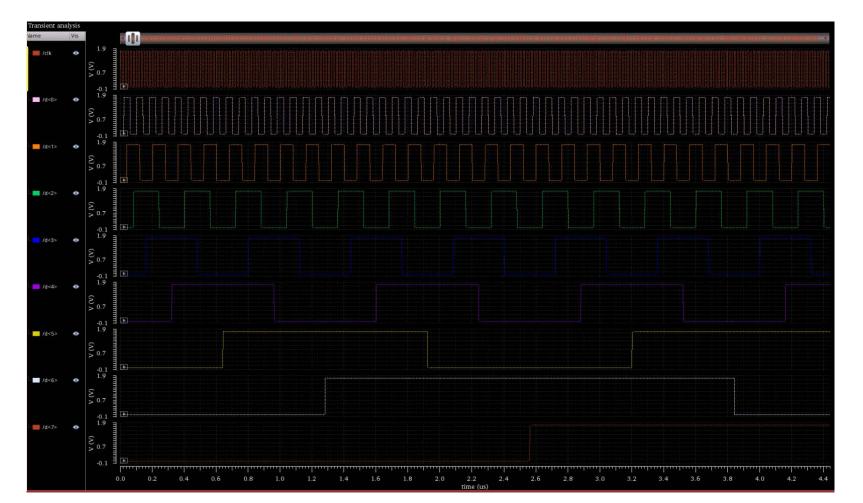

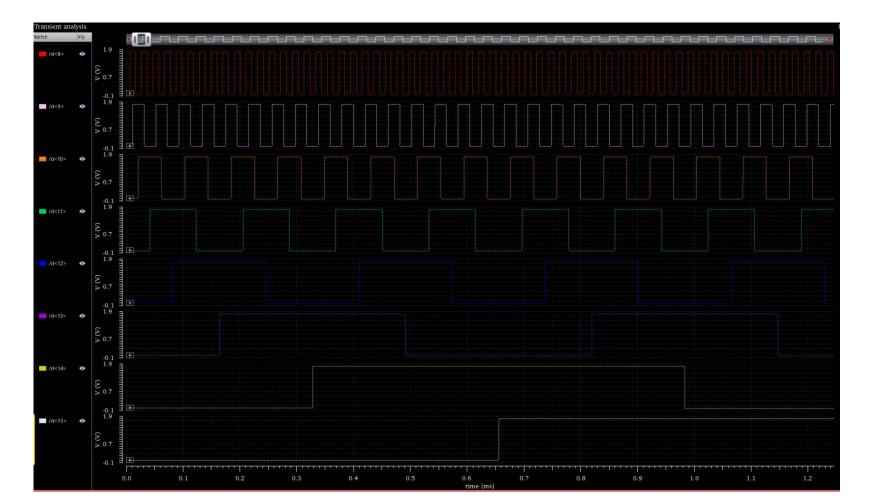

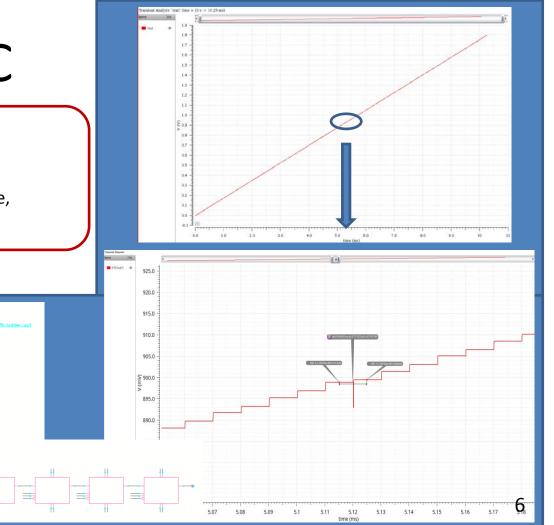

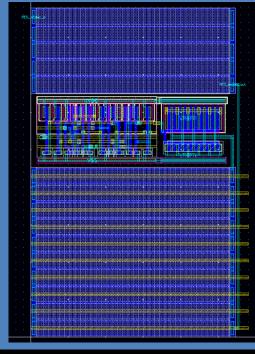

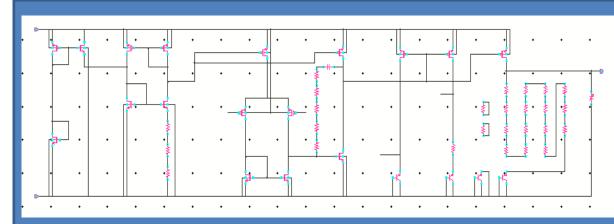

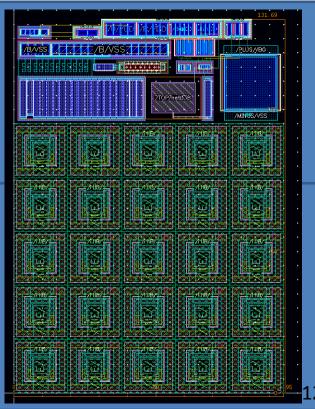

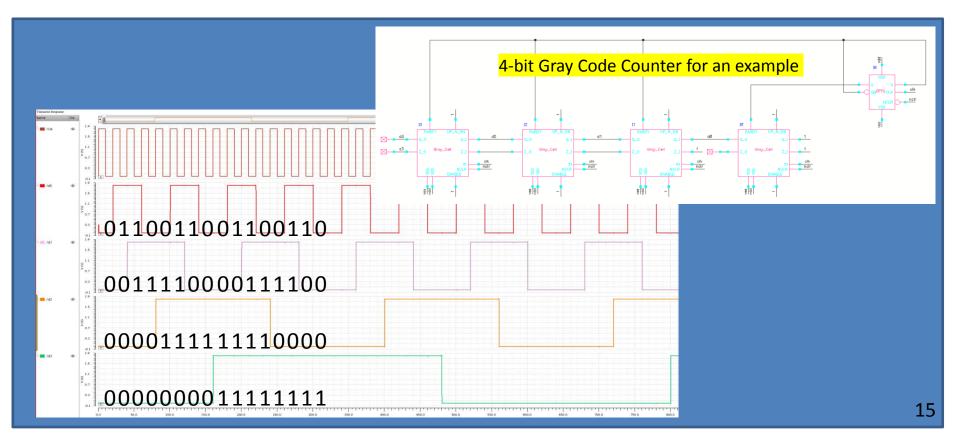

## 32-bit Gray Code Counter

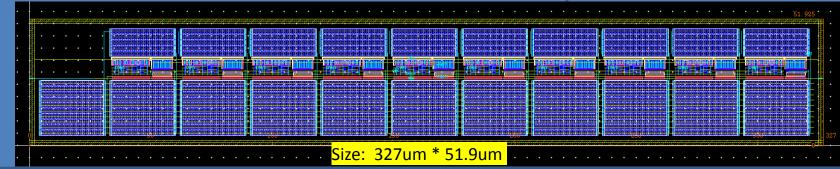

- 1-bit GCC schematic & layout

- Could be cascaded to 32 bit

- Need a reset signal after one counting cycle

- Custom designed std cell

Cascaded 32-bit GCC

Size: 945.9um \* 17.8um

#### 32-bit Gray Code Counter

#### 32-bit Gray Code Counter