## **CPAD Instrumentation Frontier Meeting 2016 Trigger & Data Acquisition**

## **SLAC Roadmap**

Ryan Herbst Department Head, Advanced Electronics Systems

(rherbst@slac.stanford.edu)

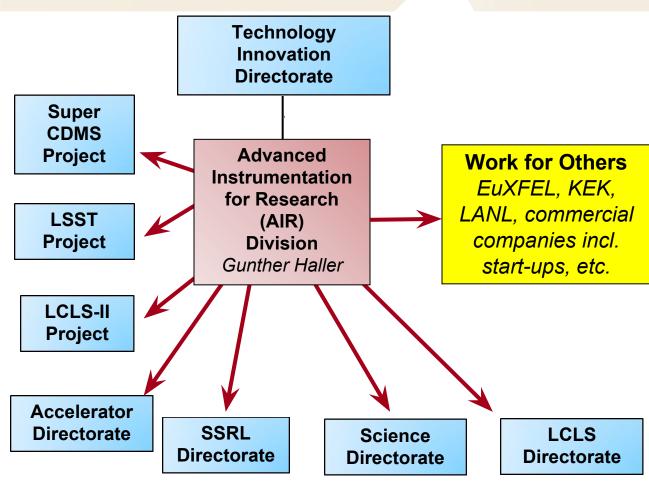

#### SLAC TID-AIR

Technology Innovation Directorate

Advanced Instrumentation for Research Division

#### **Overview of SLAC Structure**

-SLAC

LCLS-II John Galayda, Project Director

LSST Steve Kahn, Project Director

SuperCDMS SNOLAB Blas Cabrera, Project Director

Chi-Chang Kao Laboratory Director

Norbert Holtkamp Deputy Director

Accelerator Lia Merminga Associate Lab Director LCLS Mike Dunne Associate Lab Director Science Chi-Chang Kao Associate Lab Director SSRL Kelly Gaffney Associate Lab Director Technology Innovation Michael Fazio Associate Lab Director

Biosciences, Chemical Science, Computer Science Elementary Particle Physics, High Energy Density Science Material Science, Particle Astrophysics & Cosmology

Fermi-GLAST Gamma-Ray Telescope

Business & Operations

## SLAC's Core Instrumentation R&D Capability in AIR provides Systems & Components for SLAC & National/International Projects

- Provides engineering for SLAC directorates

- All SLAC developed LCLS/LCLS-II detectors

- HEP: ATLAS, CDMS, HPS, etc.

- LSST, CMB, Fermi ...

- Non-SLAC Projects

LSST: World's largest digital camera

### **High Density / High Performance Processing In ATCA**

High performance platform with 9 clustered processing elements (SOC)

Dual core ARM A-9 processor

1GB DDR3 memory

Large FPGA fabric with numerous DSP processing elements

Data processing daughter board with dual Zyng 045 FPGAs (modular for camera integration)

Application specific RTM for experiment interfaces 96 High Speed bi-dir links to SOCs

On board 10G Ethernet switch with 10G to each processing FPGA Supports 14 slot full mesh backplane interconnect!

Deployed in numerous experiments

- LSST

- Heavy Photon Search, LDMX

- **DUNE**

- **ATLAS Muon**

- **KOTO**

- ITK Development

Front panel Ethernet 2 x 4, 10-GE SFP+

SOC platform combines stable base firmware / sw with application specific cores

- HLS for C++ based algorithms & compression

- Matlab for RF processing

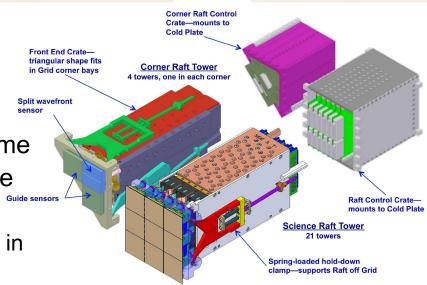

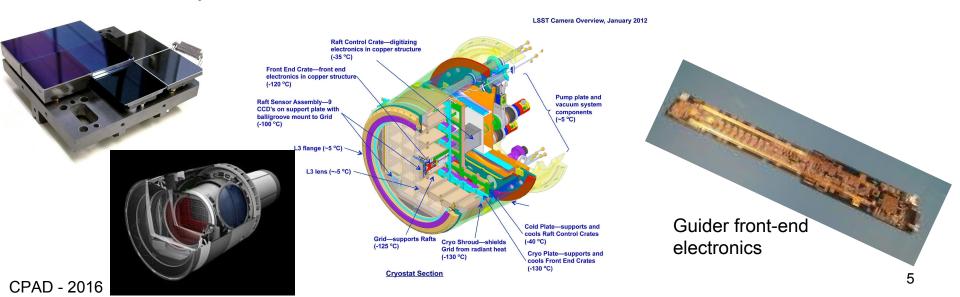

## **LSST Camera Development**

- Overall lead of electrical / electronics engineering

- Development of high-performance guiding electronics system

- Development of low-latency, high data-volume data acquisition system hardware & software

- SLAC ATCA RCE Platform

- Includes data-processing & 3 day data cache in flash memory

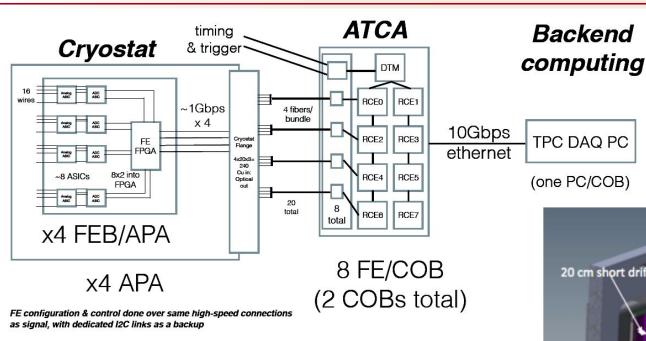

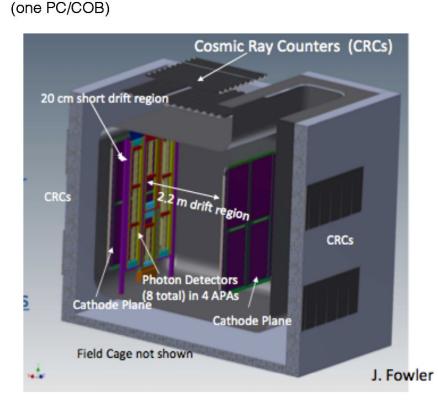

#### **DUNE 35-Ton**

- SI AC RCE Platform is readout for 35Ton detector.

- Fully integrated with timing system

- Integrated with ARTDAQ backend system

- Successful deployment of zero suppression algorithm

- Written in C++ via Vivado HLS design flow

- Support for 128 channels with 25% FPGA utilization

- Fully adjustable to optimize performance depending on S/N conditions

- Successful handling of data quality issues Noisy front end data links Cold ASIC stuck bit problem

Backend

TPC DAQ PC

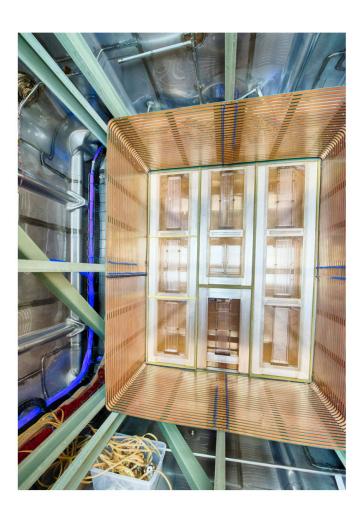

#### **ProtoDUNE & DUNE**

- Single phase detector data acquisition

- Data path processing of 256 channels per RCE

- 2048 channels per COB

Possible to grow to 384 channels

- Compression algorithm written in C++ via Vivado HLS

- Dynamic compression table for each channel using channel specific statistics

- Algorithmic Probability Encoding

- Best lossless compression without manual tuning

- Remaining FPGA processing power can be used to remove correlated noise

- Fully integrated timing system for reliable start, stop and triggering

- Moving toward full integration of ArtDAQ board reader software

- Moving from external PC to RCE ARM processor

- Hardware offload of data path using SLAC RSSI protocol

- Looking forward to full DUNE detector

- Optimize channel processing density

- DAQ platform upgrade & cost reduction

- Proposal for RCE based NOVA trigger contribution (J. Russell)

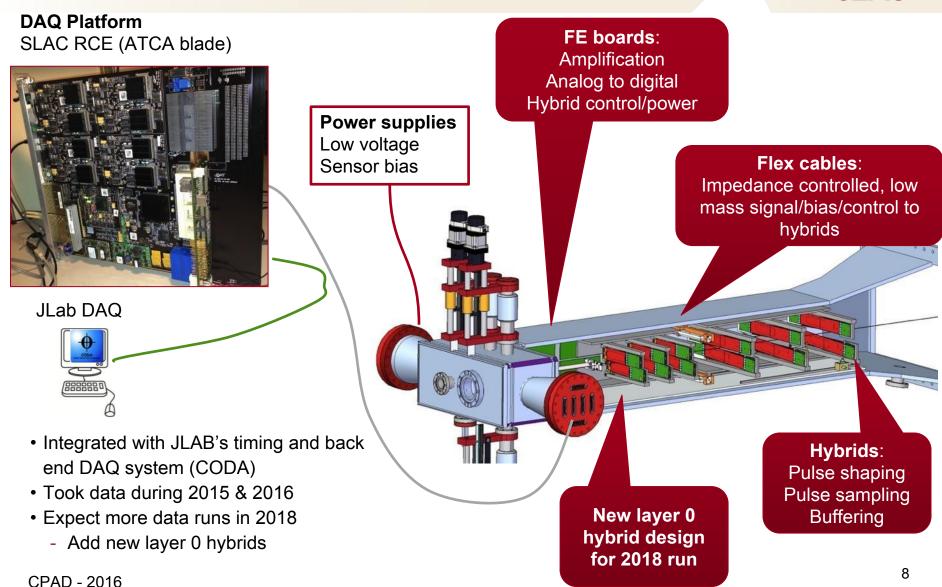

## **Heavy Photon Search**

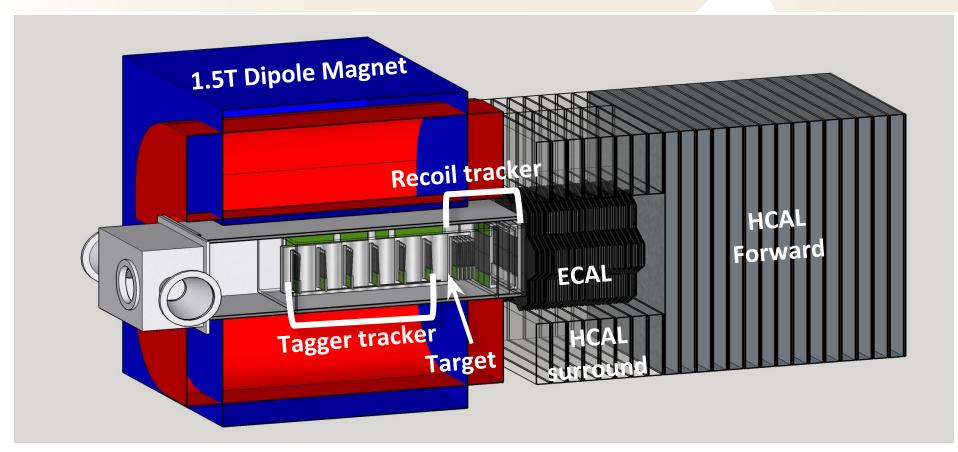

#### **LDMX**

- Light Dark Matter Experiment planned for End Station A

- Uses residual dark current available in LCLS-2

- Low energy electrons which exist between 1Mhz primary beam pulses

- SLAC providing tagger tracker (HPS clone) and facility DAQ

- Back end DAQ, event building, online analysis and offline storage based upon LCLS-2 DAQ

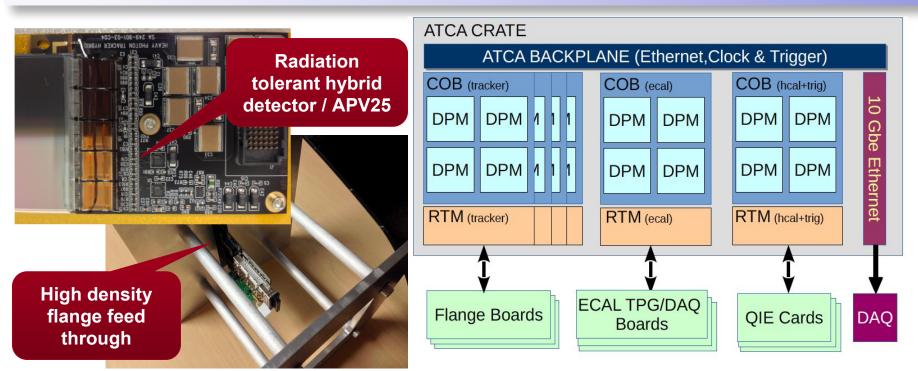

#### **LDMX Electronics & DAQ**

#### SLAC

- Common off-detector electronics system based on the RCE platform developed at SLAC

- System is powerful enough to implement the trigger, timing distribution, DAQ, and controls in one ATCA crate

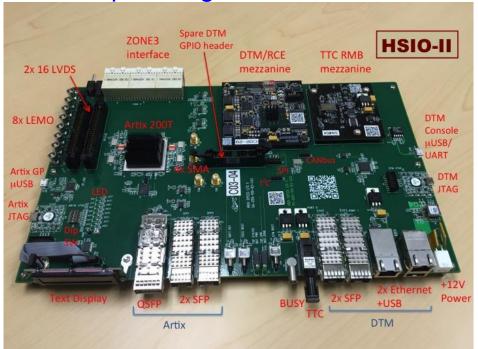

### **ATLAS ITK Readout Test Systems with HSIO+RCE**

SLAC

- Compact bench-top test stand multi-channel readout with RCE mezzanine

- Zynq Z030 based RCE + Artix FPGA for both gate logic and CPU

- Varieties of I/O banks: SFP/QSFP/LVDS/SMA/USB/LEMO, Ethernet ports and TTC interface. Further extended user I/O via zone 3 interface.

- Boot-up management with flash and remote control J-tag

- Previous version of HSIO served critical IBL Q/A and commissioning readout and many ATLAS strip and pixel upgrade test stands and test beams worldwide (~50 boards)

- Current HSIO-II version with 40+ boards for 9 US and 23 international (1 CMS) institutions and systems.

A validated and evolved concept through extensive real applications

## **HSIO & RCE GBT Integration**

TID-AIR SLAC

- RMB module available to support GBT communications

- Plug in module to HSIO

- Provides reference clock for all RCEs within a COB

- The VLDB is a test board with a GBTx chip and 20 e-links on HDMI connectors.

- Available from CERN.

- GBT firmware is available for the Xilinx Kintex.

- Build an RCE test system for FEI4 chips using the GBT protocol.

- Implementation directly on the RCE's Zynq rather than on the Artix on the HSIO because the Zynq has Kintex-like MGTs (GTX).

- Moved pixel firmware from Artix to Zynq.

- Connection via optical fiber (SFP).

- Next step is to port GBT firmware to the Artix FPGA fabric to run natively on the HSIO

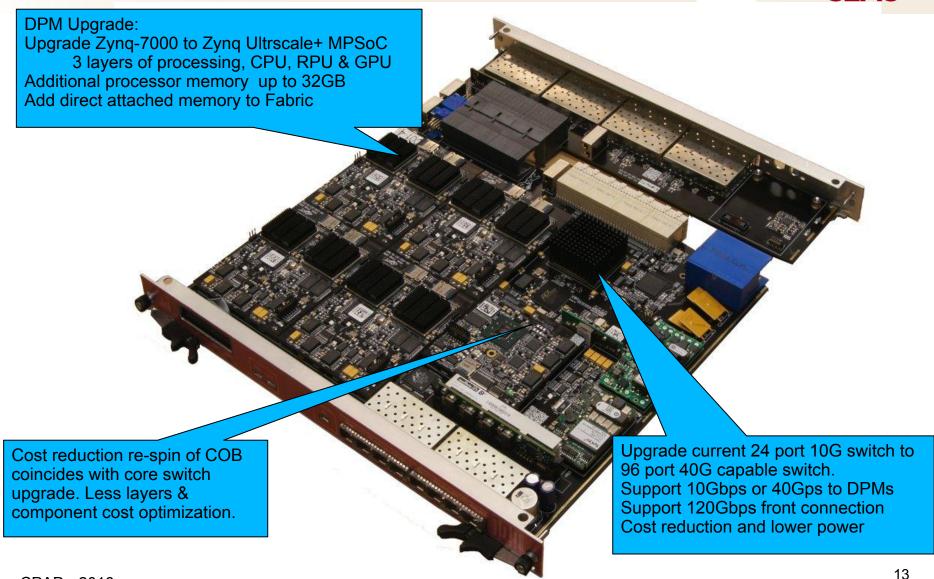

## **Planned Upgrades To RCE Platform**

**CPAD - 2016**

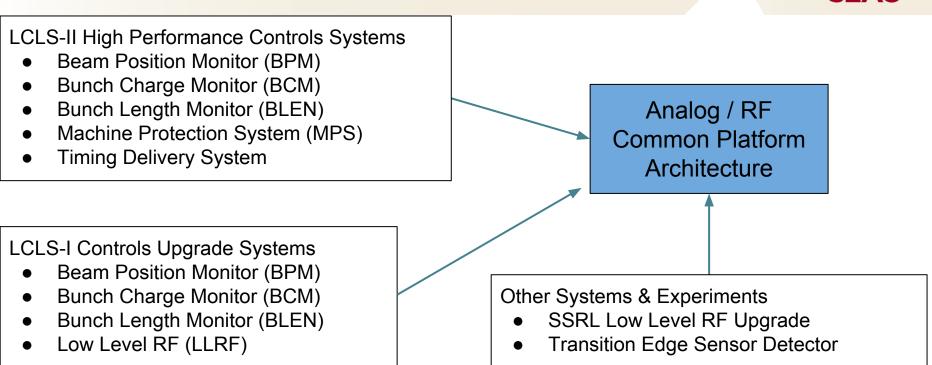

## SLAC LCLS-2 High Performance Accelerator Controls RF Detectors

TID-AIR SLAC

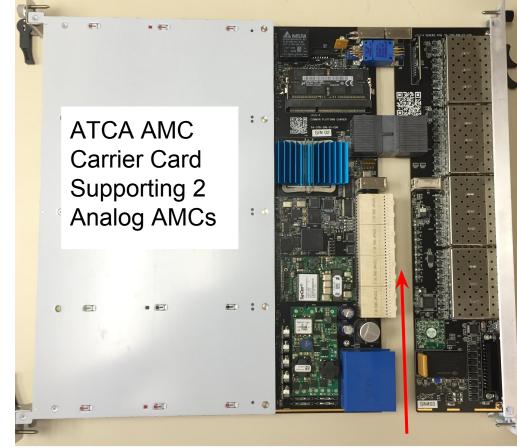

- TID-AIR developed an ATCA based common platform for accelerator controls

- LCLS-2, LCLS-1 and SSRL

- Combines high performance digital processing with low noise RF design

# ATCA Based Platform For LCLS-I & LCLS-II High Performance Controls

TID-AIR SLAC

#### LCLS-1 LLRF Down Convert

ATCA provides the space, power & cooling required for LCLS-2!

LCSL-2 BPM board

10/40Gbps Ethernet Backplane

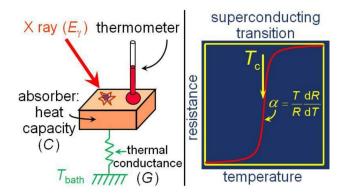

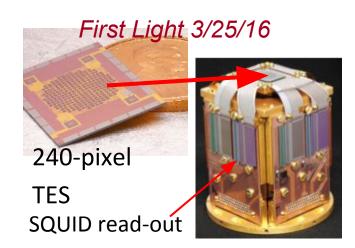

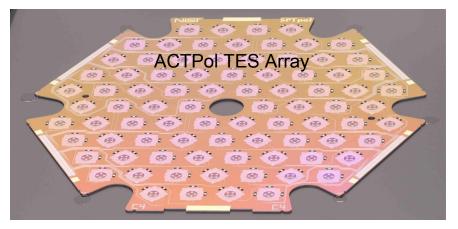

## **Superconducting Devices for Cosmology**

- Seeking signs of cosmic inflation

- Measure polarization of cosmic microwave background

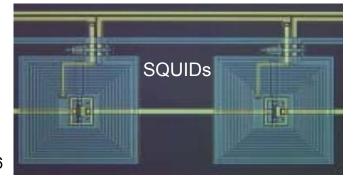

- Use Superconducting Quantum Interference Devices (SQUIDs)

- Transition-Edge Sensors (TES)

- Unprecedented sensitivity and energy resolution

- Megapixel arrays possible with spectroscopy on every pixel

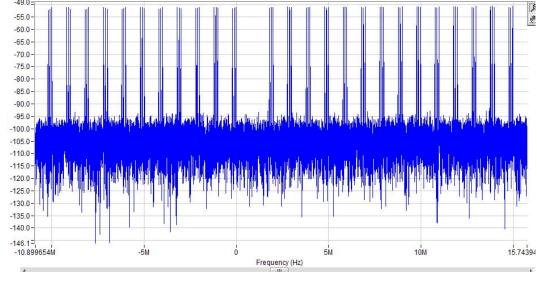

#### **TES Readout Electronics**

- Each TES element is coupled to a superconducting resonator with a SQUID that results in a resonant frequency dependent on current

- Continuous current ramp induces sinusoidal frequency driver

- TES sensor current modifies the frequency vs ramp current

- "Comb" of frequencies sent down to TES array

- Triplett of frequencies per TES sensor

- One below and above resonant frequency for reference

- ATCA based readout electronics generates comb of frequencies

- 1 at TES resonant point (dip in received frequency)

- 2 sideband frequencies for reference

- Design goal of 4K channels per FPGA

- 12K total tx and rx frequencies (resonant plus 2 reference)

**CPAD - 2016**

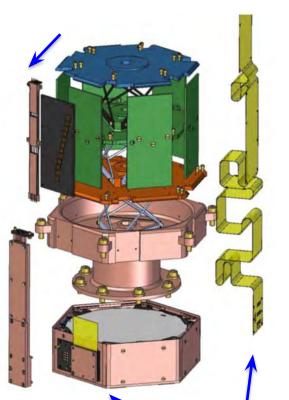

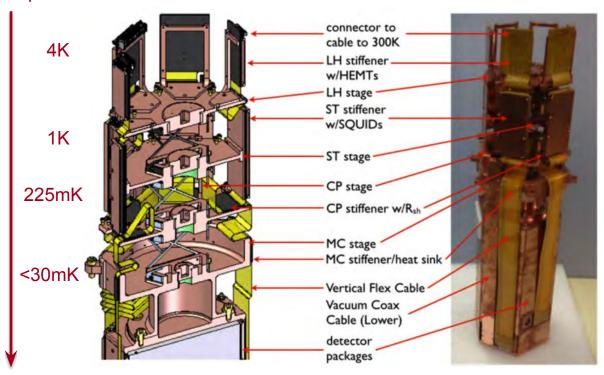

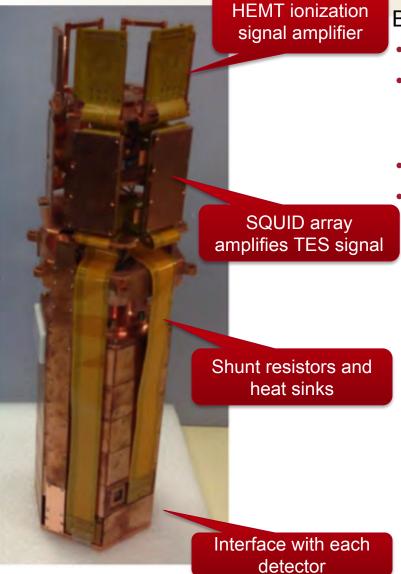

#### **SuperCDMS Detector Tower Overview**

SLAC

TID-AIR responsible for tower cold electronics and 4K->300K readout wiring

- ⇒ Detect and amplify phonon and ionization signals in ultra-pure Ge/Si detectors

- → Tight requirements on radiopurity for all materials!

#### Tensioned NbTi wire cables

#### **Temperature**

Six Ge/Si detectors/tower operating at <30mK!

Superconducting flex cables CPAD - 2016

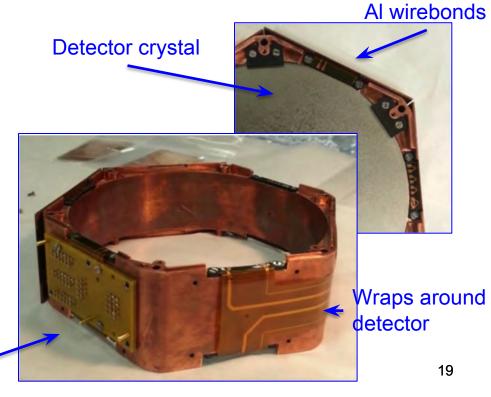

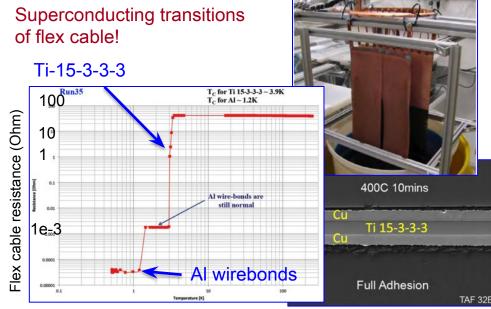

## **Superconducting Horizontal Flex Cable**

#### SLAC

#### Connects from detector wirebonds to vertical flex cable

- Superconducting traces (tin-copper) to minimize resistance

- Short run for ionization signals

- Low inductance for phonon signals

- LEDs for neutralizing

ionization traps in crystal

Rigid board connects to

vertical flex cable

## **Superconducting Vertical Flex Cable**

Backbone of tower cold electronics

- Integrated cable with multiple rigid boards

- Challenging Titanium-based superconducting traces (Ti15-3-3-3-> NbTi); critical to minimize thermal load

- Low inductance for TES signal (phonon channels)

Exotic small signal/low noise amplifiers (HEMT transistors, SQUIDs)

Cu plating+annealing

20

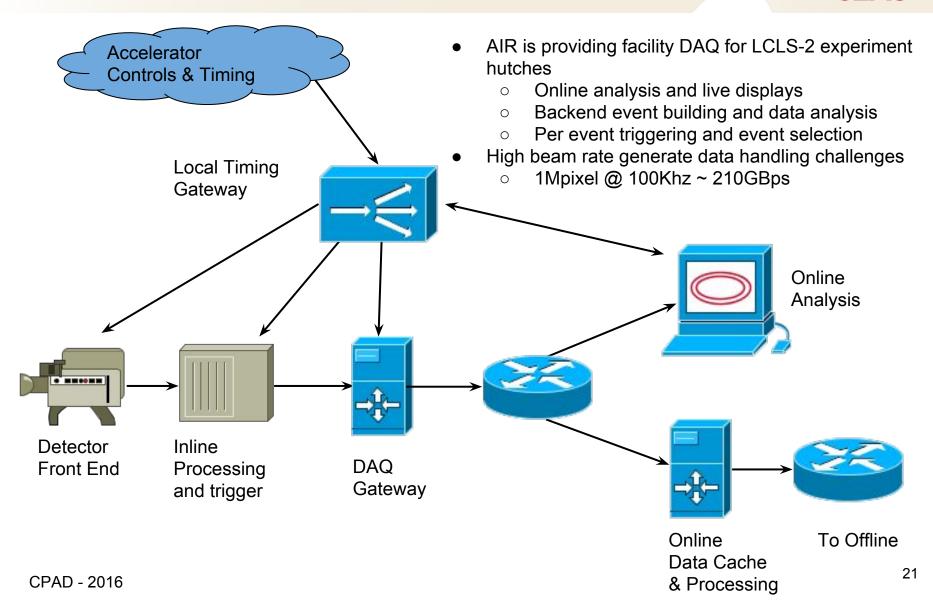

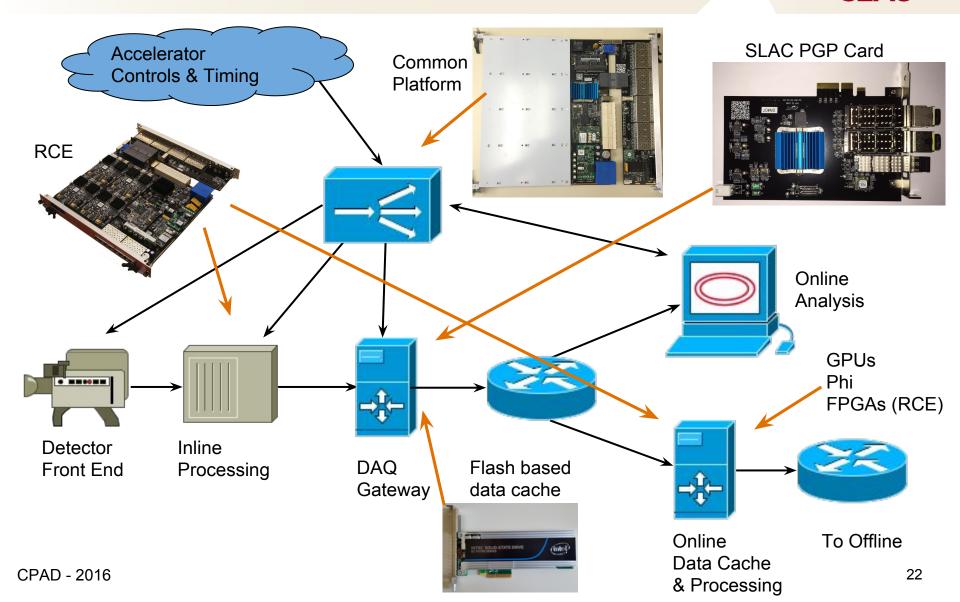

### **LCLS-2 Data Acquisition**

## **LCLS-2 Data Acquisition**

### **SLAC PCI-Express Generic DAQ Interface Card**

Dual QUAD SFPs for 8 lanes of up to 6.125Gbps (upgrade to 12Gbps)

- Optical interface supports a number of detector protocols

- o PGP (SLAC)

- Aurora

- CameraLink

- Raw Ethernet

- User Custom!

LCLS-1 or LCLS-2 Timing Interface

- PCI-Express card supports bi-directional links to camera front end

- Hardware handles protocol layers to reduce CPU loading

- Supports bi-direction timing interface supporting busy and trigger feedback

- Timing receiver firmware built into FPGA

- Timestamp and trigger forwarded down optical link with PGP

- Timestamp applied directly on camera

- Round trip latency measurements and adustment

- Firmware can also apply trigger on incoming data

- Gate event acceptance based upon event code / trigger information

- Most SLAC detectors uses SLAC developed PGP2 protocol

- High bandwidth data transport from camera to DAQ

- Supports timing and trigger delivery to front ends

CPAD - 2016 23

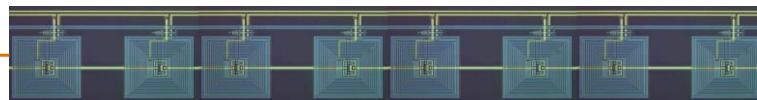

## **AIR Integrated Circuits**

Develop Application Specific Integrated Circuits (ASIC)

•10+ ASIC designers

For any application, the following slides concentrate on:

- The processing of signals from detectors

- The control of detectors

- SLAC SACI protocol for SPI like control

- 8B10B and 10B12B cores for 1Gbps streaming data readout

#### Areas of expertise:

- mixed-signal architectures

- low noise analog front end

- noise filtering optimization

- high speed, mixed mode blocks

- ADC's, DAC's

- high-speed digital data transmission

Some of the technologies

Variety of vendors (TSMC, IBM, L-Foundry, AMC, setc: 250nm to 65nm technologies

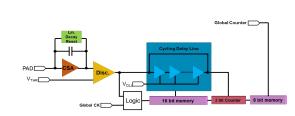

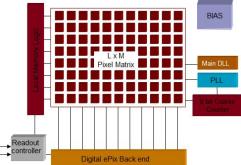

tPix a spatial and time resolving pixel Front-end ASIC

|                   | tPix                     |

|-------------------|--------------------------|

| Mode of Operation | Time of Arrival + ToT    |

| Pixel Size (µm)   | 100 x 100                |

| ' (1 /            | 352 x 384<br>(2x2 ASICs) |

| iming resolution  | ~ 100ps / 1ns            |

| Time depth        | 1µs / 10µs               |

## **FGPA SERDES Diagnostics And Tuning**

SLAC

- DCP interface to FPGA serializers allows full dynamic reconfiguration and monitoring of SERDES

- Monitor eye diagrams for link diagnostics

- Reconfigure operating mode

- No need to IP core gen for every application

- Drop down generic VHDL module with default mode and reconfigure as needed

- We currently use this to switch between LCLS-1 and LCLS-2 timing modes on our internal receiver

- Console based eye diagram testing with Microblaze:

| Lane0 ES with 715 pixels: |  | Lane1 ES with 715 pixels: |  |

|---------------------------|--|---------------------------|--|

|                           |  |                           |  |

|                           |  |                           |  |

|                           |  |                           |  |

|                           |  |                           |  |

|                           |  |                           |  |

|                           |  |                           |  |

|                           |  |                           |  |

|                           |  |                           |  |

|                           |  |                           |  |

|                           |  |                           |  |

|                           |  |                           |  |

**CPAD - 2016**

## **Additional Areas Of Development**

SLAC

- RSSI (Reliable SLAC Streaming Interface)

- Reliable layer on top of UDP for FGPA-FPGA and FPGA-SW interfaces

- Allows firmware to firmware intercommunication for distributed data processing

- Integration with our PCI-Express board host protocol offload

- BSP (Board Support Package) software layer auto inferring from VHDL firmware

- Adding hooks to register definition procedures in VHDL to generate Python code describing register space in parallel to RTL definition

- BSP can be output of FPGA build process.

- Eliminates errors when translating register space to software

- Quick prototyping

- Putting the DNA in the hardware

- Python code generated from VHDL can be integrated into FPGA image

- Compressed file next to bitfile image

- Generic software can learn the hardware and auto populate the BSP upon connection

- Plug and play detectors and front end boards

- Reliable boot loader for failsafe image download

- BIOS like initial boot and jump to application image

CPAD - 2016 26

## The End

CPAD - 2016 27