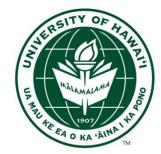

### Hawaii Group Activities

Gary S. Varner University of Hawai'i

HEP 2017

# **Supporting the Discovery Frontier**

Development Overview (SCA/WFS centric)

- Current Deployments

- LABRADOR (UHE v searches)

- IRS (ARA and Belle II TOP)

- TARGET (Belle II KLM, CTA)

- Completing development

- GRAPH for space applications (low-noise CSA+WFS)

- CTA production versions (CT5TEA + CTAC)

- Evolving Directions (commercialization):

- 1. On-chip Feature extraction: ASoC (System on Chip)

- 2. High density: Si-READ (64 channels, low-cost)

- 3. Precision timing: RFpix (details tomorrow)

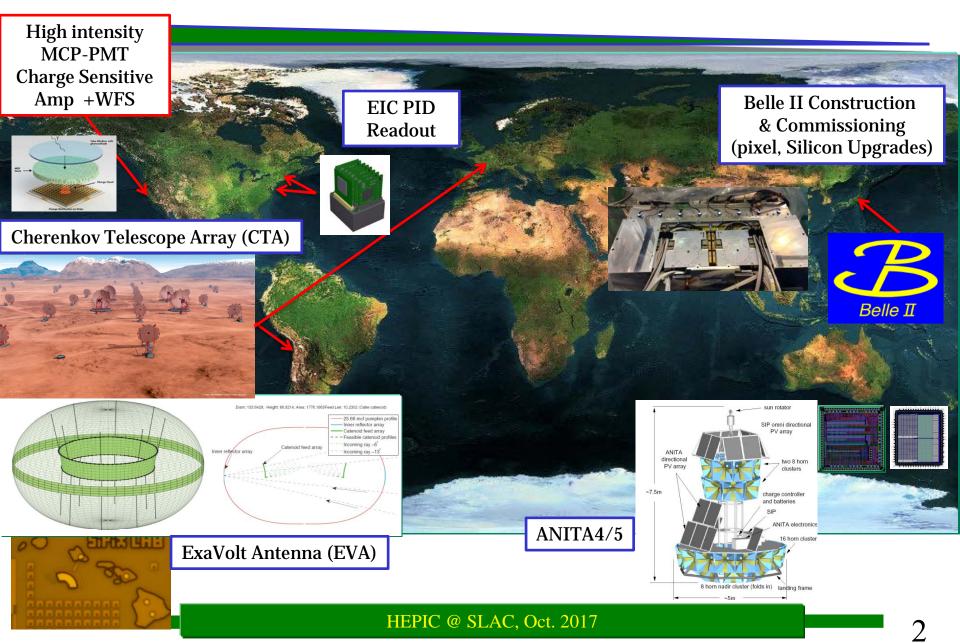

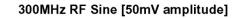

### Switched Capacitor Array Sampling

# **Basic Functional components**

# A Very Challenging Design

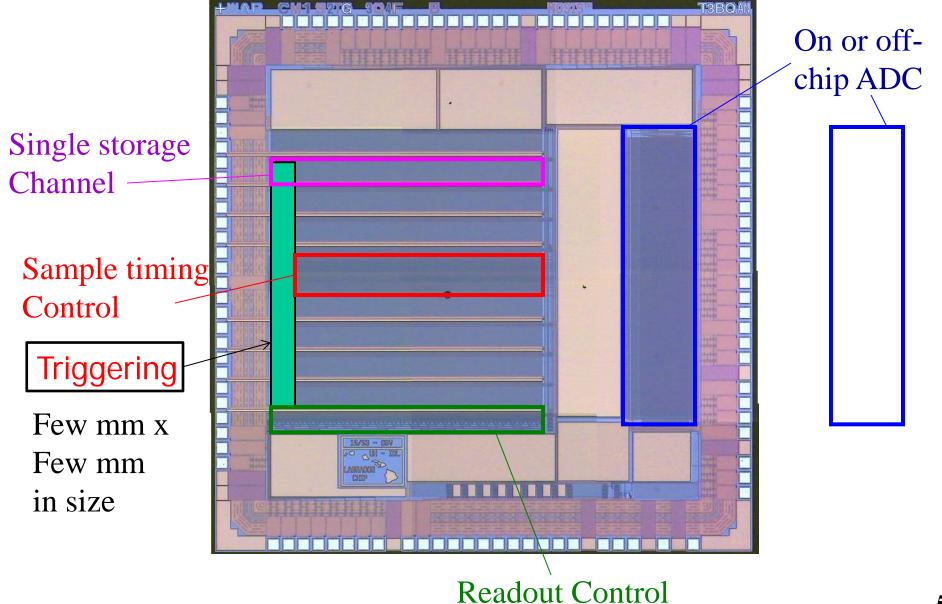

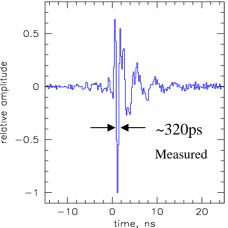

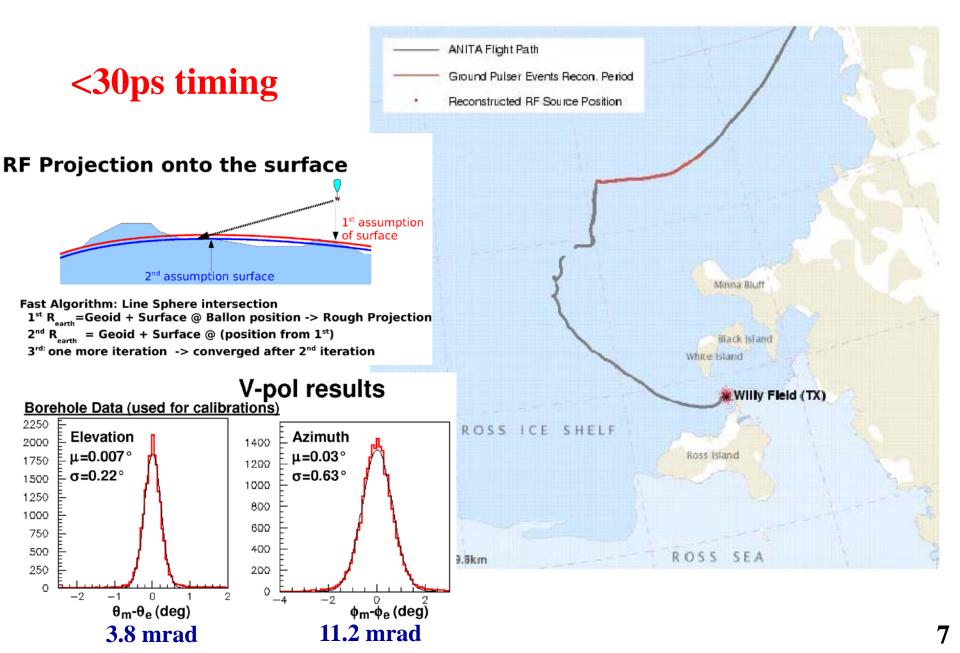

#### A radio "feedhorn array" for the Antarctica Continent

- Quad-ridged horn antennas provide superb impulse response & bandwidth (200-1200 MHz)

- Interferometry & beam gradiometry from multiple overlapped antenna measurements

### Demonstrated performance -- Not just in the lab

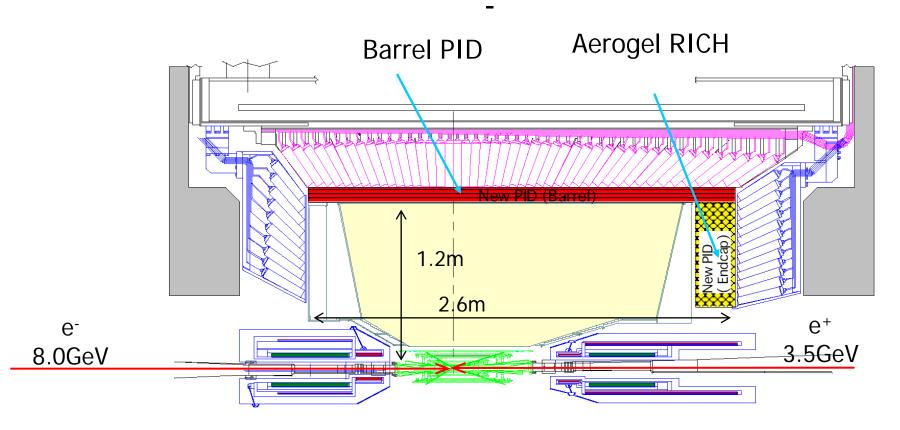

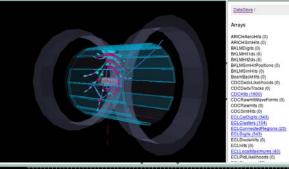

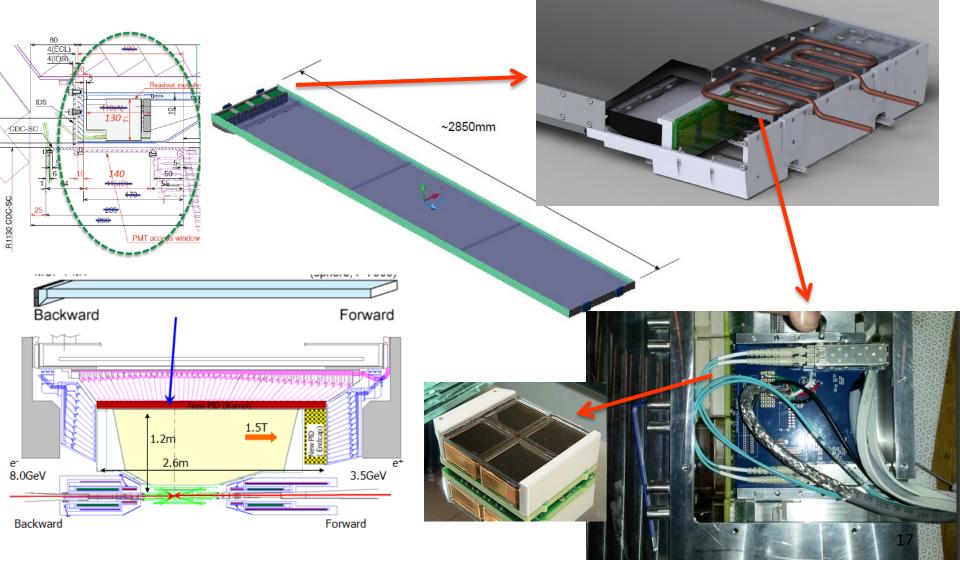

### Upgraded Belle detector

- PID (π/K) detectors

- Inside current calorimeter

- Use less material and allow more tracking volume

→ Available geometry defines form factor

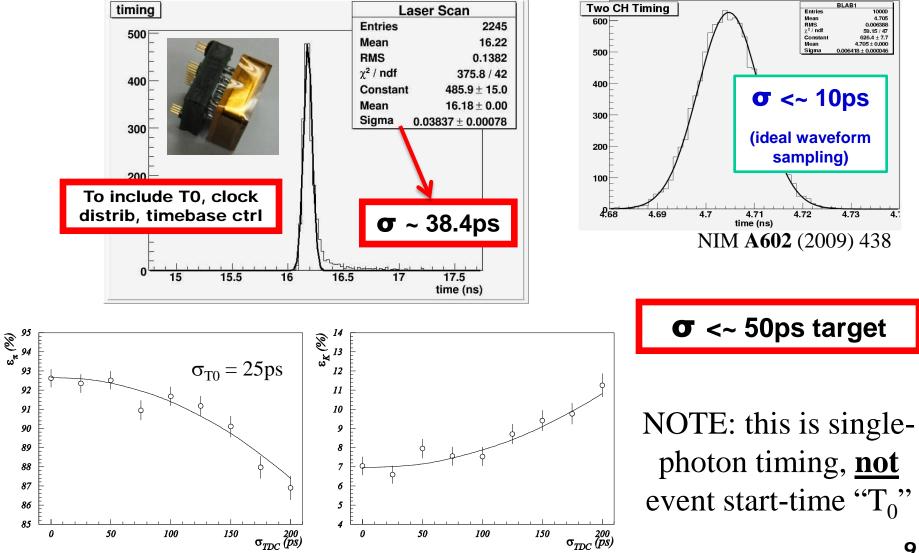

# Single photon detection for TOP

Single photon timing for MCP-PMTs

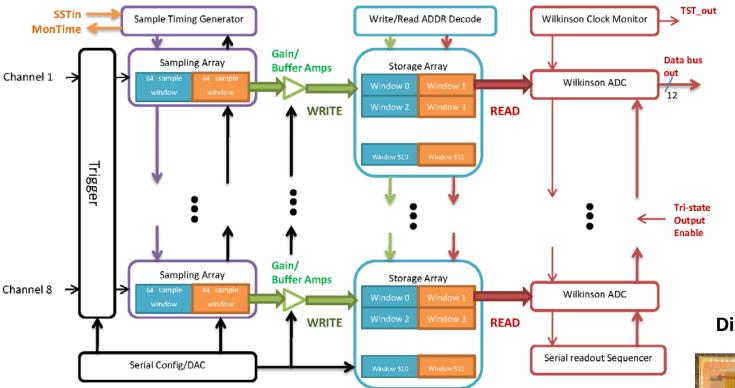

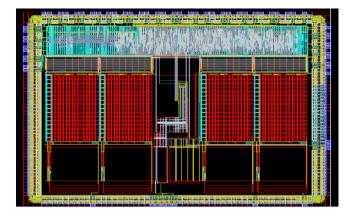

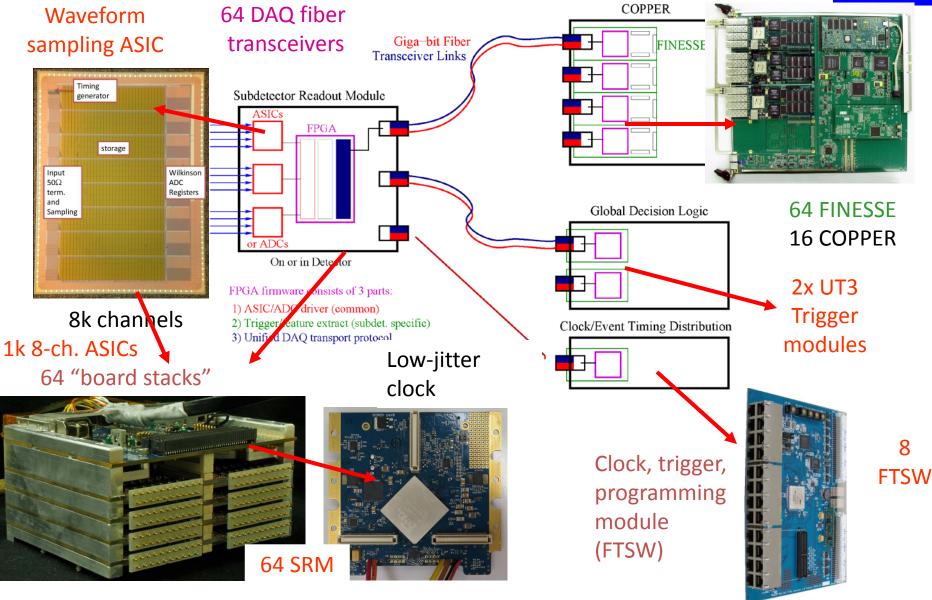

### **IRS family ASIC Overview**

- 8 channels per chip @ 2.8 GSa/s

- Samples stored, 12-bit digitized in groups of 64

- 32k samples per channel (11.6us at 2.8GSa/s)

- Compact ASICs implementation:

- Trigger comparator and thresholding on chip

- On chip ADC

- Multi-hit buffering

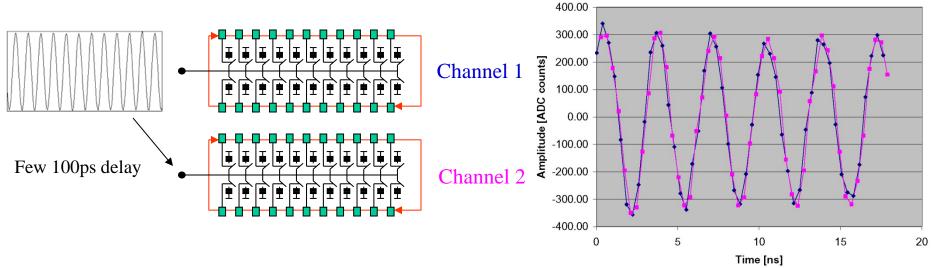

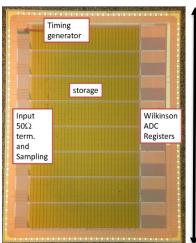

#### **Die Photograph**

8mm

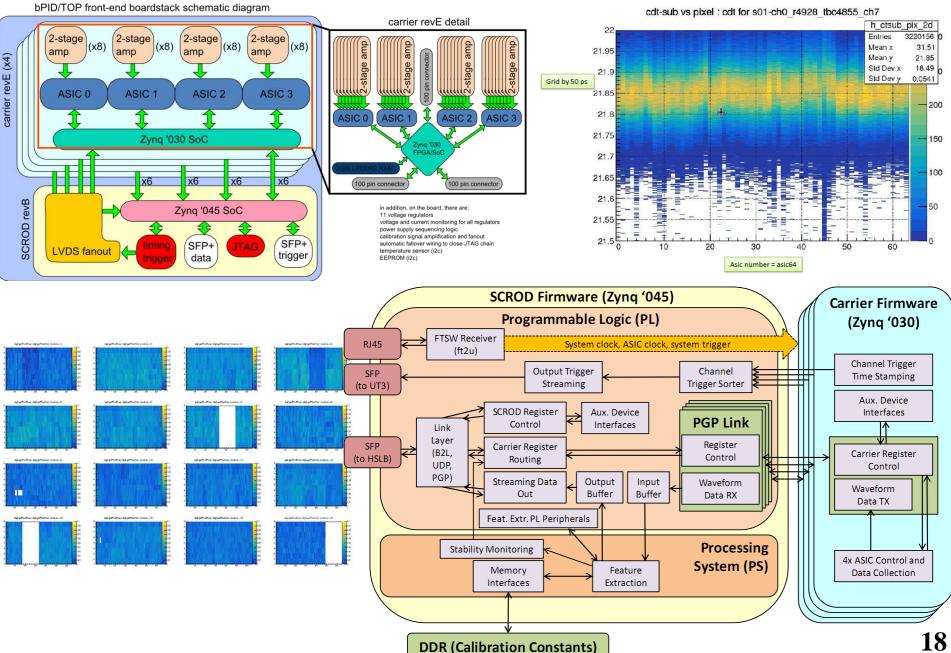

# ITOP Readout "boardstack" (1 of 4 per TOP Module)

Belle-II iTOF

030021 REV

SCROD

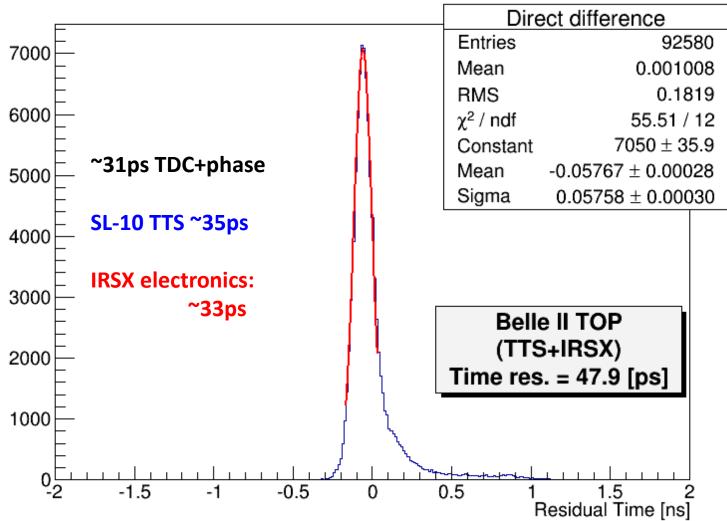

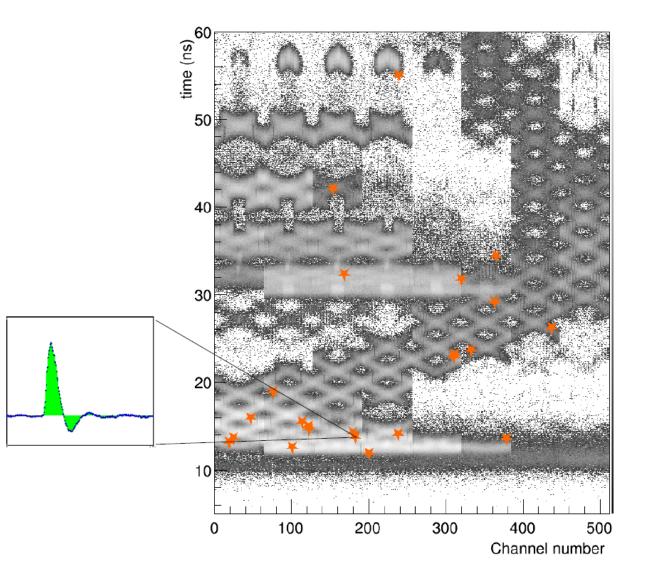

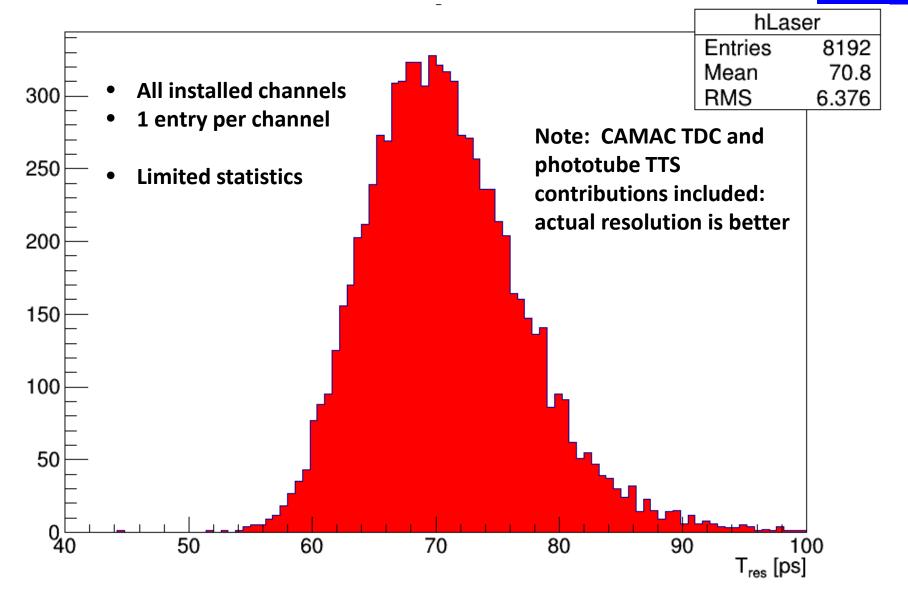

# Production single photon testing

Laser timing: laser\_pixel3\_0\_gain4\_HV3201\_18may2015

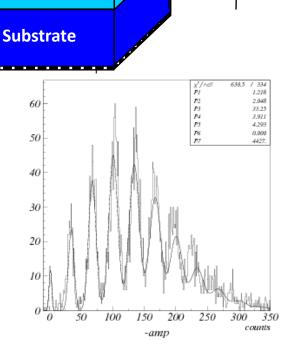

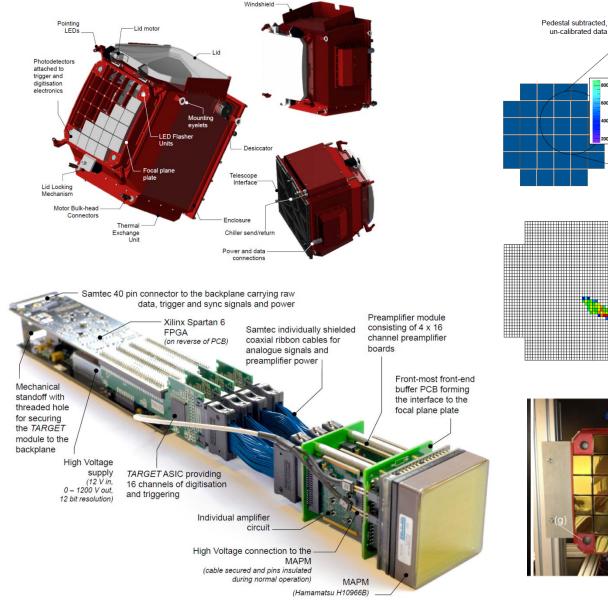

# TARGET technology

Depletion Region

2 µm

- Highly pixelated readout

- 20,000 channels Belle II Muon system readout

hν

Belle T

- 16 channels

- 0.5-1.2 GSa/s

- 10-12-bit digitization

- Samples stored, digitized in groups of 32

- 16k samples per channel (16us at 1GSa/s)

- Integrated triggering capability

500kHz – 2MHz dark rate not a problem: 5 p.e. threshold reduces rate to < 1kHz while maintaining > 99% MIP efficiency

### **Performance Reference**

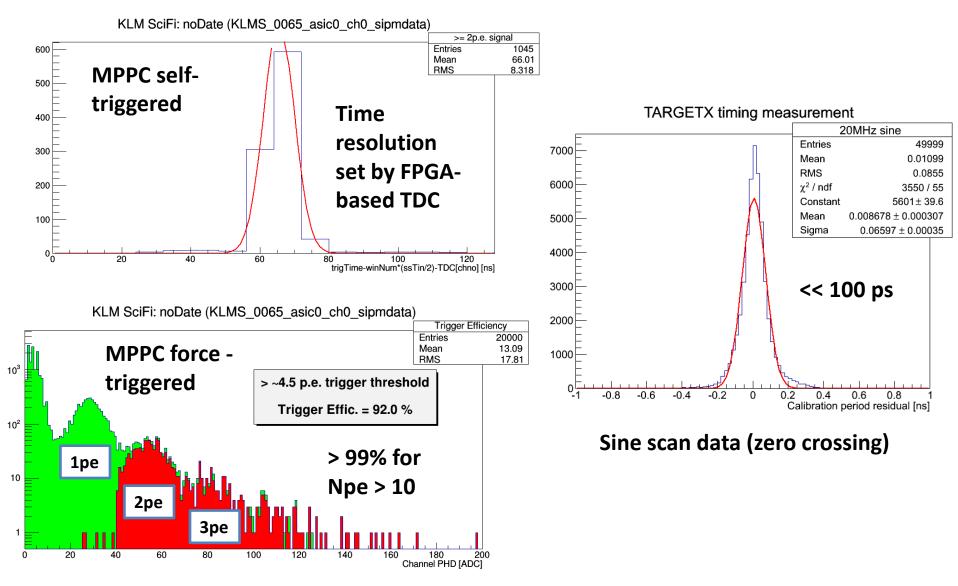

# **TARGET** family Synopsis

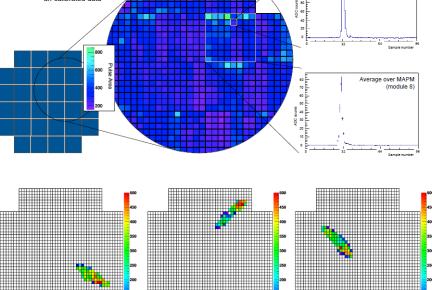

- ~21000 channels of TARGETX deployed for Belle II K-long and Muon system scintillator upgrade

- Each CTA camera 2048 channels

- 256k storage cells per ASIC (>300 million tested)

- 16 channel density attractive for compact sensor arrays (e.g. high-density DIRC ...)

- 64 channel version (SiREAD) in design

- Engineering run quantities: \$1.40/channel (ADC and trigger on-chip)

- While not for precision timing, < 100ps</li>

### Looking back on >10 year development

• ASIC costing well understood, very competitive!

NIM A591 (2008) 534-345.

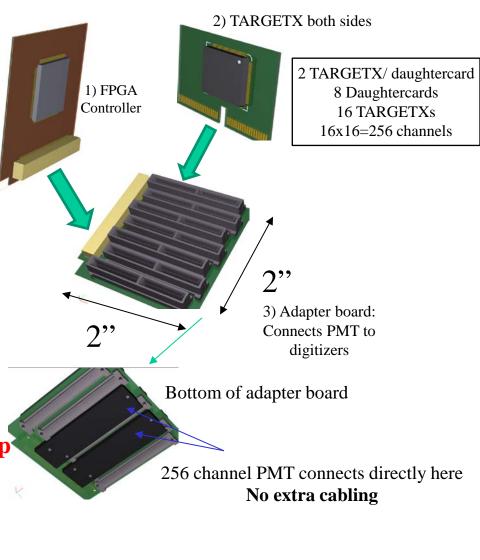

# GCT Camera (CTA) – TARGET ASIC

Single pixel (289)

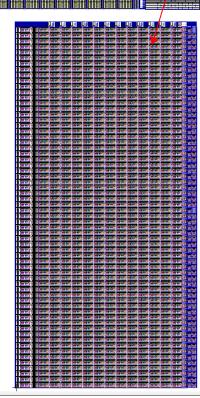

### Biggest challenge: Firmware complexity

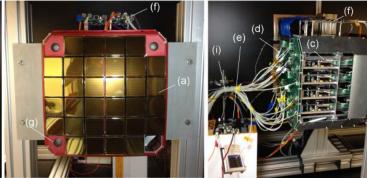

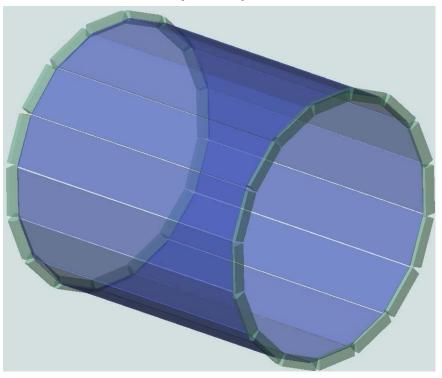

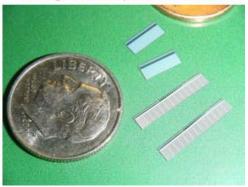

# One example: modular RICH readout

#### **Challenge:**

Readout of compact H13700 MCP-PMT Compact and dense: 256 channels in 2"x2" Timing resolution: ~100ps Long buffer Abutted Photosensors Likely convert to SiPM array later Minimize analog cabling

#### **Solution:**

1<sup>st</sup> gen prototype based on existing TARGETX ASIC:

1GSa/s full waveform sampling 16 us trigger buffer 16 channels Self triggering capability

Low cost 250nm CMOS Upgrade to 64-channel SiREAD chip

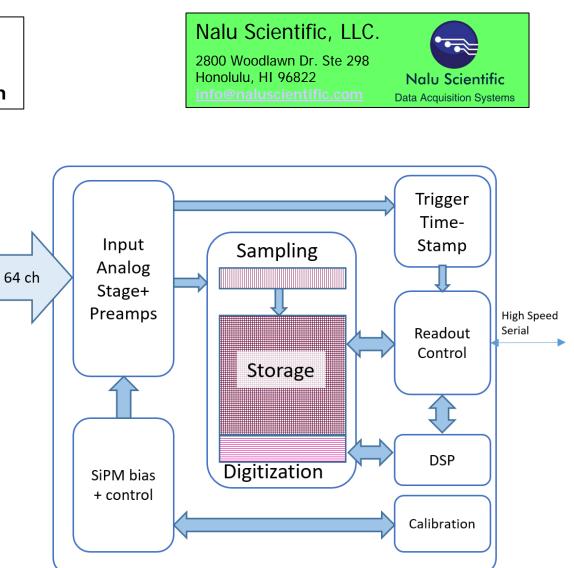

### SiREAD in more detail

#### Siread

Silicon photomultiplier REadout, Automated calibration and Detection

| SiREAD Parameter     | Specifications |

|----------------------|----------------|

| Channels             | 64             |

| Sampling rate        | 1-4 GSa/s      |

| Storage samples/ch   | 4096           |

| Analog bandwidth     | 0.7-1.1 GHz    |

| RMS voltage noise    | <1mV           |

| Dynamic range        | 10-11 bits     |

| Signal voltage range | 2.1 V          |

| ADC on chip          | 12 bits        |

| Readout              | Serial LVDS    |

| Power consumption    | 20-40 mW/ch    |

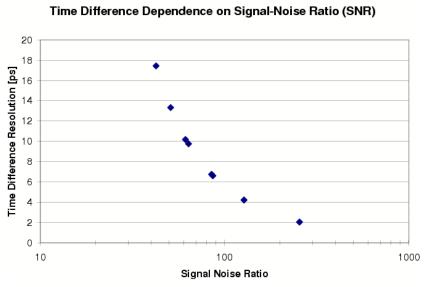

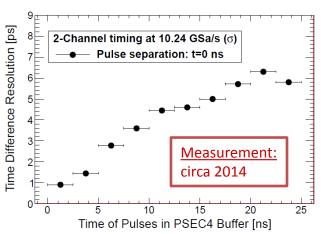

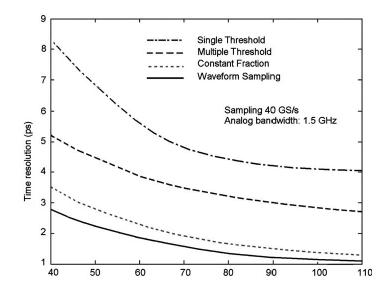

# Technology has room to improve

#### 1GHz analog bandwidth, 5GSa/s

# G. Varner and L. Ruckman NIM A602 (2009) 438-445.

E. Oberla, J-F Genat, H. Grabas, H. Frisch, K. Nishimura, G. Varner NIM A**735 (2014) 452-461**.

Simulation includes detector response

J-F Genat, G. Varner, F. Tang, H. Frisch NIM A**607 (2009) 387-393**.

> Extending to 1ps and lower, with advanced calibration techniques

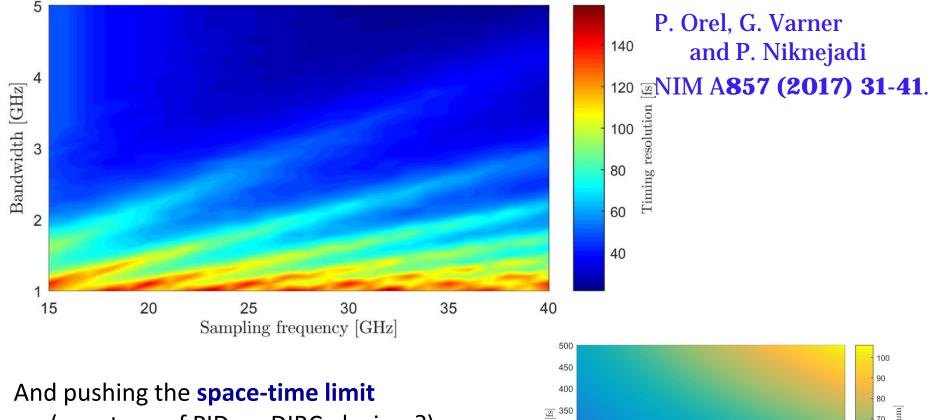

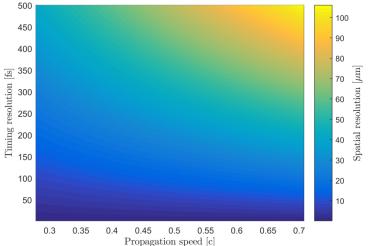

### Now pushing to the femtosecond regime

Pushing sampling speed and analog bandwidth

(new type of PID or DIRC devices?)

P. Orel and G. Varner

IEEE Trans. Nucl. Sci. 64 (2017) 1950-1962.

# Summary

Waveform-sampling readout, directly married to fast detectors has been a Hawaii focus

# • Cost for large experiments:

- Reduce cabling, power requirements

- > Underlying technology inexpensive, powerful

### • Performance:

- Space-time photon resolution PD determined

- > High rate, pile-up robustness

### • Maturity:

- Complex firmware biggest headache

- > In-ASIC functionality, commercial support

# Backup

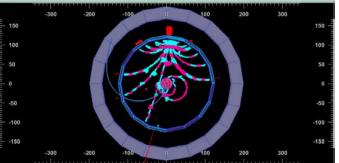

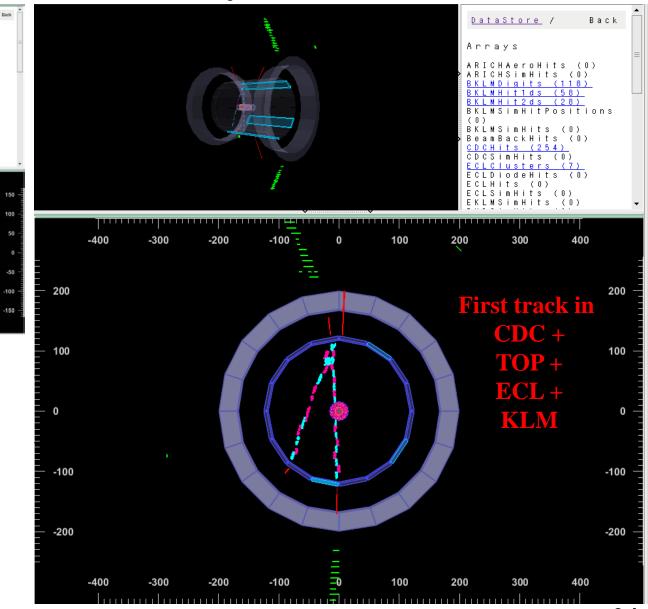

First showering Event: CDC + TOP + ECL

# **IRSX Single Channel**

• Sampling: 128 (2x 64) separate transfer lanes

Recording in one set 64, transferring other ("ping-pong")

- Concurrent Writing/Reading

Only 128 timing constants

Storage: 64 x 512 (512 = 8 \* 64)

- Wilkinson (64x1): was (32x2)

- 64 conv/channel

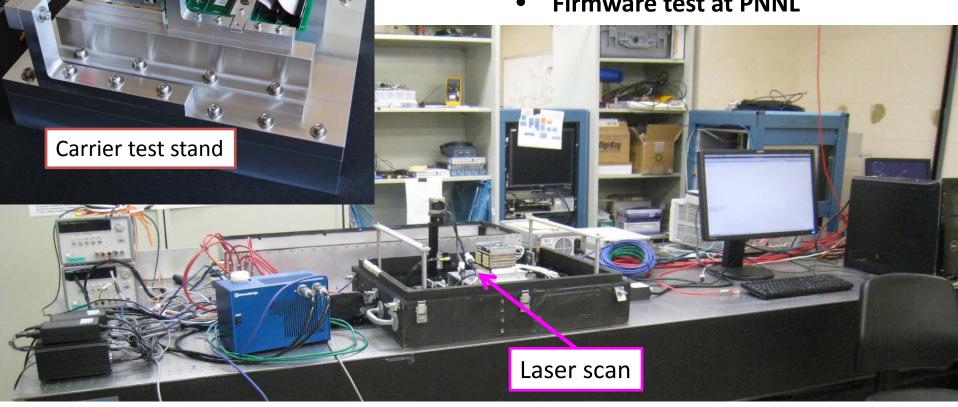

### **iTOP** Readout Production Testing

- 2x Carrier test stations at South Carolina, 1x backup in Hawaii

- Laser test stand Hawaii

- SCROD test stand in Pittsburgh

- Firmware test at PNNL

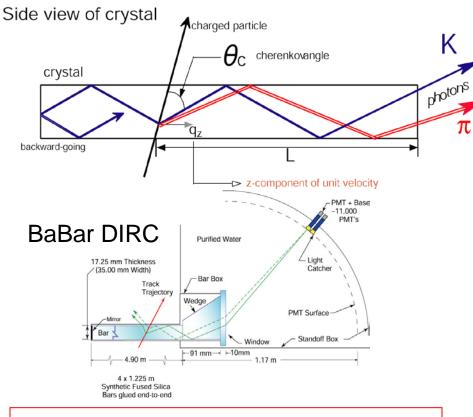

# imaging TOP (iTOP)

**Concept**: Use best of both TOP (timing) and DIRC while fit in Belle PID envelope

Use wide bars like proposed TOP counter

NIM A623 (2010) 297-299.

- Use new, high-performance MCP-PMTs for sub-50ps single p.e. TTS

Use simultaneous T, θc [measuredpredicted] for maximum K/π separation

- Optimize pixel size

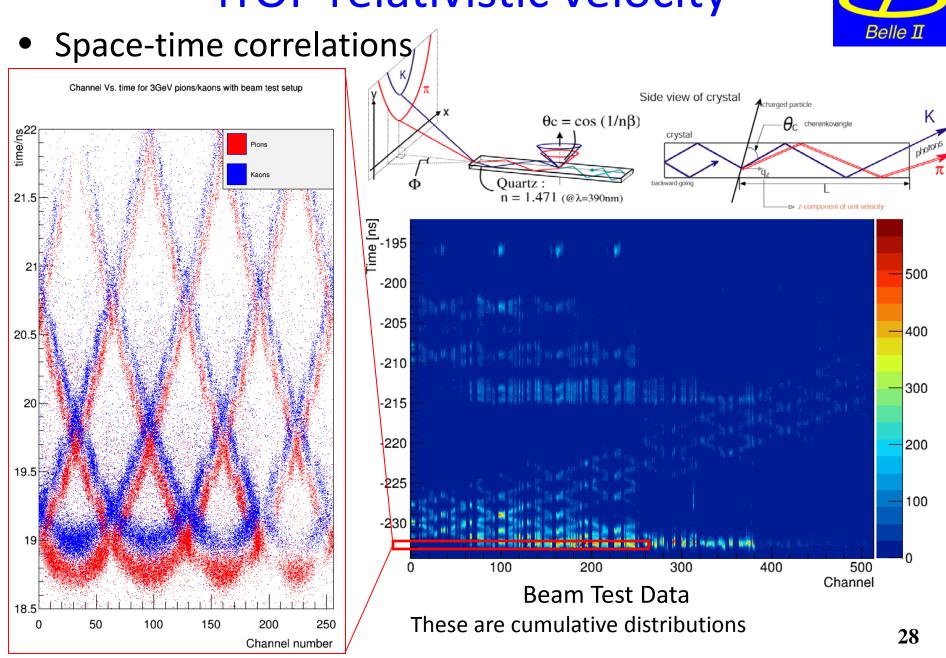

# iTOP relativistic velocity

# Actual PID is event-by-event

• Test most probable distribution

Beamtest Experiment 2 Run 568 Event 1

# Highly integrated services

• A severely constrained space

# imaging TOP Readout (FDIRC proto)

# Production – initial single photon timing

# Incubated at the Manoa Innovation Center Near University of Hawaii

Photo: http://www.myhawaiirealestateonline.com/manoa-real-estate/

#### About Nalu Scientific

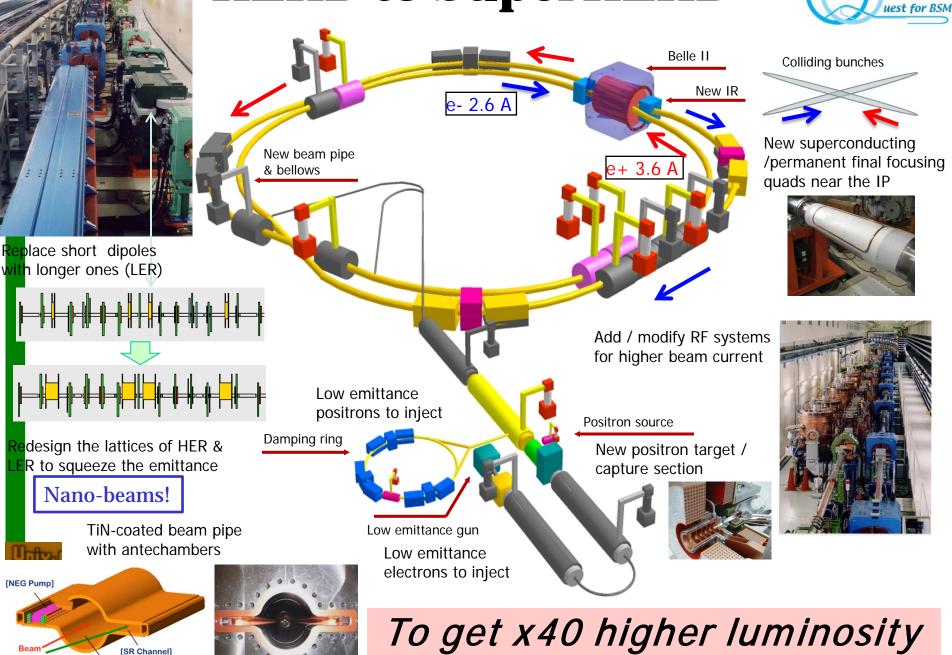

# **KEKB to SuperKEKB**

Super

KFKR

[Beam Channel]

### XRM: Hardware

X-ray beam line under construction at LER

-fly

Masks: ~20  $\mu m$  Au on 600  $\mu m$  CVD diamond substrate

US-Japan Collaboration (U. Hawaii, SLAC, Cornell U.)

High-speed readout electronics for the X-ray monitor, being developed by U of Hawaii.

Water-cooled mask holder

Deep Si pixel detector and spectrometer chips for the X-ray monitor, being developed at SLAC.

#### Instrumentation Dev. Lab Overview – Spring 2017