### "Fast" Readout Electronics (high resolution, fast throughput)

#### Gary S. Varner University of Hawai'i at Manoa

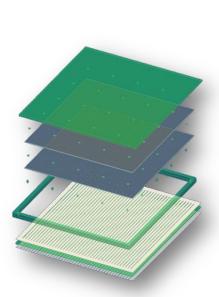

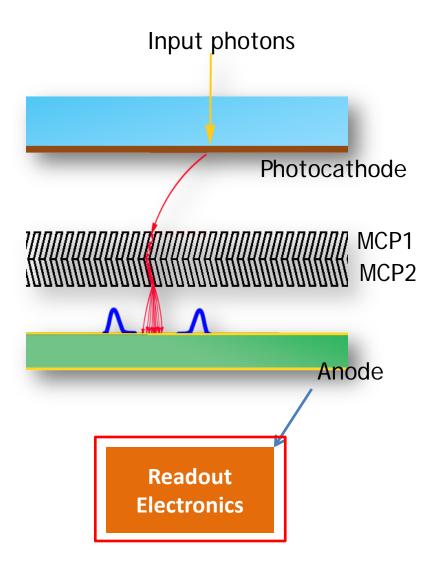

# Elements of an MCP-PMT

- Photocathode

- Micro-channel plates

- Collection anode

- Readout electronics

- Mechanical design / tile assembly.

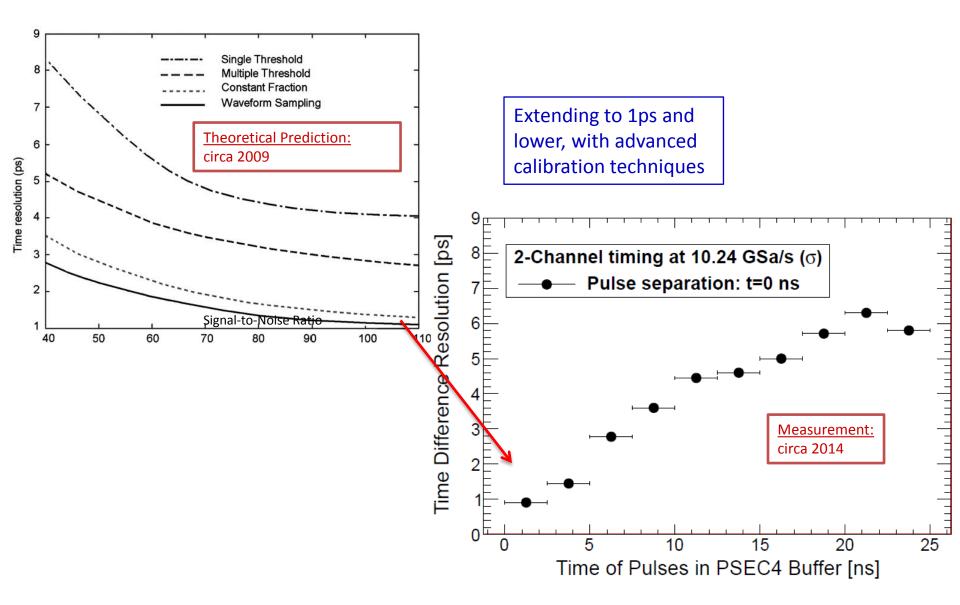

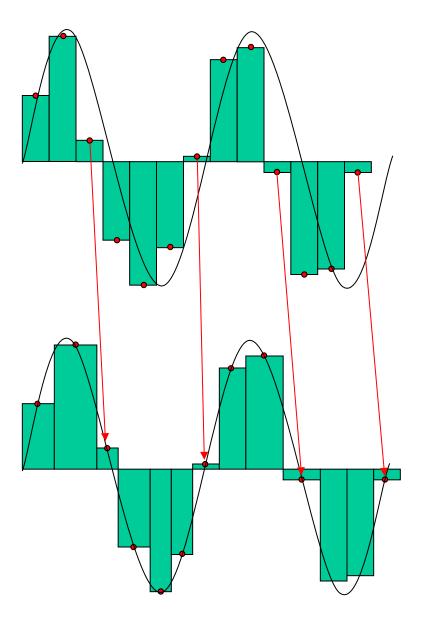

# **Timing Methods**

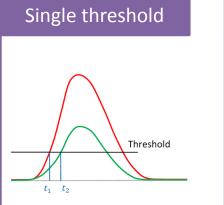

The single threshold is the least precise time extraction measurement. It has the advantage of simplicity.

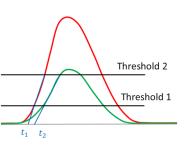

Multiple threshold

The multiple threshold method takes into account the finite slope of the signals. It is still easy to implement.

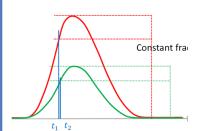

**Constant fraction**

The constant fraction algorithm is very often used due to its relatively good performance and its simplicity. Waveform sampling

Waveform sampling above the Nyquist frequency is the best algorithm since it is preserves the signal integrity.

In principle, sampling above the Nyquist-Shannon frequency and fully reconstructing the signal attains the best timing information.

Attrib. Jean-Francois Genat

## **Continued Evolution**

- CFD + TDC or Discrim. + TDC + Q/Vpeak are well established techniques

- Next generation HPTDC @ CERN

- NINO and other front-ends

- Recent years has seen explosive growth in evolution of Switched Capacitor Array waveform samplers

- Best choice can be application-specific

- Will review results/projections

- Interesting convergence of technologies

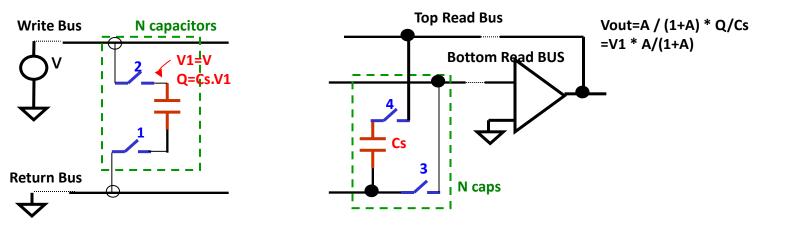

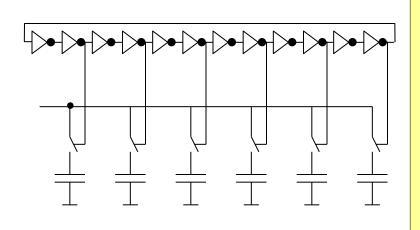

### SCA Underlying Technology

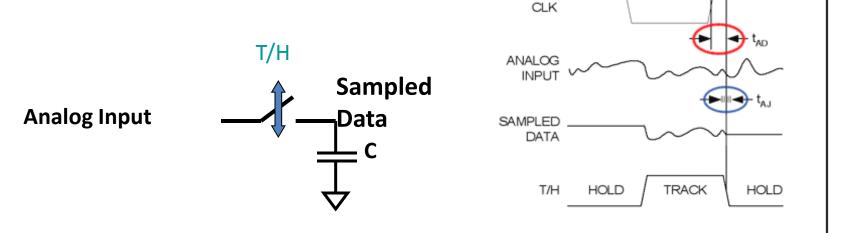

• Track and Hold (T/H)

• Pipelined storage = array of T/H elements, with output buffering

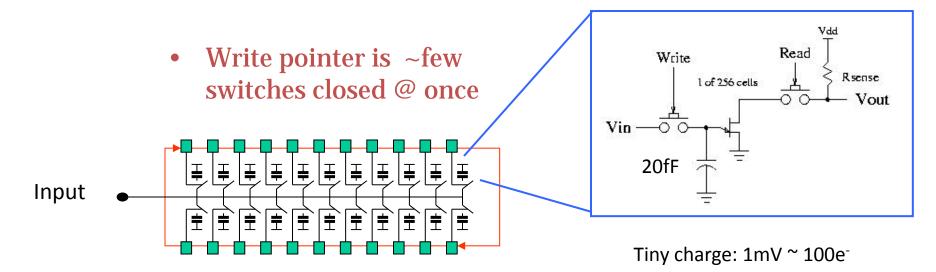

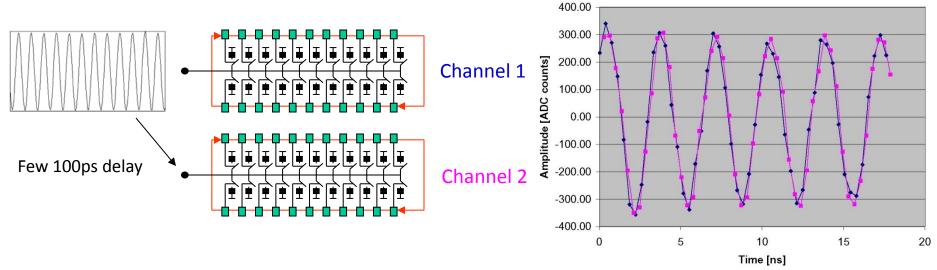

### Switched Capacitor Array Sampling

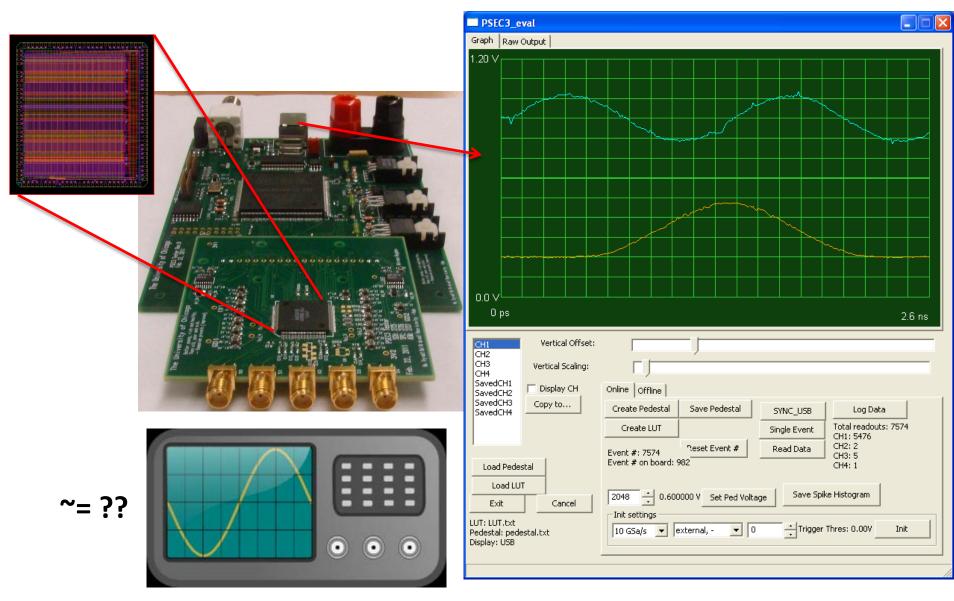

300MHz RF Sine [50mV amplitude]

#### **Basic Functional components**

### **A Portfolio of Waveform samplers**

| ASIC    | Amplification? | # chan | Depth/chan | Sampling [GSa/s] | Vendor | Size [nm] | Ext ADC? |

|---------|----------------|--------|------------|------------------|--------|-----------|----------|

| DRS4    | no.            | 8      | 1024       | 1-5              | IBM    | 250       | yes.     |

| SAM     | no.            | 2      | 1024       | 1-3              | AMS    | 350       | yes.     |

| IRSX    | no.            | 8      | 32536      | 1-4              | TSMC   | 250       | no.      |

| BLAB3A  | yes.           | 8      | 32536      | 1-4              | TSMC   | 250       | no.      |

| TARGET  | no.            | 16     | 4192       | 1-2.5            | TSMC   | 250       | no.      |

| TARGET2 | yes.           | 16     | 16384      | 1-2.5            | TSMC   | 250       | no.      |

| TARGETX | no.            | 16     | 16384      | 1-2.5            | TSMC   | 250       | no.      |

| RITC    | no.            | 3      | Continuous | 1-3.7            | IBM    | 130       | no.      |

| PSEC4   | no.            | 6      | 256        | 1-16             | IBM    | 130       | no.      |

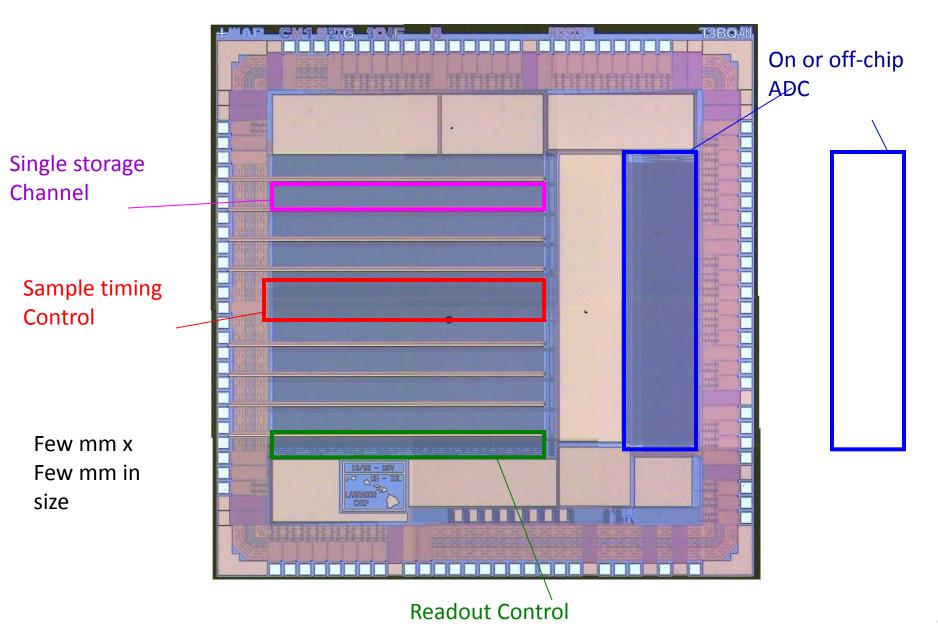

#### Gen 2 Enabling Technology (ATWD Gen 1)

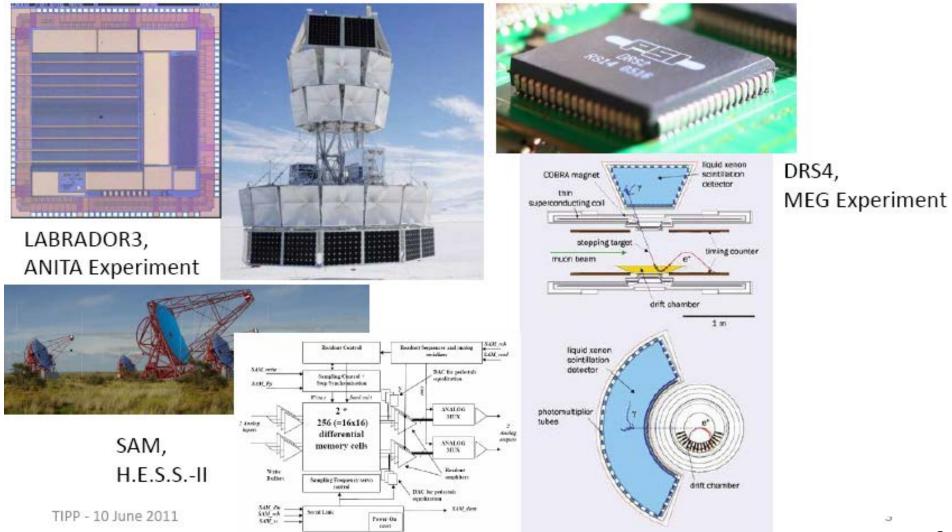

#### Already in use in many experiments...

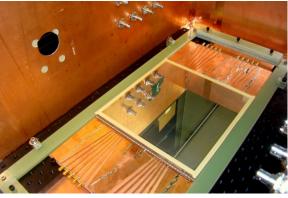

# **Integrating Readout Electronics**

- Detectors and Readout electronics keep pushing each other

- Readout based on waveform sampling

- Requirements of the readout vary significantly by application

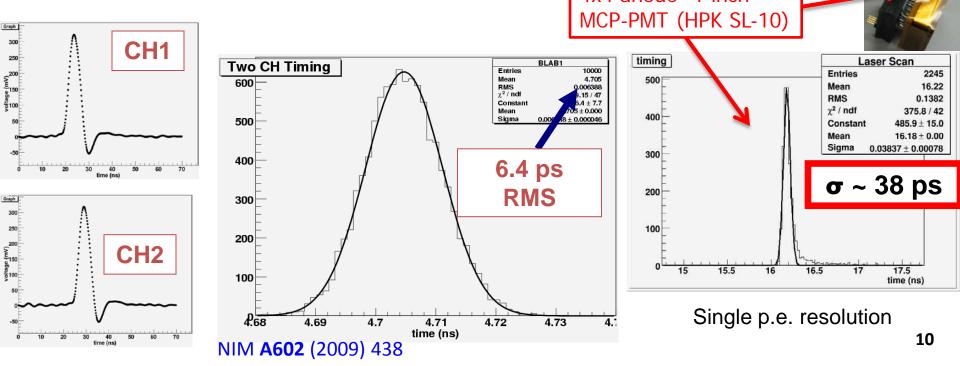

4x4 anode "1 inch"

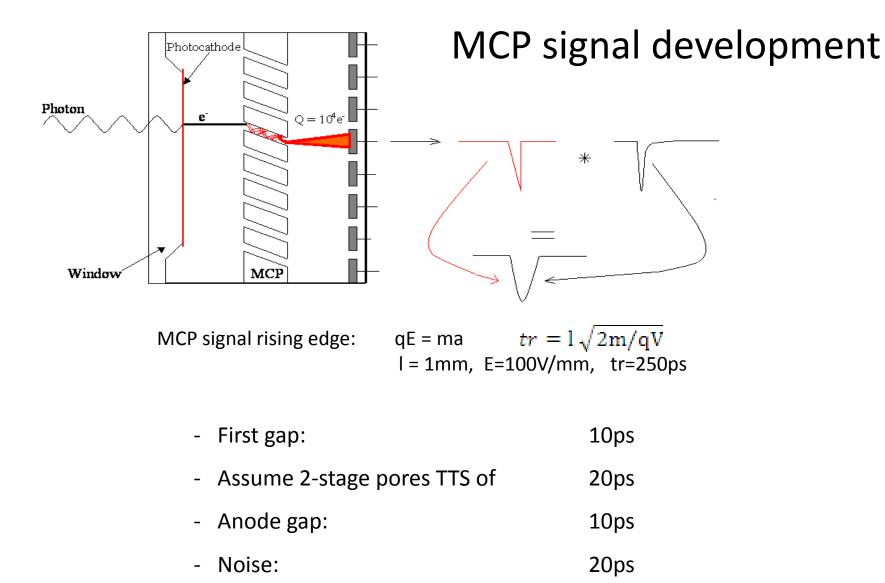

#### Total is 32ps

(Measured Burle-Photonis 2" x 2" is 30ps)

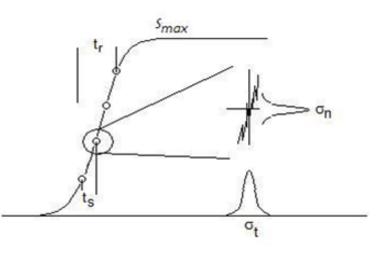

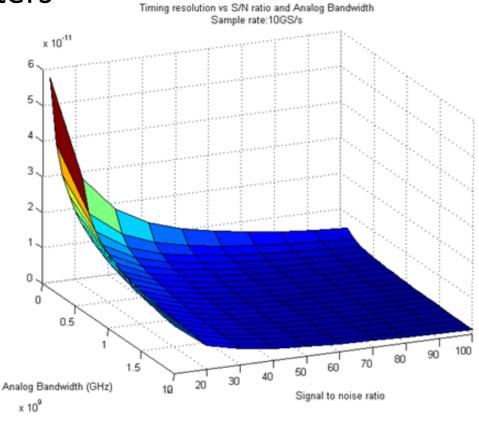

#### Understanding what matters

Transit Time Noise<sub>detector</sub> Rise time Gain (Signal/noise)

**Electronics:**

Noise<sub>elec</sub> Sample rate Analog bandwidth

$$SN = S_{max} / \sigma_n \qquad \sigma_{t,n} = \frac{\sigma_n}{\sqrt{n}}$$

$$\sigma_n = \sigma_{n \, det} + \sigma_{n \, elec}$$

$$\sigma_{t,n} = \frac{\sqrt{t_r t_s}}{SN} = \frac{1}{SN} \sqrt{\frac{0.35t_s}{abw}} \qquad S = G \ Npe$$

The Factors that Limit Timing Resolution, University of Chicago, April 28-29, 2011

#### **ps Timing Resolution**

### The "no free lunch" Theorem

• Excellent results obtained

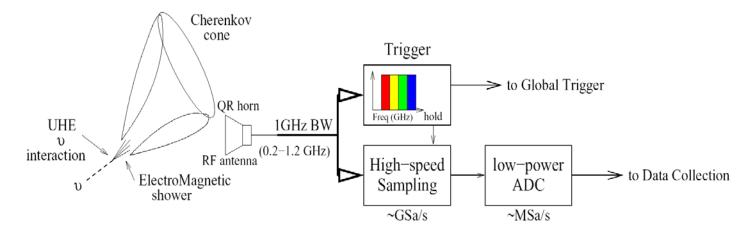

**1. Has made ANITA and other projects possible & highly successful**

2. Similar architectures being studied for new and upgraded experiments

3. Minimize costs for large systems

- Not a magic solution

- Significant/important constraints

- Technology in its adolescence will continue to improve

- Limits and future directions First, the current limitations, in a bit more detail

#### **Constraint 0: An Intrinsic Limitation**

No power (performance savings) for continuous digitization

Won't displace Flash ADCs

→ For most "triggered" 'event' applications, not a serious drawback

#### Constraint 2: Storage Depth

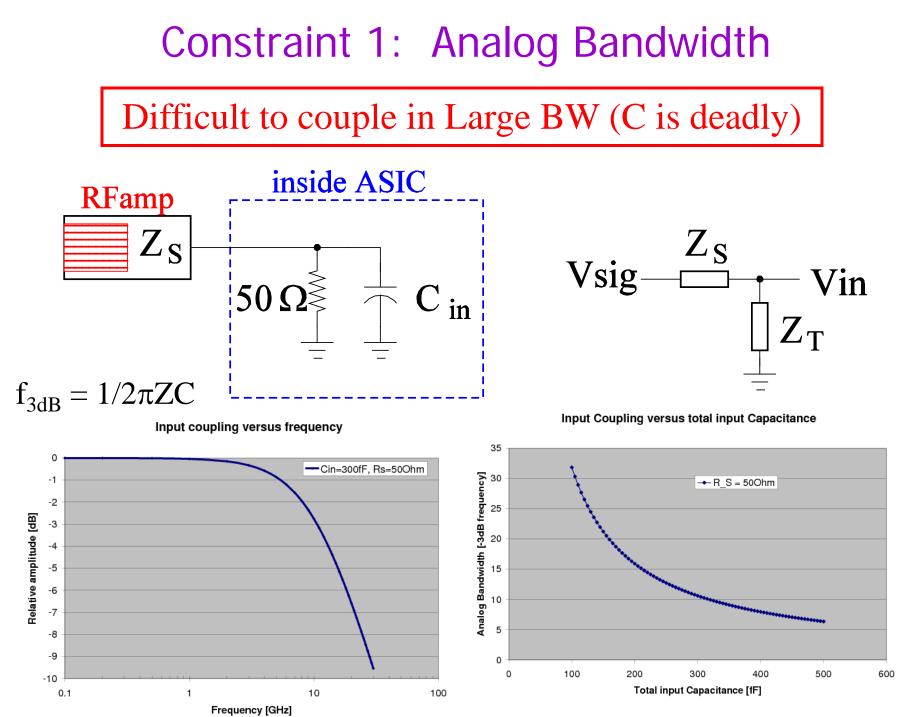

$f_{3dB} = 1/2\pi ZC$

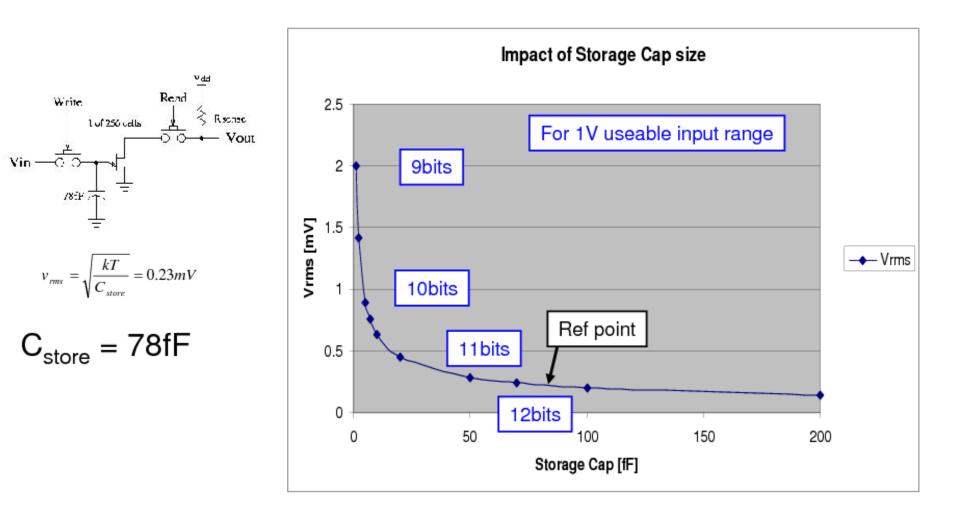

Would like smallest possible Cstore

- For 1.2GHz, C <~ 2pF (NB input protection diode ~10pF)

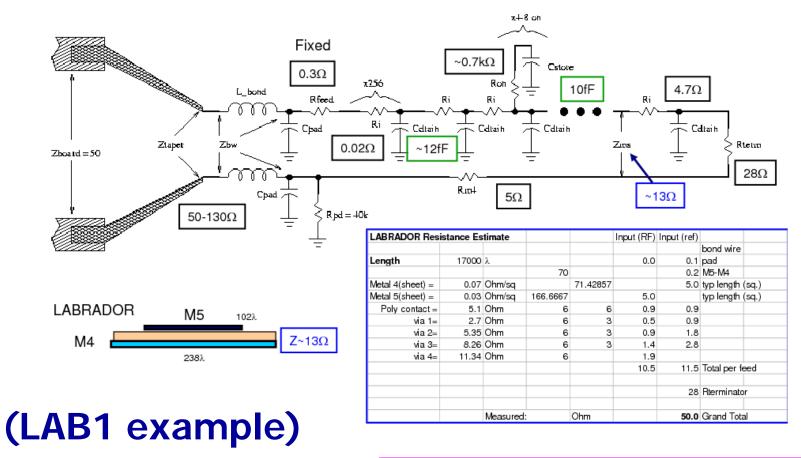

- Minimize C, (C<sub>drain</sub> not negligible x260)

#### Constraint 3: kTC Noise

#### Want small storage C, but...

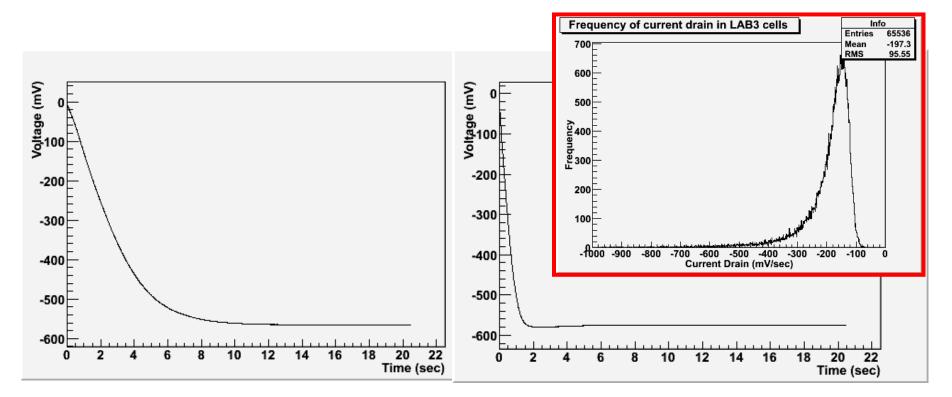

#### Similar Constraint 3b: Leakage Current

Increase C or reduce conversion time << 1mV

Sample channel-channel variation ~ fA leakage typically (0.25um process) Becomes much worse in faster (digital) processes

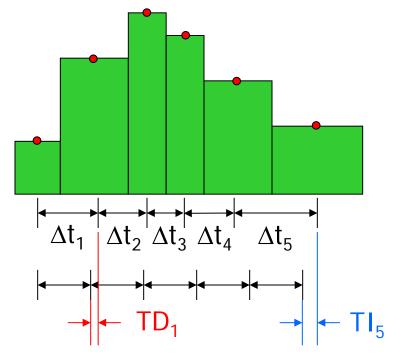

#### Constraint 4: Sample Aperture Variance

- Inverter chain has transistor variations

- $\rightarrow \Delta t_i$  between samples differ

- → "Fixed pattern aperture jitter"

- "Differential temporal nonlinearity"  $TD_i = \Delta t_i - \Delta t_{nominal}$

- "Integral temporal nonlinearity"  $TI_i = \Sigma \Delta t_i - i \cdot \Delta t_{nominal}$

- "Random aperture jitter" = variation of Δt<sub>i</sub> between measurements

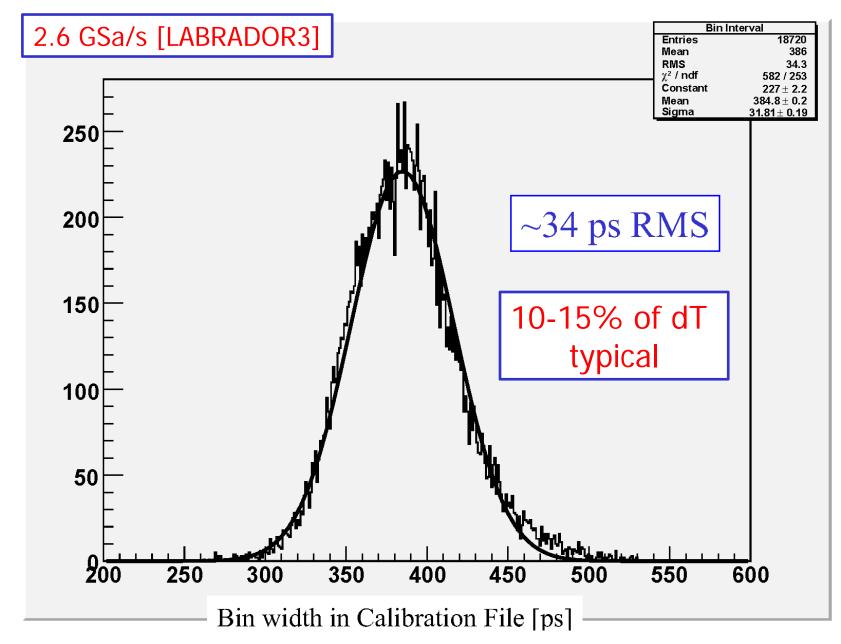

#### Sample-sample timing "dT" Spread

#### Average aperture calibration

- Fixed aperature offsets are constant over time, can be measured and corrected

- Several methods are commonly used (sine fit [left], zero-crossing)

- Most use sine wave with random phase and correct for TD<sub>i</sub> on a statistical basis

# Great progress in improved algorithms:

http://arxiv.org/abs/1405.4975

However still computationally expensive (e.g. resampling for FFTs)

### "3<sup>rd</sup> Generation" (arbitrary)

- Raw performance of 2<sup>nd</sup> Generation devices

- Have proven themselves

- Somewhat general purpose therefore each adopter wants to change something

- Next generation addressing these constraints

- 1. Analog bandwidth

- 2. Storage depth

- 3. System requirements (clock, flow control, multi-hit, etc.)

- 4. Calibration overhead

- Merely a snapshot:

- 1. This talk is a moving target

- 2. Highly dynamic field

- 3. A lot of cross-pollination

1) Analog bandwidth (sampling, readout speed)

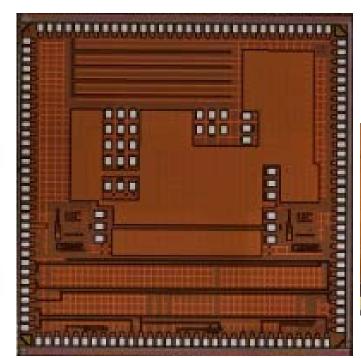

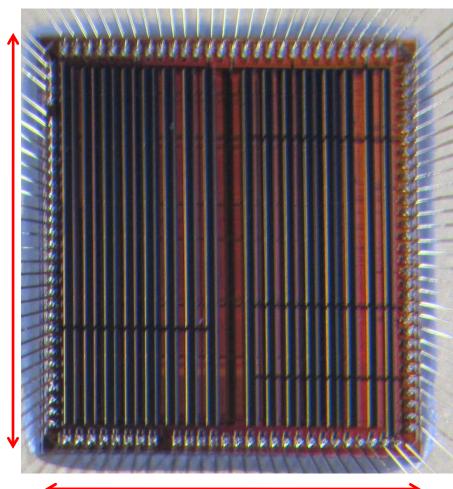

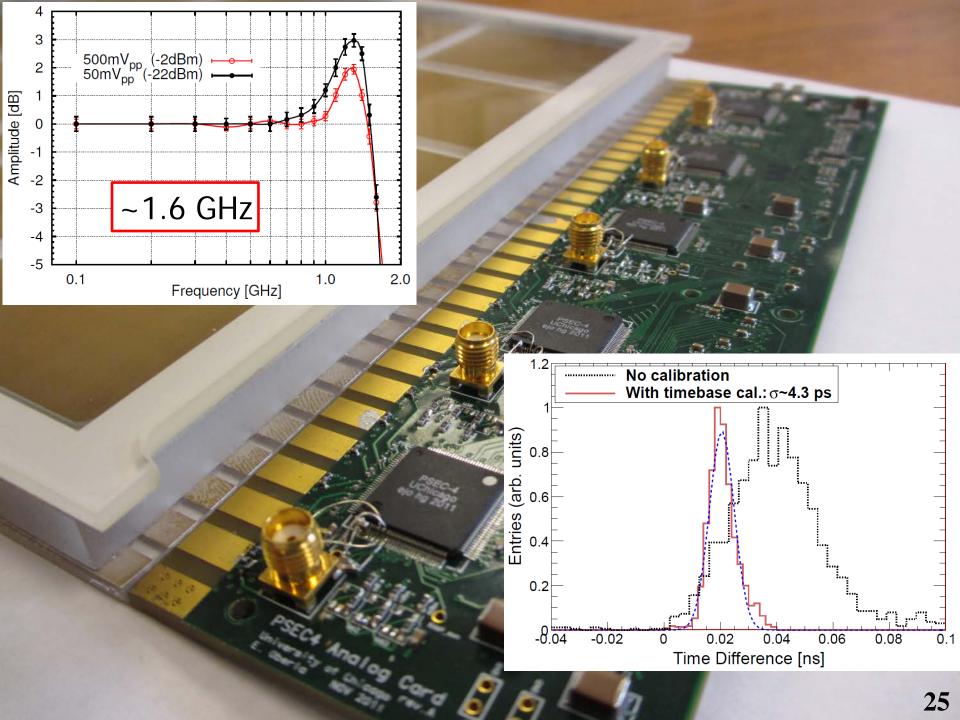

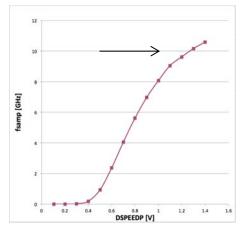

### **PSEC-4 ASIC**

| Sampling Rate    | 2.5 GSa/s-17GS/s 4.3mm              |

|------------------|-------------------------------------|

| # Channels       | 6 (or 2)                            |

| Sampling Depth   | 256 (or 768) points                 |

| Sampling Window  | Depth*(Sampling Rate) <sup>-1</sup> |

| Input Noise      | <1 mV RMS                           |

| Analog Bandwidth | 1.6 GHz                             |

| ADC conversion   | Up to 12 bit @ 2GHz                 |

| Latency          | 2 μs (min) – 16 μs (max)            |

| Internal Trigger | yes                                 |

|                  |                                     |

130nm process – sampling speed, Conversion rate

4.0mm

[E. Oberla, U. Chicago]

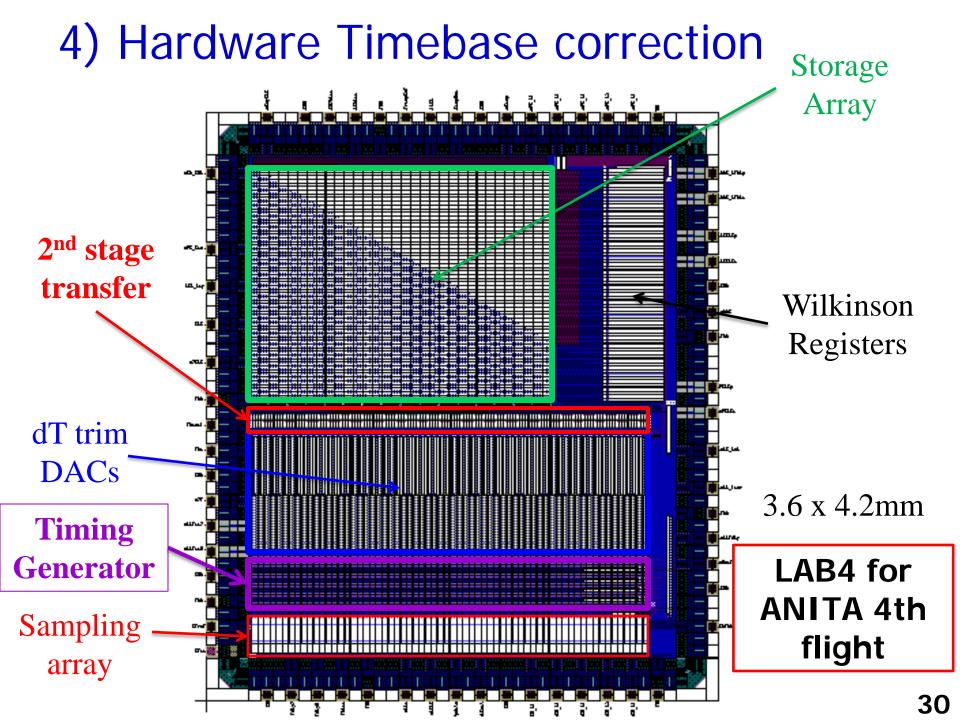

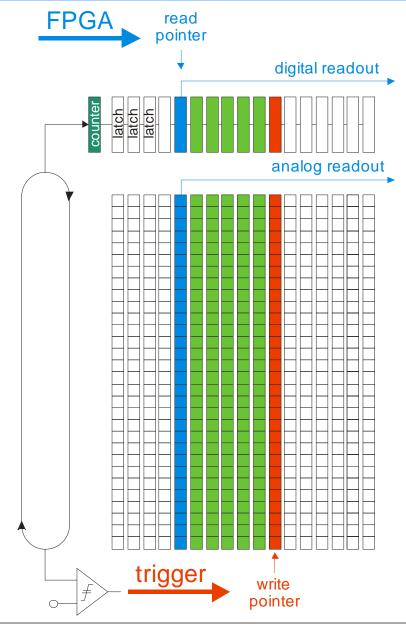

# 2) Storage Depth

• Sampling: 128 (2x 64) separate transfer lanes

Recording in one set 64, transferring other ("ping-pong")

- Concurrent Writing/Reading

- Only 128 timing constants

- Storage: 64 x 512 (8 ch. IRS) (32x512 16 ch. [TARGET – CTA])

- Wilkinson (64x1): was (32x2)

- 64 conv/channel

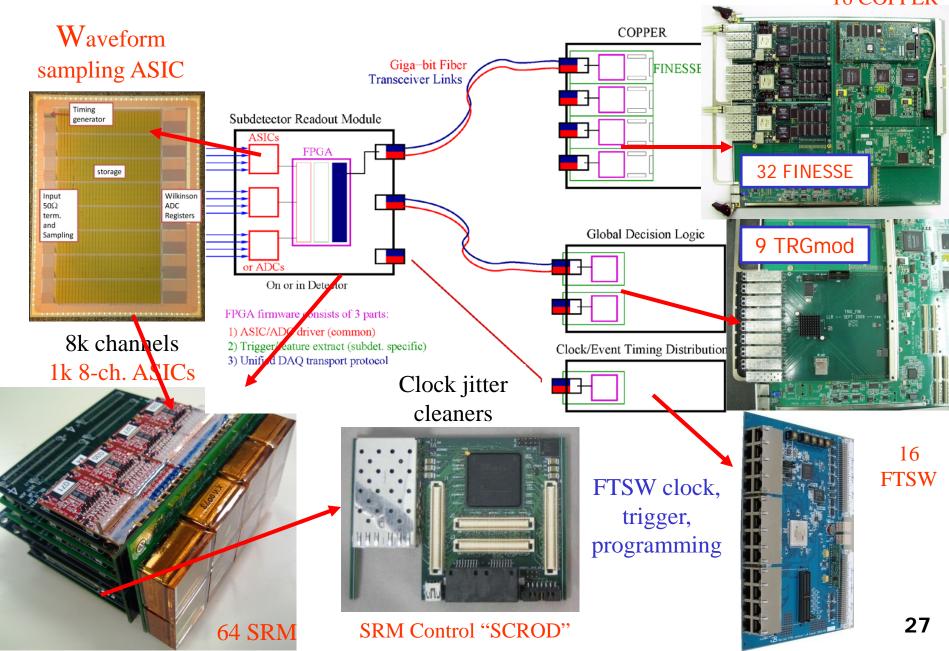

# 3a) Ex. Belle II TOP Readout Architecture

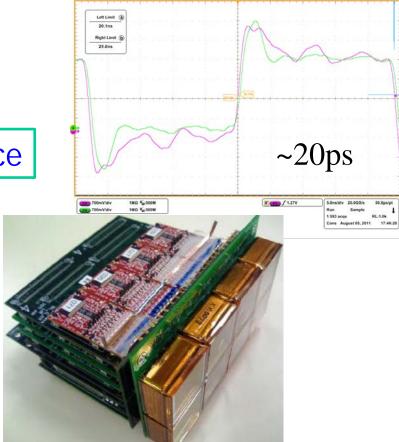

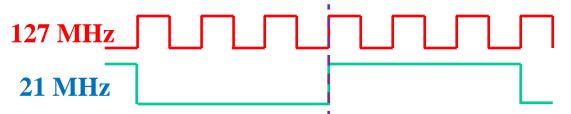

### System Synchronization

Crucial to obtain required performance

FTSW (Timing & Trigger Distribution

board)

127 MHz clock Serial data (trigger & synchronization)

- 127 MHz clock is divided by 6 on front-end module to ~21 MHz

- This corresponds to sampling rate of ~2.7 GSa/s

- FPGA uses serial data stream to determine clock phase

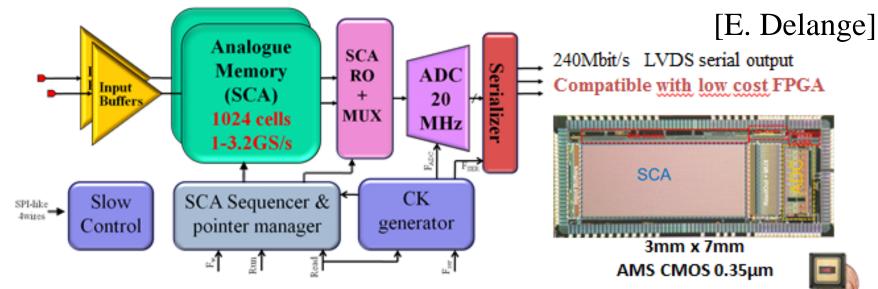

# 3b/4) Multiple TeV-gamma telescopes

#### The NECTAR chip for the Cerenkov Telescope Array

- Evolution of the SAM(LONG) chip (HESS-2 telescope)

- 4 SCA channels => 2 fully differential channels

- 1024 cells/SCA channel (64 x 16 matrix)

- 0.5 to 3.2 GSPS => 1μs max latency @ 1GSPS, 0.5μs @ 2GSPS

- On chip 12 bit pipeline 20MSPS ADC

- Output data directly usable for calculation (without need for pedestal or gain spread correction)

- Low input capacitance < 4pF including package thanks to input buffers</li>

- 4000 chips used for the upgrade of the HESS experiment (Namibia)

PAUL SCHERRER INSTITU

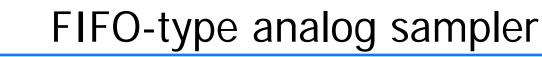

- Self-trigger writing of 128 short 32-bin segments (4096 bins total, 3 GHz analog bandwidth)

- Storage of 128 events

- Accommodate long trigger latencies

- Quasi dead time-free up to a few MHz,

- Possibility to skip segments

→ second level trigger

- Attractive replacement for CFD+TDC

- First tests: > 10 GSPS @ 4 mA, first full version planned for 2014

# Summary

- Options for integrated, high-performance photodetector readout will continue to increase

- Next generation SCA-based readout:

- Higher analog bandwidth

- Faster sampling rate

- Deeper storage depth

- Easier calibration

- Higher throughput

- For higher-rate applications, distinction between WFS and traditional TDC becoming blurred

#### **Back-up Slides**

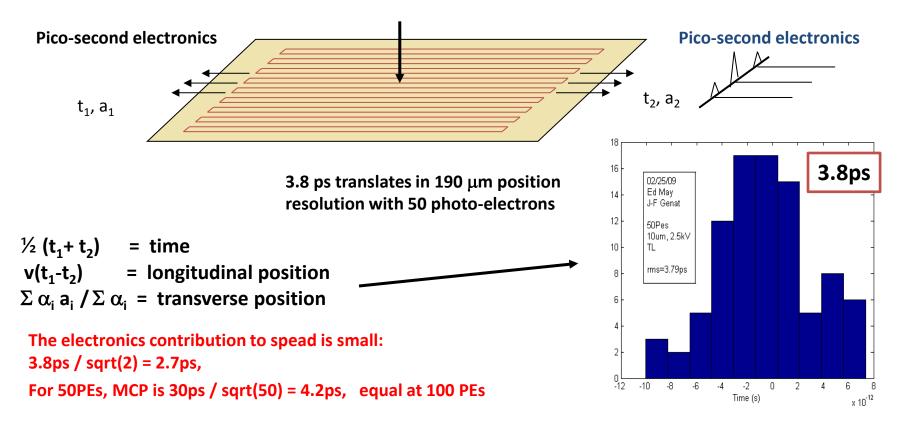

#### Picosecond timing and 2D position for large area detectors: delay lines and Waveform Sampling

Delay line readout and pulse sampling provide fast timing (2-10ps).  $\rightarrow$  Delay lines should have a signal bandwidth matched to the detector

Fewer electronics channels for large area sensors

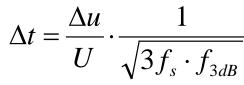

# w is timing resolution affected?

$\frac{3f_s \cdot f_{3dB}}{f_s \qquad f_{3db}} \qquad \qquad \downarrow$

•today:

- •optimized SNR:

- •next generation:

- next generationoptimized SNR:

| U      | $\Delta U$ | $f_s$   | f <sub>3db</sub> | Δt     |

|--------|------------|---------|------------------|--------|

| 100 mV | 1 mV       | 2 GSPS  | 300 MHz          | ~10 ps |

| 1 V    | 1 mV       | 2 GSPS  | 300 MHz          | 1 ps   |

| 100 mV | 1 mV       | 20 GSPS | 3 GHz            | 0.7 ps |

| 1V     | 1 mV       | 10 GSPS | 3 GHz            | 0.1 ps |

#### •How to achieve this?

includes detector noise

in the frequency region of the rise time

and aperture jitter

Assumes zero

aperture jitter

Stefan Ritt slide

UC workshop 4/11

April 28th, 2011

Stefan Ritt

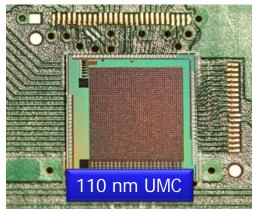

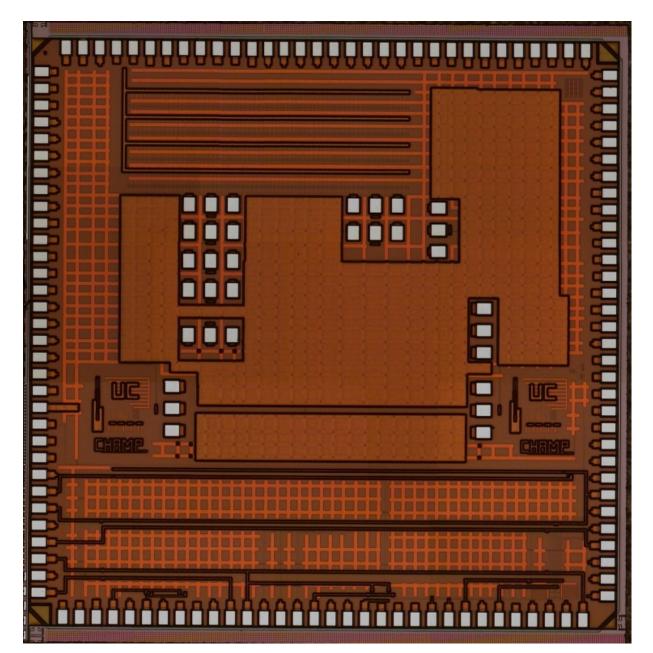

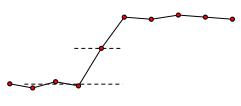

### Chicago Hawaii ASIC, Multi-Purpose (CHAMP)

Develop new circuit elements, train additional students in the IBM 130nm process

<sup>2</sup>/<sub>y</sub> 1.2

<sup>2</sup>/<sub>y</sub> 1.

### Oscilloscope on a chip? -> Calibration