# REPORT ON DAPHNE DEVELOPMENT GATEWARE AND SOFTWARE

Manuel Arroyave<sup>1</sup>

<sup>1</sup>Universidad EIA-Colombia

May 21, 2020

#### **Outline**

Documents prepared for the mini-review

**Fundamental ideas**

Requirements for DAPHNE

#### **Documents for the mini-review**

#### https://edms.cern.ch/document/2342785/1

- ▶ DAPHNE General Report. Late February.

- ► DAPHNE Firmware Gateware description.

- ▶ DAPHNE Hardware description.

- Cold Interface Document.

- ▶ DAPHNE Flange Cables.

#### Ideas to understand documentation

- ► It is not an upgrade.

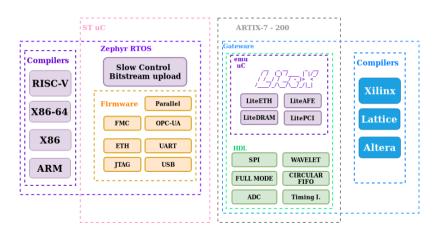

- We are working with RTL automatized output.

- We are implementing gateware and firmware that will not be used in DUNE.

## Requirements for DAPHNE - on the paper

- ▶ 14 bit resolution.

- ▶ 62.5 MSPS.

- ► 40 channel granularity.

- ▶ Low dark noise rate.

- Power support for the cold electronics.

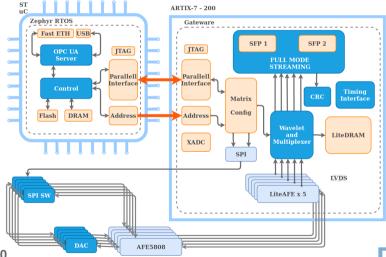

### **Block diagram**

## Status of the development

We need to prepare to use the Vivado transceiver debugger.

- ► AFE Not yet able to test the link

- ► Gb ETH Gb ETH over PHY SFP

- RAM (Checked with both packages)

- ► CRC (Clock Recovery Circuit for the inner use)

- ► SPI (All DACs, AFES, and ADC use it)

- SoC has been tested.

## **Support**

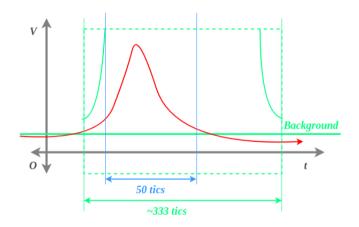

## Wavelet and zero suppression