## **Future Directions in high-speed, transient waveform digitization**

### Gary Varner University of Hawaii

Input to the Snowmass process

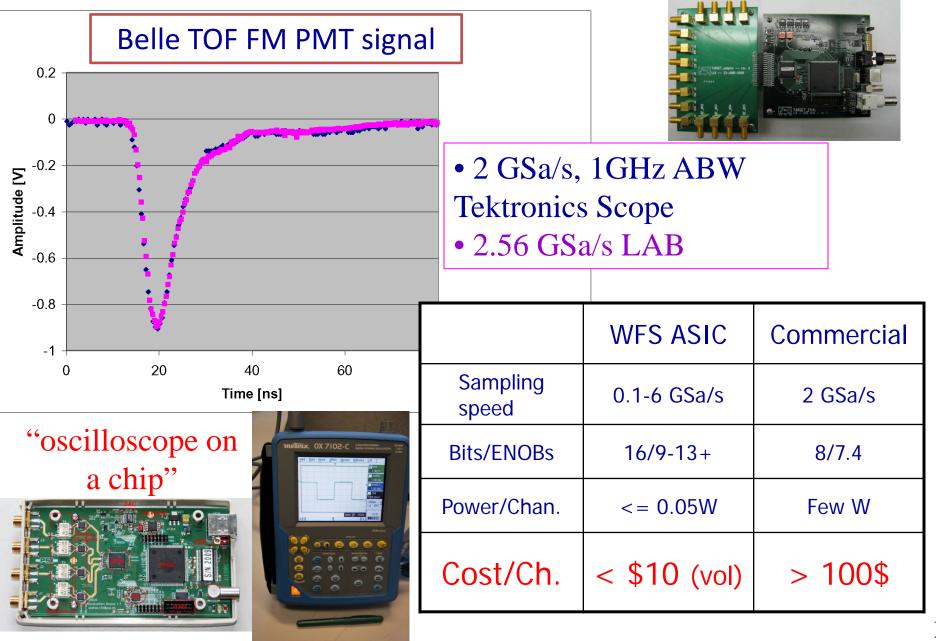

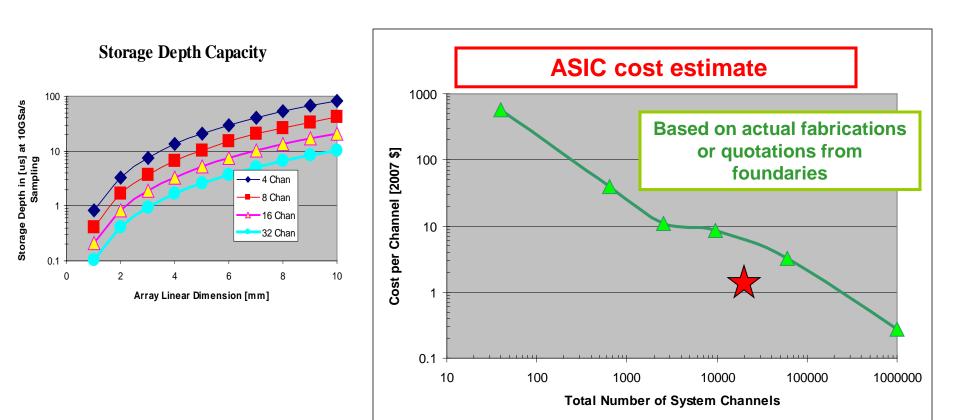

# Switched Capacitor Array technology

What can learn from these developments

• ASIC costing well understood, very competitive!

NIM A591 (2008) 534-345.

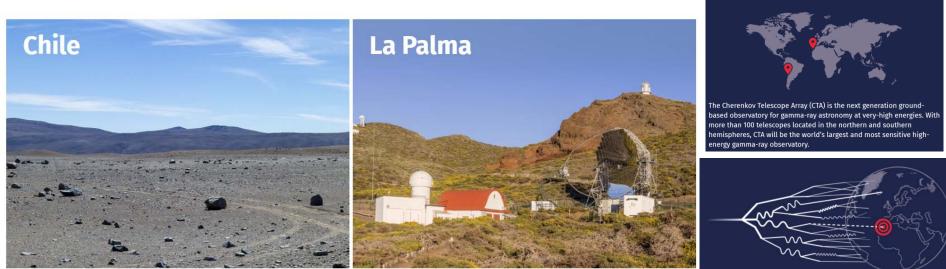

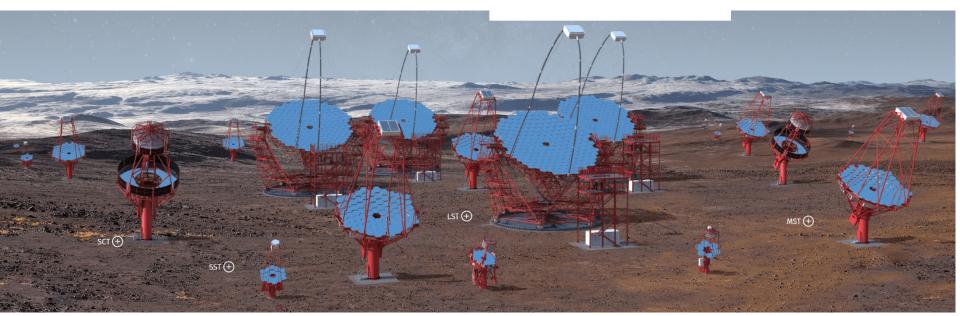

# Cherenkov Telescope Array

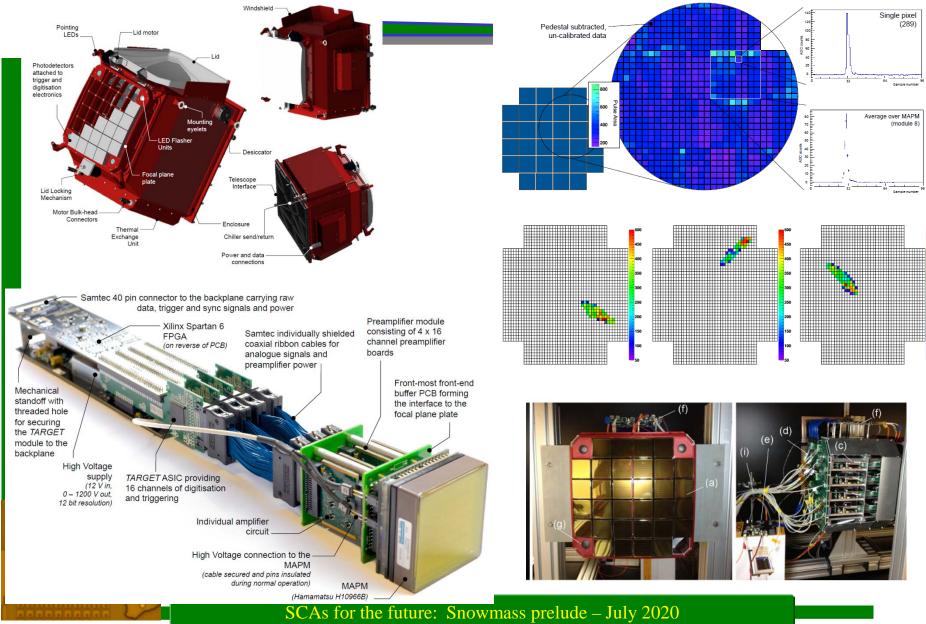

# GCT Camera (CTA) – Gearing for prod.

## Technology has room to improve

#### 1GHz analog bandwidth, 5GSa/s

G. Varner and L. Ruckman NIM A602 (2009) 438-445.

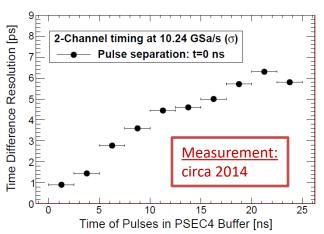

E. Oberla, J-F Genat, H. Grabas, H. Frisch, K. Nishimura, G. Varner NIM A**735 (2014) 452-461**.

Simulation includes detector response

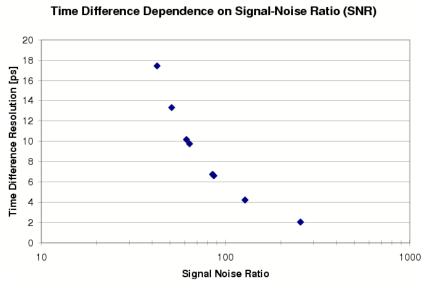

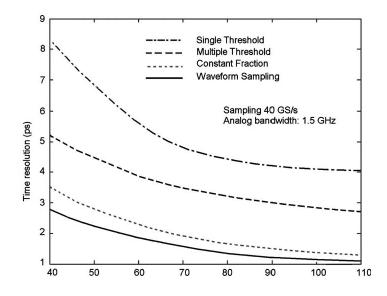

J-F Genat, G. Varner, F. Tang, H. Frisch NIM A**607 (2009) 387-393**.

> Extending to 1ps and lower, with advanced calibration techniques

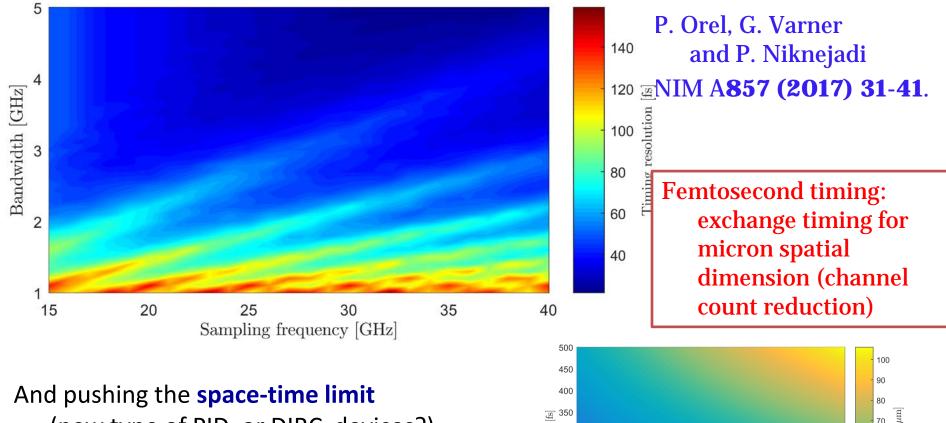

## Now pushing to the femtosecond regime

Pushing sampling speed and analog bandwidth

noitulion [

200

150

100

50

0.3

0.35

Timing

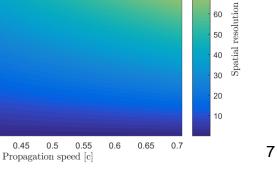

(new type of PID or DIRC devices?)

P. Orel and G. Varner

IEEE Trans. Nucl. Sci. 64 (2017) 1950-1962.

70

Super

KFKR

[Beam Channel]

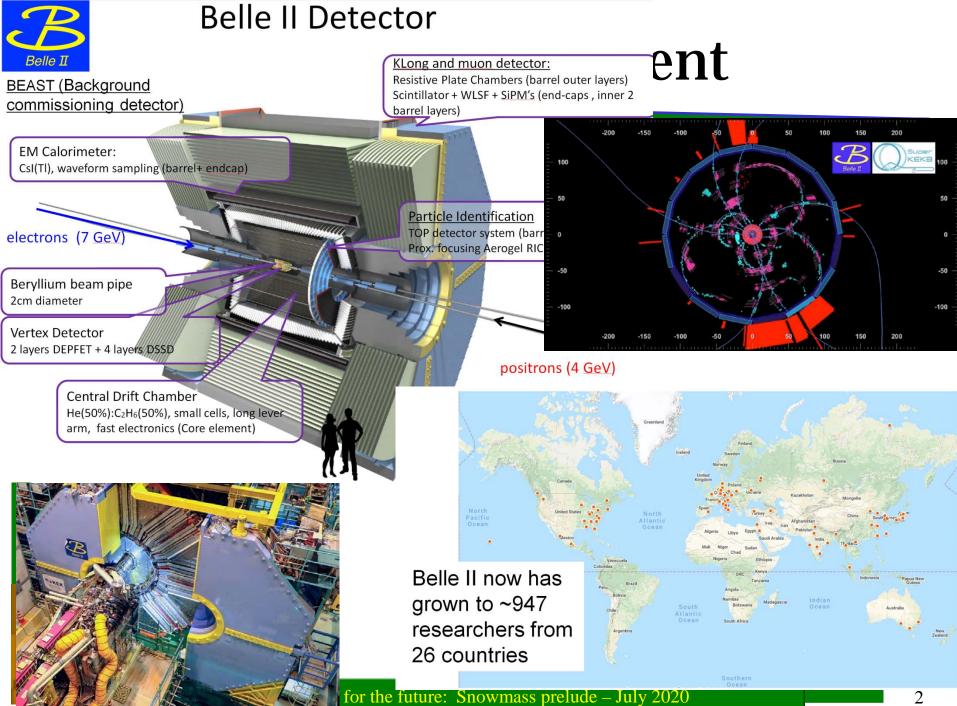

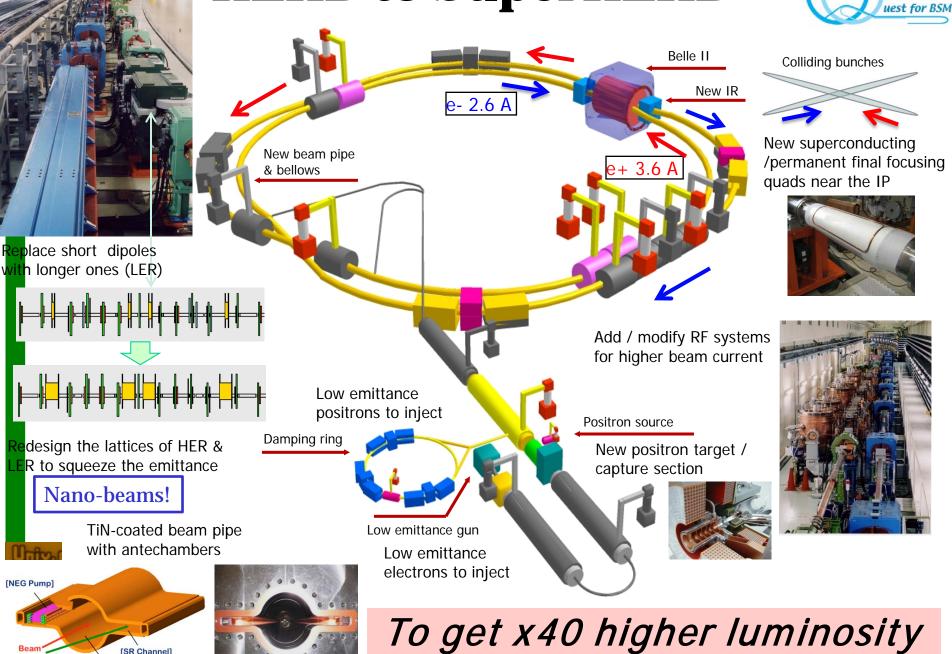

# Huge data challenge: online reduction (many TB/s)

X-ray beam line under construction at LER

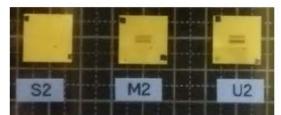

Masks: ~20  $\mu m$  Au on 600  $\mu m$  CVD diamond substrate

US-Japan Collaboration (U. Hawaii, SLAC, Cornell U.)

High-speed readout electronics for the X-ray monitor, being developed by U of Hawaii.

Water-cooled mask holder

Deep Si pixel detector and spectrometer chips for the X-ray monitor, being developed at SLAC.

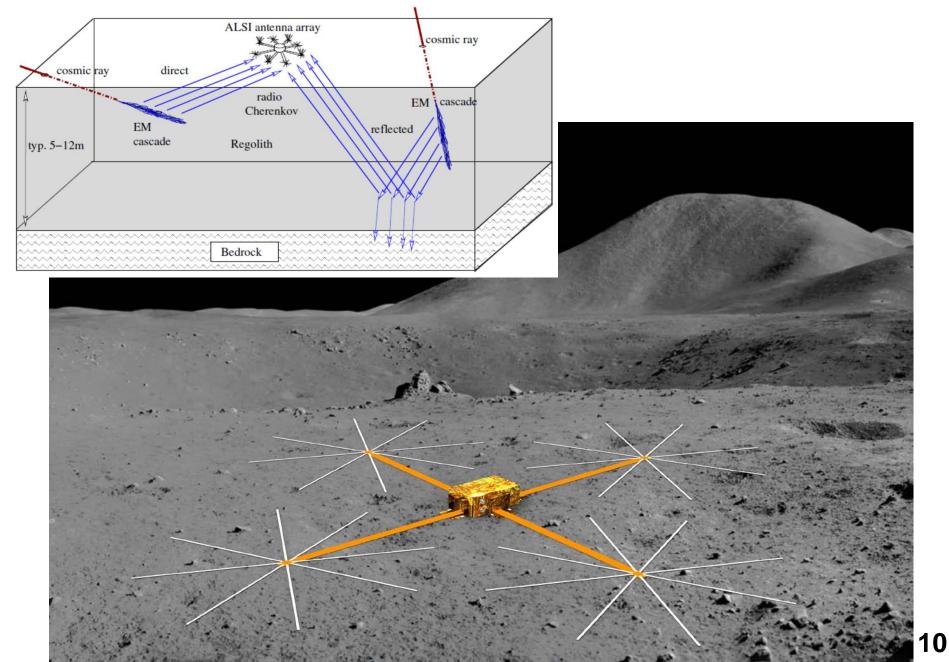

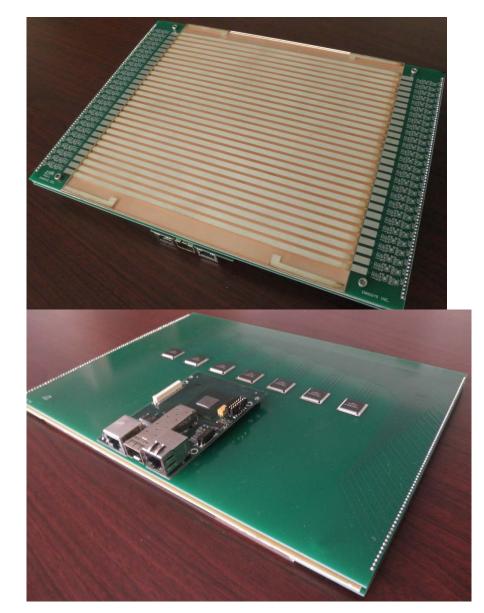

## Low power: Lunar cosmic-ray radio geology

## Strategy for Extreme Low Power operation

- Only power what actually need

- CMOS intrinsically zero power when idle

- Strategy works for either strip or pixel geometry

- Places to reduce power:

- Remove FPGA

- Low-power processing

- Single ASIC

## **Future directions (summary)**

- 1. Femtosecond timing to provide

- a. Reduction of spatial granularity (8M -> 4k ch.)

- b. "streak camera" diagnostics

- 2. Feature extraction (marry more digital processing with power of SCA) for 'up front' data reduction

- 3. As scale to large experimental systems, cost and POWER are huge (existential) issues