# Monolithic Active Pixel Sensors for High Performance Tracking

G.W. Deptuch, G.A. Carinii, G. Giacomini, A. Tricoli Brookhaven National Laboratory L. Greiner, N. Apadula, A. Collu, E. Sichtermann Lawrence Berkeley National Laboratory

Technology for monolithic tracking and timing devices

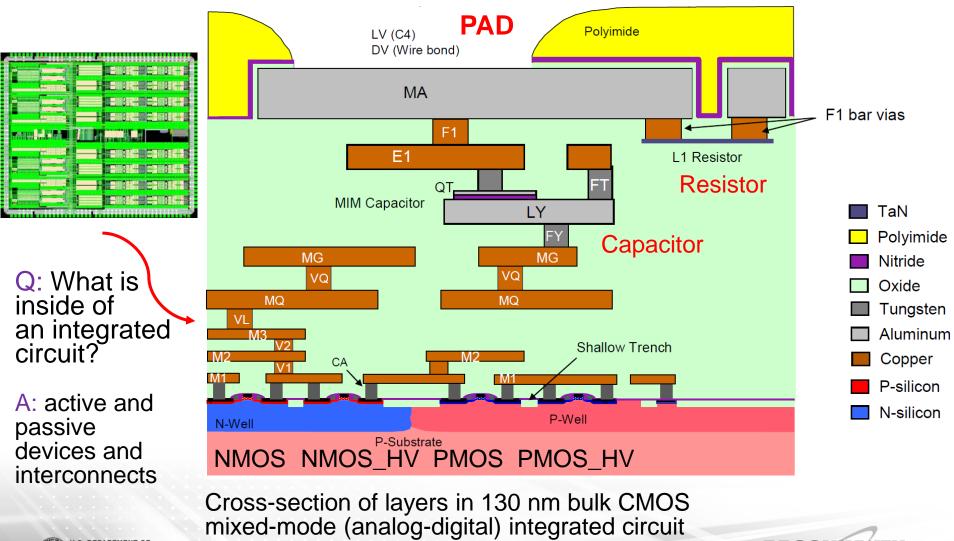

### **Typical bulk CMOS process**

IBM

NATIONAL LABORATORY

# **Typical bulk CMOS process**

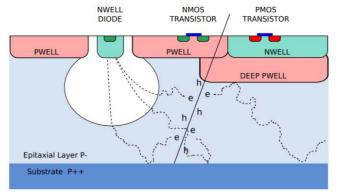

VNwiell VPsub. NMOS Q: How PMOS Twin-well: transistors are built and nMOSFETs  $D^+$ n+ **D**\* how the are share isolated? common P-well N-well N-well substrate (pwell) twin-well A: transistors P substrate "sit" in wells and wells are VPsub VNwell VPwell implanted in NMOS PMOS substrate; Tripple-well: substrate is D+ n +typically pnMOSFET do type not share P-well P-well. substrate N-well N-well between them Deep N-well (extra pwell inside nwell-P substrate tripple-well deep\_nwell)

U.S. DEPARTMENT OF

Implanted wells create diodes with other doped areas, so these structures can act as sensors

### **MAPS in 2000+**

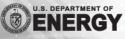

#### From digital photography

advantages:

- small pitch (high tracking precision),

- low amount of material,

- fast readout.

- moderate price, SoC, etc.

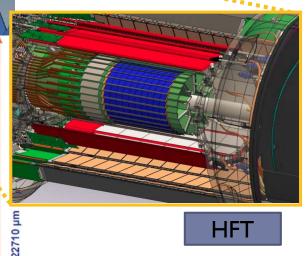

### MAPS in 2000+ =>PXL MAPS sensor

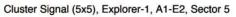

- This early MAPS made to STAR <u>HFT: Ultimate-2: 3<sup>rd</sup> rev. sensor for PXL by PICSEL of IPHC, Strasbourg</u>

- AMS OPTO 0.35 process

- Binary readout of hit pixels

- Increased resistivity p-epi layer

- Reduced charge collection time

- Improved radiation hardness

- ▶ S/N ~ 30

- MIP Signal ~ 1000 e-

- 185.6 µs integration time

- ~170 mW/cm<sup>2</sup> power

#### Rolling-shutter readout

- I. A row is selected

- 2. For each column, a pixel is connected to discriminator

- 3. Discriminator detects possible hit

- 4. Move to next row

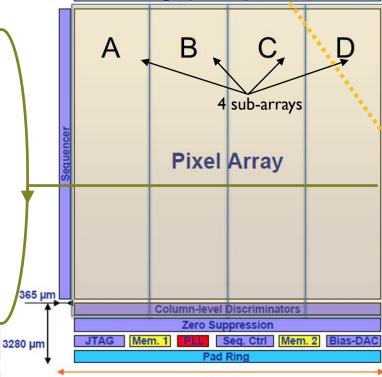

#### Pixel matrix

- > 20.7 µm x 20.7 µm pixels

- ▶ 928 rows x 960 columns = ~IM pixel

- In-pixel amplifier

- In- pixel CDS

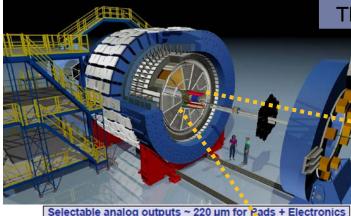

#### The STAR detector @ RHIC

#### HFT – Heavy Flavor Tracker

- SSD Silicon Strip Detector

- IST Intermediate Silicon

- Tracker

- PXL Pixel Detector

#### Digital section

- End-of-column discriminators

- Zero suppression (up to 9 hits/row)

- ✓ ▶ Ping-pong memory frame readout (~1500 W)

- > 2 LVDS data outputs @ 160 MHz

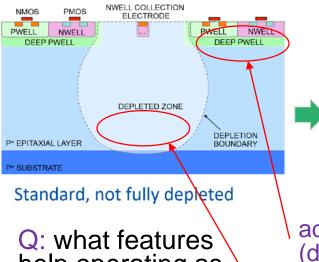

### **Evolution of MAPS**

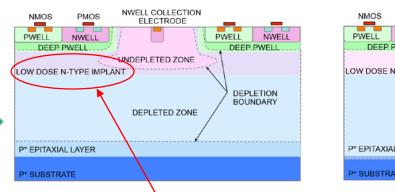

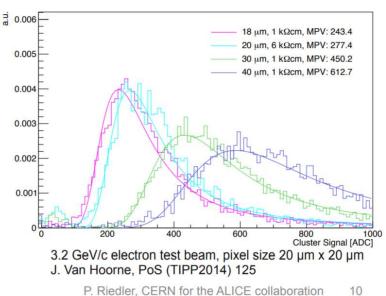

help operating as good detector?

A: several...

- full depletion of sensing volume

- uniform Efield in sensitive volume

- smallest achievable capacitance in sensitive node

added pwell (does not isolate nMOSFETs)

increased resistivity (typically:  $10\Omega cm$ Increased to to ~ $1k\Omega cm$ ) added uniform n-implant to:

- vertical

Efield under wells

- no extra capacitance if depleted

- nevertheless

no lateral E

field

Depletion at higher reverse bias

applied stronger voltage for more depletion, but watch out breakdowns

Foundry accepted process additions to TJ 180nm and good results were obtained

https://dx.doi.org/10.1016/j.nima.2017.07.046

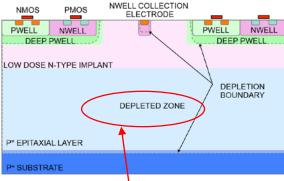

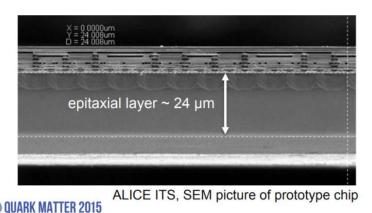

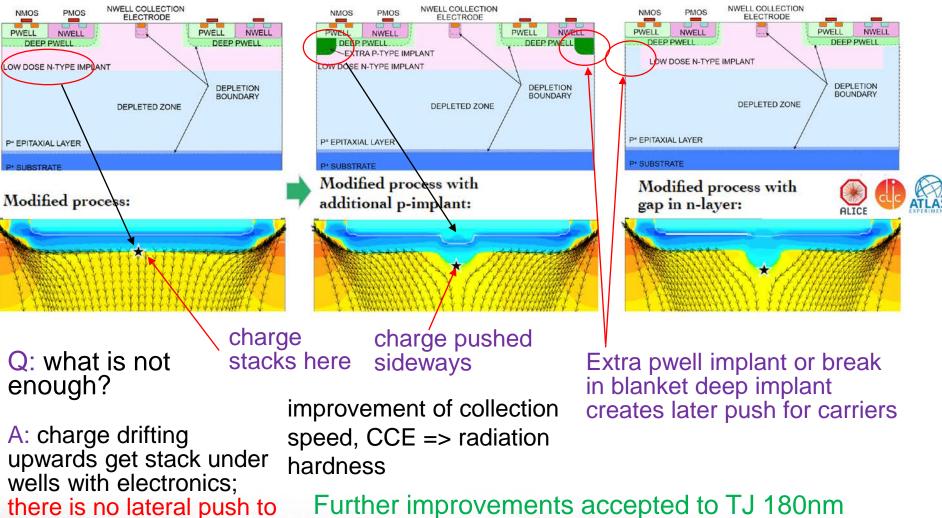

## (PWELL + HR)=ITS

#### ALICE ITS pixel technology

#### MAPS produced in CMOS 0.18 µm process by TowerJazz

- Deep p-well allows to have PMOS and NMOS inside the pixel cell

- High resistivity epi layer

- Chip size: 15 mm x 30 mm, thinned to 50 μm

- Pixel pitch ~ 30 μm

U.S. DEPARTMENT OF

ENERGY

Spatial resolution < 5 μm</li>

BROOKHAVEN NATIONAL LABORATORY

#### **Further evolution of MAPS**

collection nwell

Further improvements accepted to TJ 180nm and good results were obtained but 180nm has density limitation => 10  $\mu$ m pixels difficult

E. Schioppa, et al, VCI 2019 M.Munker, et al. PIXEL2018

NATIONAL LABORATORY

### Use of process features

- Adding features to existing volume production CMOS process is extremely difficult and only possible if foundry sees economical benefits:

- Even using wafers from outside of qualified supplier is out of question,

- Adding or modified doping layers is even more difficult.

- MAPS have been detectors demonstrated assuitable for tracking in some limited areas, but with TJ 180 / TJ 65 for ALICE ITS MAPS gain 100x in performance (bandwidth, TID, NIEL, processing, timing).

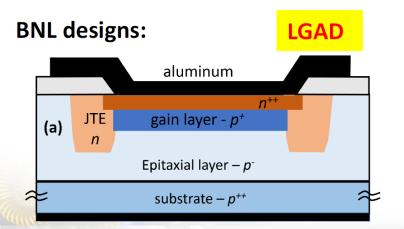

- MAPS combined combine diode as sensitive detection volume.

- Other structures, e.g. avalanche charge multiplying devices (DC / AC-LGAD) can be explored should process features available (implants) allow construction of such a device – needs to be investigated.

### **MAPS technology LOI**

Snowmass 2021 Letter of Interest: Monolithic Active Pixel Sensors for High Performance Tracking

Grzegorz Deptuch, Gabriella Carinii, Gabriele Giacomini, Alessandro Tricoli Brookhaven National Laboratory

Leo Greiner, Nicole Apadula, Alberto Collu, Ernst Sichtermann Lawrence Berkeley National Laboratory

Thematic Areas: IF7: Electronics/ASICs IF3: Solid State Detectors and Tracking

Monolithic Active Pixel Sensors (MAPS) detectors have been postulated for charged particle tracking in the early 2000s [1] stimulated by a growing interest at that time in developing lepton colliders with an aim on the International Linear Collider (ILC). The MAPS detectors can be built rather inexpensively, even in large sizes of megapixel arrays, thinned as needed, offer high blooming threshold, individual pixel readout, radiation hardness, while operating at high speed with low power consumption, from a single and low voltage supply. Older-generation MAPS, such as those postulated early for the ILC and practically used in the Heavy Flavor Tracker (HFT) at STAR [2] are built on a low-resistivity substrate, forming the active sensitive volume (ASV) and in-situ signal/data processing is limited. This limitation results from the technological restriction of fabrication processes used for these early MAPS detectors. Simply, a lack of nested n-inside-p doping wells disallows complementary transistors in in-pixel processing circuit networks. Therefore, these early MAPS detectors, although able to offer high granularity and small material budget, are not suited for implementation of the systems requiring advanced timing, fast readout and resistance to radiation needed in the LHC experiments or for Electron Ion Collider.

# TJ 65 for tracking

- TJ 180nm process used with modifications fabricated in Israel

- deep-wells, EPI  $\rho$ =~500 $\Omega$ cm (HR option), EPI thickness limited to 8-10  $\mu$ m,

- New efforts TJ 65nm process fabricated in Japan (joint venture w. Panasonic

- Two main technology flavors(both available with HR epi<10 µm thick):</li>

- Imaging technology (ISC) and high-density CMOS (logic, rf...),

- Switch to TowerJazz 65 nm CMOS process (ITS2/ALPIDE: TowerJazz 180 nm)

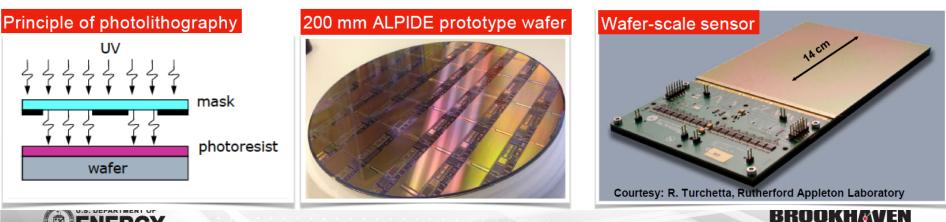

- needed mainly because of larger wafers: Ø=300 mm (180 nm process only available on Ø=200 mm wafers)

- Stitching, i.e. producing chips as big as the wafer

- More details about the sensor development in the *next talk by lain Sedgwick*

#### **TJ 65 for tracking** EOI – EIC Silicon Consortium

#### Please indicate the name of the contact person for this submission:

Leo Greiner

Lawrence Berkeley National Laboratory

lcgreiner@lbl.gov

Please indicate all institutions collectively involved in this submission of interest:

LBNL, BNL Instrumentation Division, University of Birmingham, Rutheford Appleton Laboratory, CCNU (Wuhan), JLAB.

We expect others to be joining soon.

Please indicate the items of interest for potential equipment cooperation:

The goal of this consortium is to develop a MAPS sensor and associated powering, support structures, control and ancillary parts as necessary to produce a detector solution for silicon tracking for the central tracking parts of an EIC detector. The consensus of opinion in the consortium is that the optimum path to realize this goal is to join the ITS3 effort at CERN and work to develop both the proposed ITS3 sensor technology that could be used for the vertexing layers at the EIC, and a very similar sensor optimized for deployment in the outer barrel and disc layers.

ENERGY Expression of Interest information session, 3<sup>rd</sup> Yellow Report Meeting, CUA, DC, 09/16-18/20

# Timing

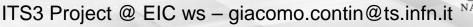

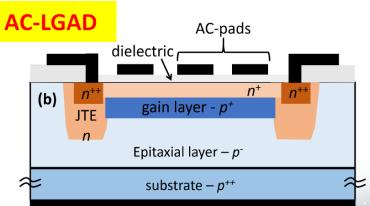

- Novel development: AC-coupling allows fine segmentation

- Time & Space measurements

- ➔ 100% fill factor

#### Main differences wrt LGADs:

- one large low-doped / high-ρ n<sup>+</sup> implant running overall the active area, instead of a high-doped low-ρ n<sup>++</sup>

- 1. A thin **insulator** over the  $n^+$ , where fine-pitch electrodes are placed.

- Signal is still generated by drift of multiplied holes into the substrate and AC-coupled through dielectric

- Electrons collect at the resistive n<sup>+</sup> and then slowly flow to ohmic contact at the edge.

- 100% Fill Factor and fast timing information at a per-pixel level both achieved!!!

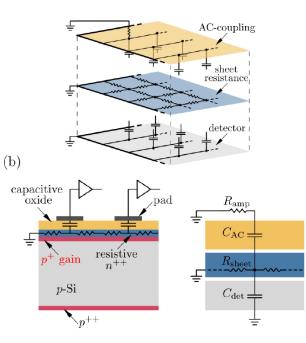

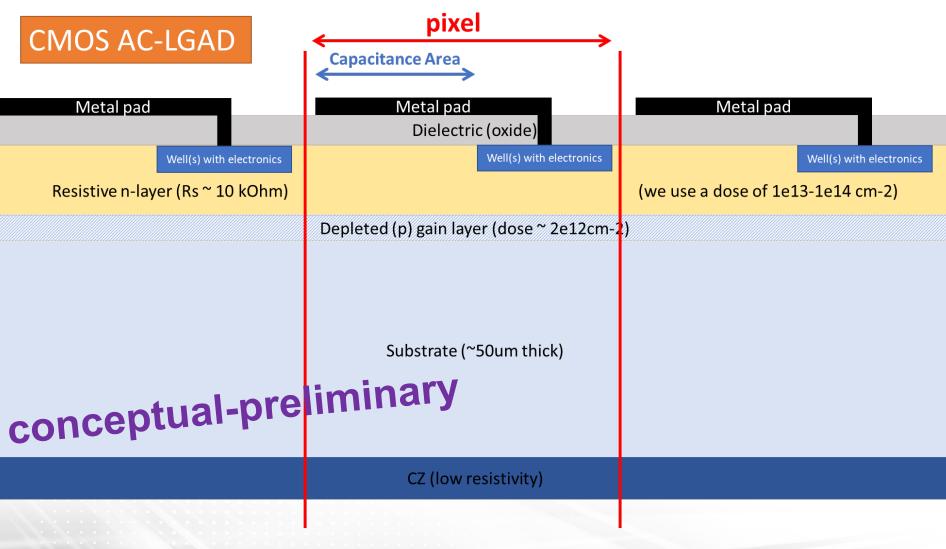

### TJ 65 for: monolithic AC LGADs

timing detectors

### Timing: monolithic AC LGADs

ROC (it provides the AC-metal for the sensor)

Dielectric (oxide)

Resistive n-layer (Rs ~ 10 kOhm)

Depleted (p) gain layer (dose ~ 2e12cm-2)

In this approach, the LGAD is made by BNL (or Hamamatsu) and the ROC is oxide bonded to the sensor

Substrate (~50um thick)

conceptual-preliminary

CZ (low resistivity)

#### May still combine hybridization

#### **Timing: monolithic AC LGADs** CMOS LGAD

### Conclusions

- MAPS as initially developed in early 2000s showed their limitations,

- Recently, an effort is emerging to develop new generation MAPS in TJ 65 nm CMOS imaging technology

- Improvements for making good monolithic (sensors + readout) has been known, simulated and sometimes demonstrated – inefficient is to get the adaptations to a mainstream CMOS process due to no market for foundries,

- MAPS built in adapted TJ process for ALICE ITS3, CERN Experimental Physics department R&D programme (WP1.2 MAPS) and are is technological platform for:

- EIC tracking (options are under consideration) and pixel for direct detection of electrons and X-ray photons.

- Timing detectors using built-in gain structures; this is under feasibility consideration if process features are suitable.

bent but functional ALPIDE