# **New Frontiers in On-Chip Image Processing**

### **Richard Younger**

This material is based upon work supported by the Defense Advanced Research Projects Agency (DARPA) and the Assistant Secretary of Defense for Research and Engineering under Air Force Contract No. FA8721-05-C-0002 and/or FA8702-15-D-0001. Any opinions, findings and conclusions or recommendations expressed in this material are those of the author(s) and do not necessarily reflect the views of the Assistant Secretary of Defense for Research and Engineering or the United States Government.

©2021 Massachusetts Institute of Technology.

Delivered to the U.S. Government with Unlimited Rights, as defined in DFARS Part 252.227-7013 or 7014 (Feb 2014). Notwithstanding any copyright notice, U.S. Government rights in this work are defined by DFARS 252.227-7013 or DFARS 252.227-7014 as detailed above. Use of this work other than as specifically authorized by the U.S. Government may violate any copyrights that exist in this work.

**CPAD Instrumentation Frontier Workshop 2021**

March 18-21, 2021

DISTRIBUTION STATEMENT A. Approved for public release. Distribution is unlimited.

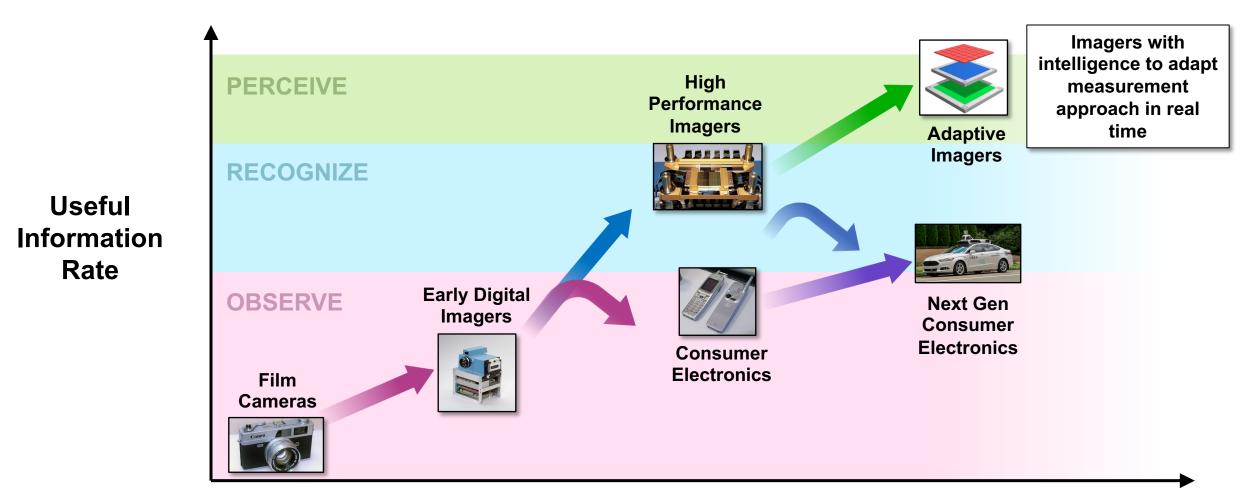

### **Evolution of High Performance Imagers**

Year

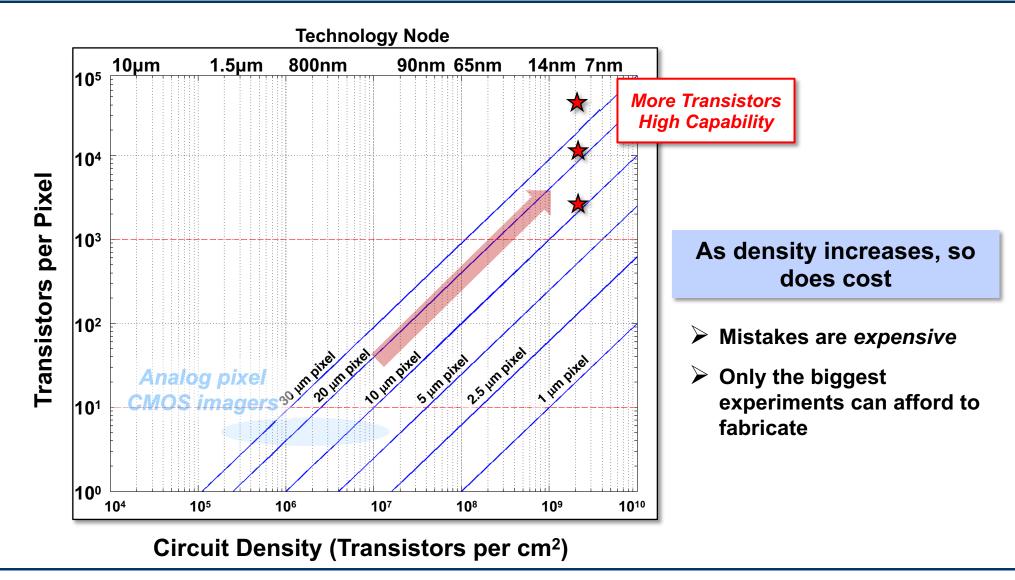

### **ROIC Fabrication Technology Landscape**

How can we bring advanced processing ROICs to more applications?

Increase hardware modularity and reconfigurability to reuse ROICs and amortize costs

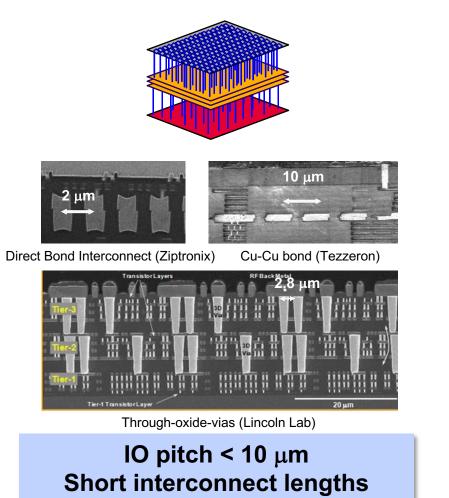

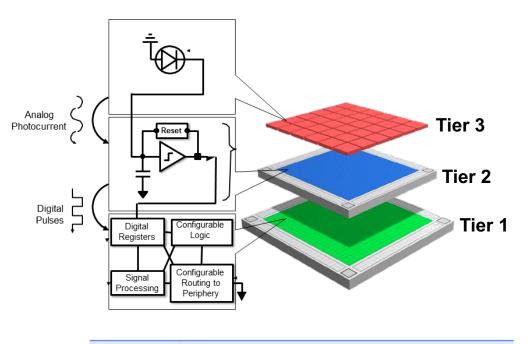

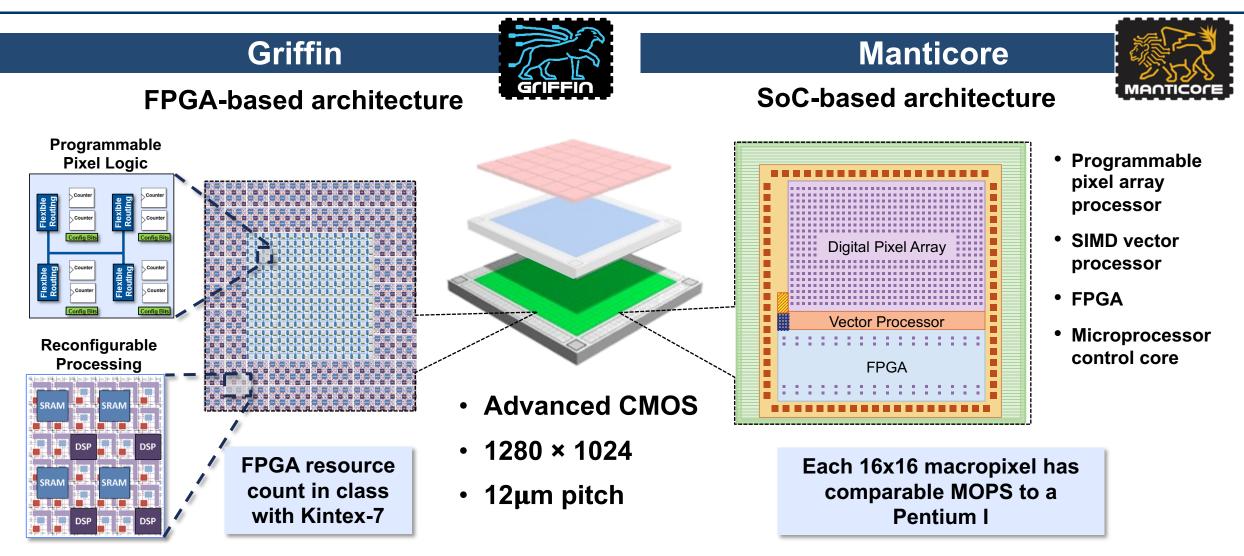

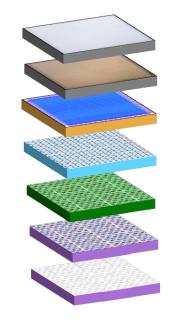

### Hardware Modularity: Split the ROIC

| Tier 3 | Waveband Specific Detector Array                                  |

|--------|-------------------------------------------------------------------|

| Tier 2 | Detector Specific Analog Interface                                |

| Tier 1 | Reconfigurable Digital Circuit with<br>Integrated FPGA Processing |

- Advanced CMOS

- 1280 × 1024

- 12µm pitch

## **Demonstrating Modularity and Reconfigurability**

## **Using Smart Imagers**

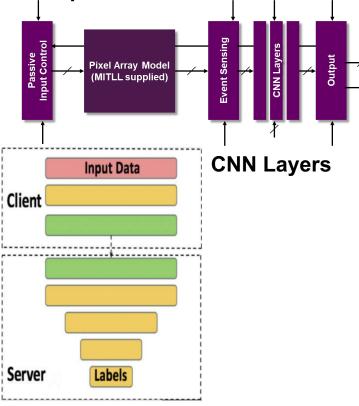

#### **Multimodal Sensing**

Self-trigger a change in sensing based on events

| . 8. 8. 8.<br>오          |  |  |  |  |  |  |  |

|--------------------------|--|--|--|--|--|--|--|

| solve<br>trol            |  |  |  |  |  |  |  |

| lime Resolved<br>Control |  |  |  |  |  |  |  |

| Ē                        |  |  |  |  |  |  |  |

| <u>96 - 96 - 96 - 96</u> |  |  |  |  |  |  |  |

| Passive<br>Control       |  |  |  |  |  |  |  |

| Event Sensing            |  |  |  |  |  |  |  |

| Output                   |  |  |  |  |  |  |  |

|                          |  |  |  |  |  |  |  |

#### Machine Learning

CNNs are feasible to implement on-chip

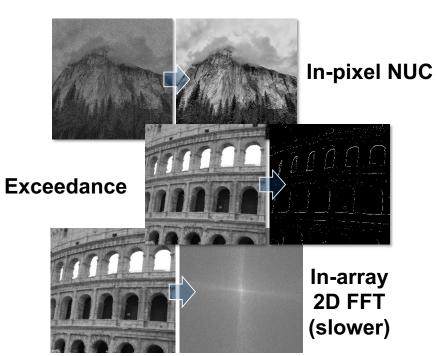

#### **Conventional Processing**

Many types of on-chip processing at rates in excess of 100,000 FPS

More sophisticated adaptive processing is possible in-pixel and in-array

### **Relmagine ROIC Status**

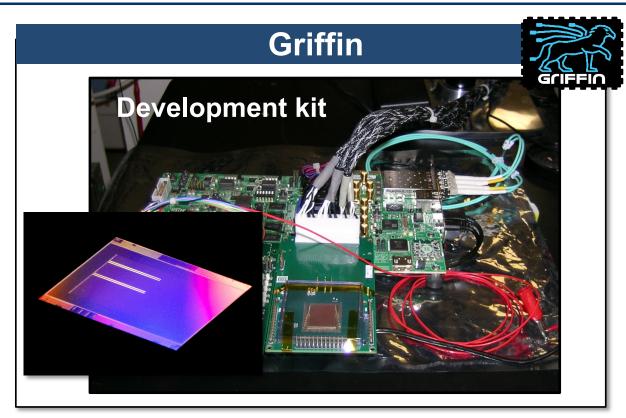

- Multiple partners with Griffin tier-2 chips

- Griffin T1-only hardware development kit shipped January 2021

- Multiple partners in process of tier 2 design

- Anticipate at least one bonded assembly to begin late 2021

- Demo camera in 2022

## What's next?

### **Near Future**

- Demonstration cameras

- Design refinement

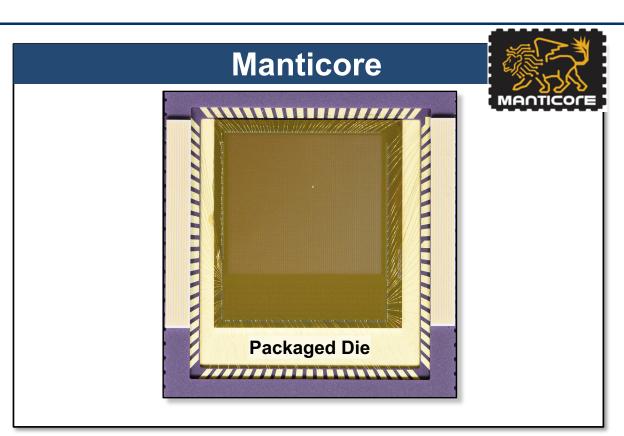

- Open to collaborations on Griffin & Manticore

- Open to studying needs for science & space applications

### Looking Ahead

- Is on-chip ML the path for perceptive imagers?

- Create deep stacking architectures for full modularity

- Abuttability

# **Thank You**

# younger@ll.mit.edu

## **MIT/LL Relmagine Team**

| Rich Younger             | Maria Blood     | Renee Lambert            | Tim Gagnon                |

|--------------------------|-----------------|--------------------------|---------------------------|

| Valerie Finnemeyer       | Glenn Garvey    | Donna Yost               | Erik Duerr                |

| Jon Frechette            | Kate Gillis     | Sandra Lee               | Eric Dauler               |

| Sue Burzyk               | Philemon Chose  |                          | Dan Ripin                 |

| Brian Tyrrell            |                 | Hannah Whisnant          | Kaitlyn Dixon             |

|                          | Kate Thurmer    | Praneeth Vepakomma (MIT) | Stephan Chase             |

| Matt Stamplis            | Jordan Lahanas  | Tom Karolyshyn           | Kenny Sims                |

| Jonathan Leu             | Tom Ross        | Greg Rowe                | Elaine Swenson            |

| Peter Grossmann          | lan Brown       |                          |                           |

|                          |                 | Farhan Adil              |                           |

| Matt Gregory             | Tony Kryzak     | Phillip Bailey           |                           |

| George Jordy             | Austin Holloway | Hernan Castro            | Designing and             |

| Tom Cheng                | Tony Soares     | Dan Santiago             | producing these chips     |

| Jim Wey                  | David Volfson   | Domenic Terranova        | is the product of a large |

| Alice Lee                | Jerry Lipson    |                          | team of professionals     |

|                          | Tom Ferguson    | Tim Smith                |                           |

| Ana-Maria Mandrila Vacca | Mike Cooper     | Dmitriy Kaplan           |                           |

| Brian Yu                 |                 | Bob D'Ambra              |                           |

|                          |                 |                          |                           |

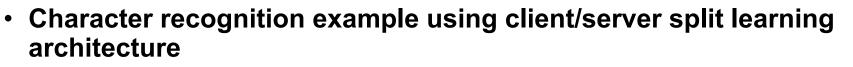

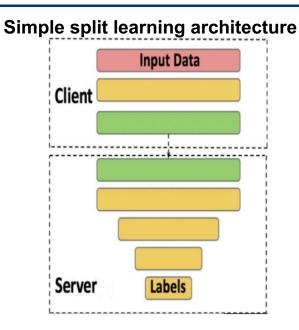

- Split learning separates input data from full body of inference network

- Used hls4ml to translate character recognition split learning model in Keras to Vivado HLS

- Results: This model should, with further optimizations, fit on Griffin

- Need to investigate network compression (pruning) & DSP re-use

- 2D convolutional layers were a challenge for hls4ml (as of v0.1.6)

| Split Learning Model | Kintex UltraScale 115           | Griffin FPIA                                         |  |  |  |

|----------------------|---------------------------------|------------------------------------------------------|--|--|--|

| 92,395               | 663,390                         | 275,032                                              |  |  |  |

| 634*                 | 702                             | 275                                                  |  |  |  |

| 3,286                | 5,530                           | 1,736                                                |  |  |  |

| 60.5                 | 2,160                           | 820                                                  |  |  |  |

| * Includes image     |                                 |                                                      |  |  |  |

|                      | 92,395<br>634*<br>3,286<br>60.5 | 92,395 663,390   634* 702   3,286 5,530   60.5 2,160 |  |  |  |

#### **Character Recognition Model FPGA Resource Utilization**

CPAD 2021 - 13 RDY MM/DD/YY Whisnant, H. K. (2020). Split learning on FPGAs (Master's Thesis, Massachusetts Institute of Technology). Duarte et al., "Fast inference of deep neural networks in FPGAs for particle physics", <u>JINST 13 P07027</u> (2018), arXiv:1804.06913.

LINCOLN LABORATORY MASSACHUSETTS INSTITUTE OF TECHNOLOGY