####

## **ASIC Design and Development**

Paul Rubinov 2021 All Engineers Retreat 24 Feb

## The Fermilab ASIC Group

Application Specific Integrated Circuits

The history of ASIC design for HEP is tied to the development of Si strip detectors. The first Fermilab ASIC : QPA02 (Quad Preamp), bipolar, semi-custom

First Si strip detector at CERN NA11 (1981) 60um readout pitch, 400 chan Readout > 1 sq meter

R. Yarema, "ASIC Design at Fermilab", FERMILAB-Conf-91/170

## Need for collider detectors drives full custom design in CMOS

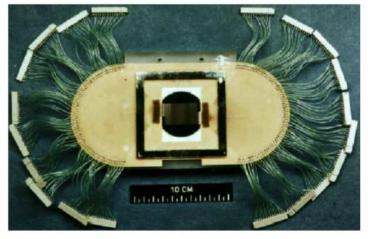

- By 2005, Fermilab ASIC group is BUSY

- 5 (!) ASIC engineers + Analog and Digital + Test engineers

- Many projects, most in TSMC 0.25um (250nm)

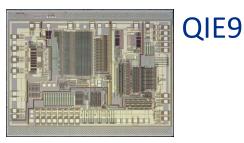

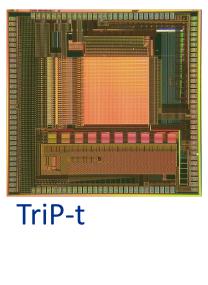

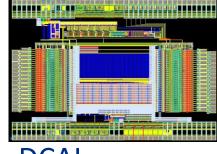

DCAL

RMCC

+SVX4 +MASDA(X) +APD RO (NOvA) Going to 130nm **CFermilab**

## Today

| J. Hoff            | S. Li |

|--------------------|-------|

| C. Gingu           | -     |

| A. Shenai          | I     |

| C. Syal            |       |

| <b>R. Wickwire</b> |       |

| (M. Hammer)        |       |

i T. England H. Sun X. Wang

G. Drake D. Braga Q. Sun T. Zimmerman **F. Fahim** Deputy Head Quantum Science Program, FQI

• + Test engineers, IT support, firmware support etc.

## **The power of Integrated Circuits**

• Moore and friends – digital scaling

| Scaled Parameters                  | Constant field Scaling                   |

|------------------------------------|------------------------------------------|

| $t_{ox}, L, W, X_j, W_d$           | 1/κ                                      |

| $N_a, N_d$ (ions/cm <sup>3</sup> ) | к                                        |

| Power supply: $(V_{dd})$           | 1/~                                      |

| Electric field in device: ( $E$ )  | 1                                        |

| Capacitance: (C)                   | 1/~                                      |

| Inversion charge density $(Q)$     | 1                                        |

| Circuit delay time: $T  CV_I$      | 1/~                                      |

| Power dissipation: $(P)$           | 1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/ |

| Power density $(\sim P_A)$         | 1                                        |

| Circuit density                    | ĸ <sup>2</sup>                           |

| Chip Area (A)                      | 1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/1/ |

|                                    |                                          |

| MOSFET scaling |

|----------------|

| (process nodes |

| 10 µm – 1971   |

| 6 µm – 1974    |

| 3 µm – 1977    |

| 1.5 µm – 1981  |

| 1 µm – 1984    |

| 800 nm – 1987  |

| 600 nm – 1990  |

| 350 nm – 1993  |

| 250 nm – 1996  |

| 180 nm – 1999  |

| 130 nm – 2001  |

| 90 nm – 2003   |

| 65 nm – 2005   |

| 45 nm – 2007   |

| 32 nm – 2009   |

| 22 nm – 2012   |

| 14 nm – 2014   |

| 10 nm – 2016   |

| 7 nm - 2018    |

| 5 nm - 2020    |

| Future         |

| 3 nm ~ 2022    |

| 2 nm ~ 2024    |

|                |

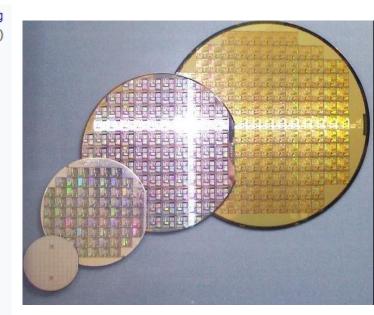

#### 4in wafer $\rightarrow$ 300mm wafer

## Moore's law cont.

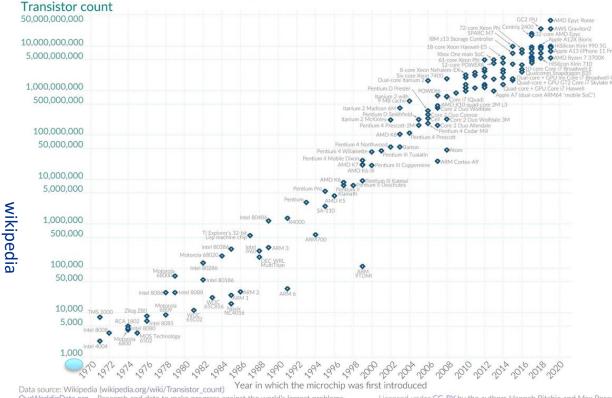

Moore's Law: The number of transistors on microchips doubles every two years Our World in Data

Moore's law describes the empirical regularity that the number of transistors on integrated circuits doubles approximately every two years. This advancement is important for other aspects of technological progress in computing – such as processing speed or the price of computers.

## 1990: \$25K for prototype run

## 2020: \$40K for 55nm GF for 9mm<sup>2</sup> (50 chips)

OurWorldinData.org - Research and data to make progress against the world's largest problems.

Licensed under CC-BY by the authors Hannah Ritchie and Max Roser.

## **Analog scaling**

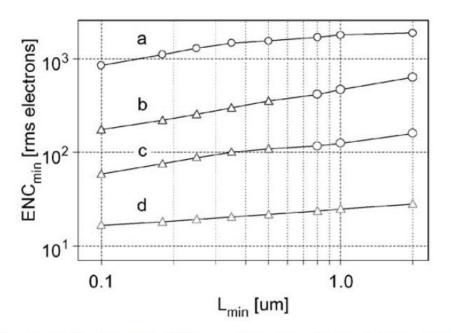

# P. O'Connor and G. De Geronimo Prospects for charge sensitive amplifiers in scaled CMOS NIM A 480 (2002) 713-725 Written exactly 20 yrs ago

| System | ystem $C_{det}$ $t_s$ $P$ $I_{leak}$ Detector |                       |      |       |               |

|--------|-----------------------------------------------|-----------------------|------|-------|---------------|

| System | $C_{\text{det}}$                              | <sup>1</sup> S        | 1    | Ileak | Detector      |

| а      | 30                                            | 75                    | 10   | 0.001 | Wire chamber  |

| b      | 15                                            | 25                    | 0.2  | 10    | Si Strip      |

| с      | 0.3                                           | 25                    | 0.02 | 1     | Si Pixel      |

| d      | 3                                             | 2500–500 <sup>a</sup> | 10   | 0.01  | Semiconductor |

| UNITS  | pF                                            | ns                    | mW   | nA    |               |

Table 2

System parameters for ENC scaling simulation

<sup>a</sup> For this system, the shaping time was varied at each  $L_g$  to optimize the overall noise (i.e., to make the white series noise and parallel noise equal).

Typical application

Tracking, imaging

Tracking Tracking Spectroscopy

## Analog scaling cont.

Fig. 6. Optimum total ENC as a function of the minimum gate length. Curves (a-d) refer to the system parameters given in Table 2. Circles = NMOS, triangles = PMOS.

## **ADC** scaling

|            | 0 to 14 bit,<br>0MSPS | FOM <sup>:</sup><br>*freq | = Power/(2^ENOB<br>) |

|------------|-----------------------|---------------------------|----------------------|

| Technology | Year                  | Area (sq mm)              | FOM (fJ/step)        |

| 250nm      | 2010                  | 4.5                       | 344                  |

| 180nm      | 2012                  | 0.5                       | 89                   |

| 130nm      | 2012                  | 0.24                      | 31                   |

| 65nm       | 2012                  | 0.19                      | 46                   |

| 28nm       | 2015                  | 0.047                     | 13                   |

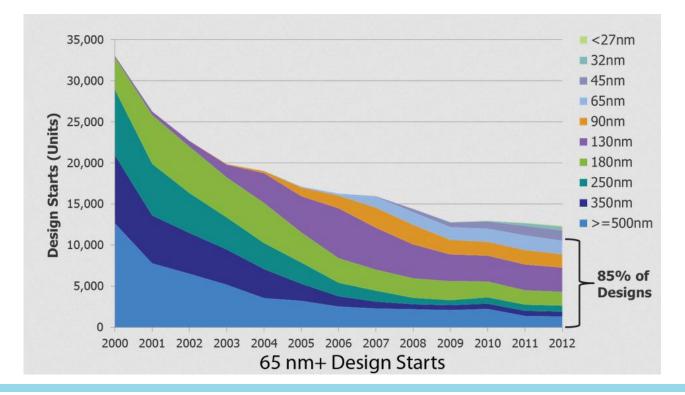

## **The power of Application Specific**

Moore's law does not drive design decisions

#### Functionality

#### Complexity

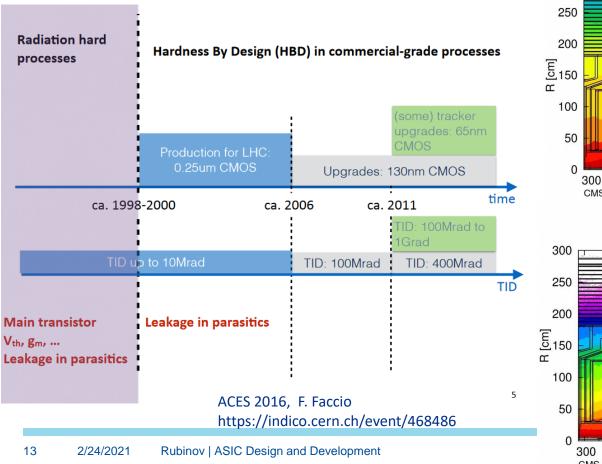

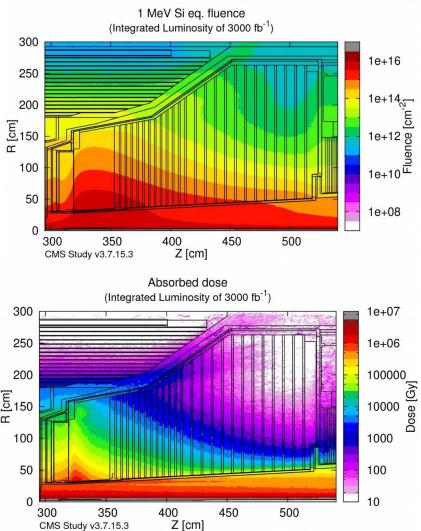

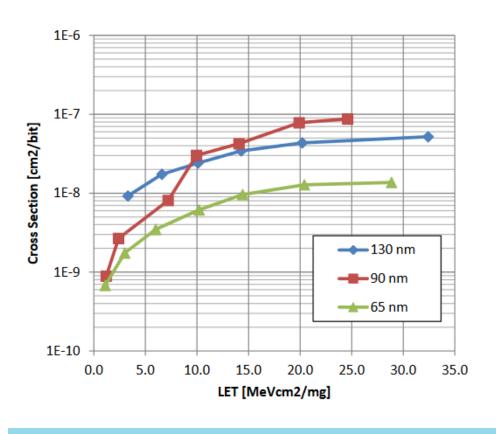

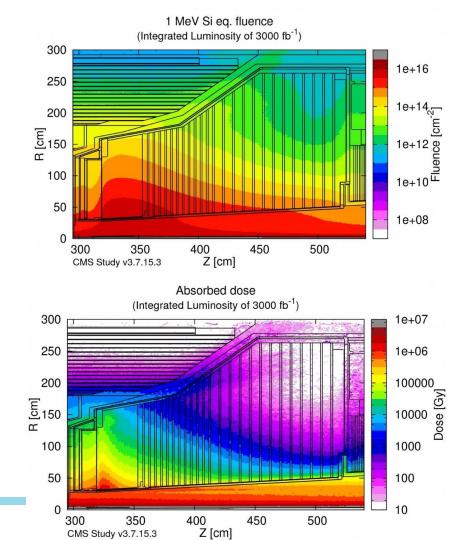

## **Need for Extreme Environments**

## **Need for Extreme Environments**

## **Need for Extreme Environments**

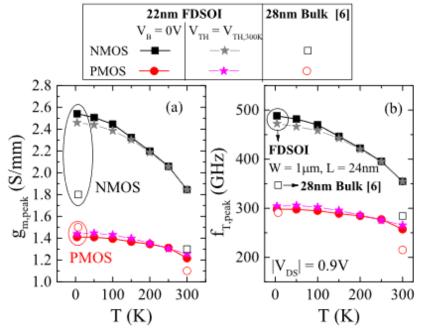

E TRANSACTIONS ON ELECTRON DEVICES, VOL. 67, NO. 11, NOVEMBER 2020

#### Performance and Low-Frequency Noise of 22-nm FDSOI Down to 4.2 K for Cryogenic Applications

Bruna Cardoso Paz<sup>©</sup>, Mikaël Cassé<sup>©</sup>, *Member, IEEE*, Christoforos Theodorou, Gérard Ghibaudo<sup>©</sup>, *Fellow, IEEE*, Thorsten Kammler, Luca Pirro, Maud Vinet, *Senior Member, IEEE*, Silvano de Franceschi, Tristan Meunier, and Fred Gaillard

(Invited Paper)

Fig. 5. (a)  $g_{m,peak}$  versus *T* and (b)  $f_{T,peak}$  versus *T* for nMOS and pMOS, at  $V_B = 0$  V and at  $V_B$  needed to keep  $V_{TH}$  constant =  $V_{TH,300K}$ .  $|V_{DS}| = 0.9$  V.

🛟 Fermilab

## Projects within the ASIC group (current, recent and near future)

CMS Upgrades ECON-T and ECON-D: data concentrators for trigger and DAQ paths of HGCAL ETROC: precision timing for MIPs in the forward region using LGADs

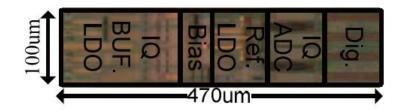

DUNE Cold electronics **COLDADC**: (with LBNL and BNL) 16ch, 12 bit, 2 MSPS ADC **COLDATA**: "Digital-on-Top" leveraging FNAL cold models. <1E-15 BER @25m and1.28gbps

## Projects within the ASIC group (current, recent and near future)

Quantum projects MIDNA: readout of Skipper CCDs to allow large number of channels SNSPD: readout of Superconducting Nanowire Single Photon Detector (part of QuantISED) ACC1: Atomic Clock Control – shrinking Atomic Clocks to be chip sized (part of QuantISED) CITC1: Cryo-electronics Ion Trap control for Qubits and other quantum applications CryoADC: Collaboration with Microsoft, component for quantum computing Skipper in CMOS (R&D) : extending Skipper technology to CMOS sensors SiSeRO (R&D) : Joint development with MIT LL to extend Skipper technology to MIT-LL process

Other:

FALCON: High speed Xray camera for APS upgrade at ANL

VIPRAM (130nm): 3D CAM (Vertically Integrated Pattern Recognition Associative Memory)

## **Take Home Message**

One Size does NOT fit all.

Fermilab ASIC group is here to do apply expertise in

## **Integrated Circuits to our Specific Applications**

🗱 Fermilab

### BACKUP

19 2/24/2021 Rubinov | ASIC Design and Development

## **Backup: MPW prices from Europractice**

#### **GLOBALFOUNDRIES**

| Technology                               | Standard<br>EUR / mm <sup>2</sup> | Discounted<br>EUR / mm <sup>2</sup> |

|------------------------------------------|-----------------------------------|-------------------------------------|

| GLOBALFOUNDRIES SIGE 8HP                 | 3,800                             | 3,600                               |

| GLOBALFOUNDRIES 130 nm BCDlite           | 1,500 <sup>2</sup>                | 1,400 <sup>2</sup>                  |

| GLOBALFOUNDRIES 130 nm LP                | 1,500 <sup>2</sup>                | 1,400 <sup>2</sup>                  |

| GLOBALFOUNDRIES 90WG Silicon Photonics   | 5,250                             | 5,000                               |

| GLOBALFOUNDRIES 55 nm LPx-NVM/LPx-RF     | 4,000 <sup>2</sup>                | 3,800 <sup>2</sup>                  |

| GLOBALFOUNDRIES 55 nm LPe                | 4,000 <sup>2</sup>                | 3,800 <sup>2</sup>                  |

| GLOBALFOUNDRIES 45RFSOI                  | 7,350 <sup>2</sup>                | 7,000 <sup>2</sup>                  |

| GLOBALFOUNDRIES 40 nm LP/LP-RF/RF-mmWave | 5,000 <sup>2</sup>                | 4,700 <sup>2</sup>                  |

| GLOBALFOUNDRIES 28 nm SLP/SLP-RF         | 10,200 2                          | 9,700 <sup>2</sup>                  |

| GLOBALFOUNDRIES 22 nm FDSOI              | 14,000 <sup>2</sup>               | 13,200 <sup>2</sup>                 |

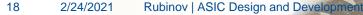

## **BACKUP: QPA02**

4 chan Gain = 17mv/fC ENC = 1600e @ 20pF Rise = 6 ns Falltime = 12ns Power = 42 mw/channel

## **QPA02** Schematic Diagram

R. Yarema, "ASIC Design at Fermilab", FERMILAB-Conf-91/170

🛟 Fermilab