# Wire-Cell TPC simulation for VD update

#### Previous works:

- Initial Field Response simulation for 50L

- 2-view geometry ported to Wire-Cell format

- initial configuration for standalone Wire-Cell

#### Ref:

- Brett's talk <a href="https://indico.fnal.gov/event/47321/contributions/206217/">https://indico.fnal.gov/event/47321/contributions/206217/</a>

- Andrea's talk <a href="https://indico.fnal.gov/event/46502/contributions/206716/">https://indico.fnal.gov/event/46502/contributions/206716/</a>

#### **Update: LArSoft integration**

- currently focusing on making the full chain work

- more tuning/debugging/enhancing later

- status: initial integration done for sim-SP chain

- https://github.com/HaiwangYu/wire-cell-toolkit/blob/dune-vd/cfg/pgrapher/experiment/dune-vd/

### Initial check of the TPC simulation

- For now, use sim::SimEnergyDeposit from dune10kt-1x2x6 (HD)

- Will try V. Galymov's simulation for VD later.

- geom: https://github.com/WireCell/wire-cell-data/blob/master/dunevd-wires-twoplanes.json.bz2

- field resp.: <a href="https://www.phy.bnl.gov/~bviren/tmp/pcbro/pcbro-response-latest.tar">https://www.phy.bnl.gov/~bviren/tmp/pcbro/pcbro-response-latest.tar</a>

- fcl: <a href="https://github.com/HaiwangYu/wire-cell-toolkit/blob/dune-vd/cfg/pgrapher/experiment/dune-vd/wcls-sim-drift-simchannel.fcl">https://github.com/HaiwangYu/wire-cell-toolkit/blob/dune-vd/cfg/pgrapher/experiment/dune-vd/wcls-sim-drift-simchannel.fcl</a>

# CRM 1 CRM 7 CRM 0 CRM 6 Plane 0 0.520 cm 150 cm

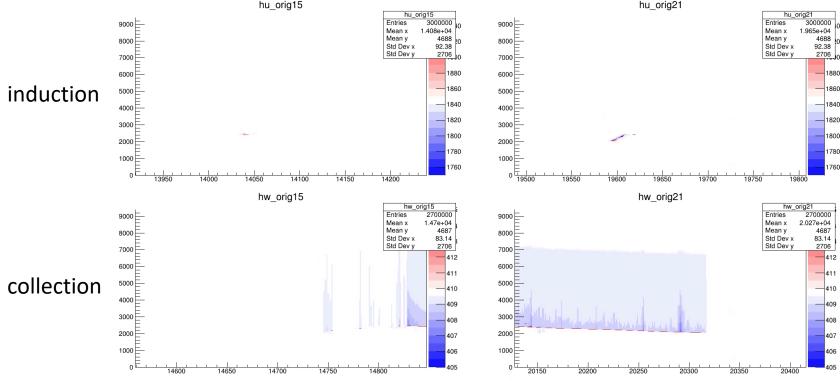

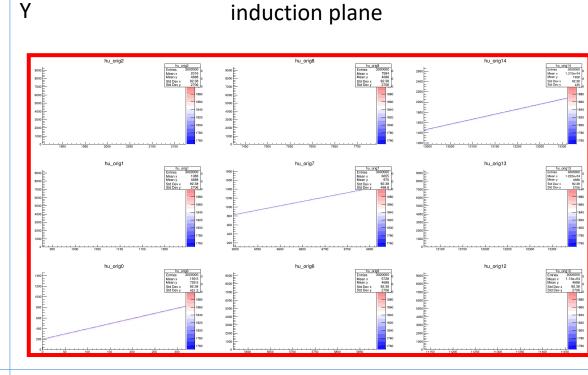

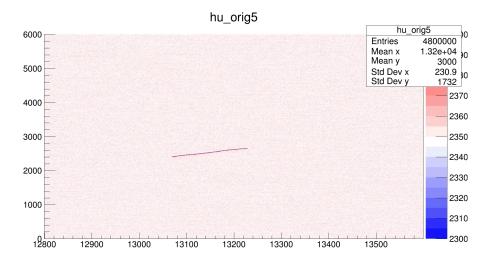

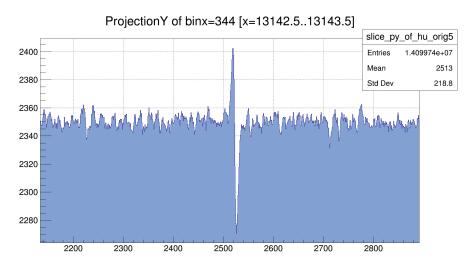

### mu-simulated from the HD hu\_orig15

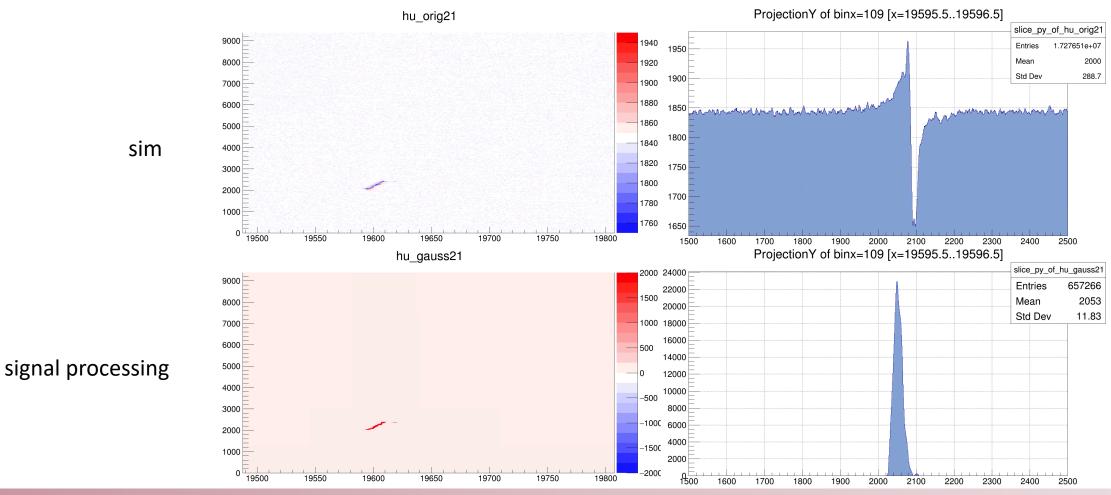

# Initial check of the Signal Processing

- noise model from ProtoDUNE-SP

- working with B. Yu on new model for VD

- filters and other tunings are also from ProtoDUNE-SP

- initial check, more tuning undergoing

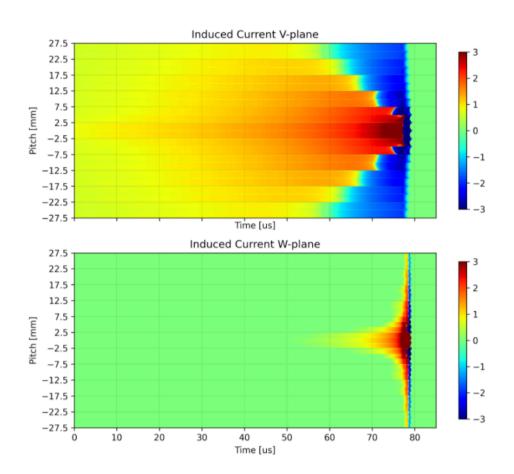

# Field Response

- Currently using the one calculated for the 50L Prototype using the "2.5D" method by Y. Li and B. Viren

- using this as placeholder

- more in <u>B. Viren's talk in last FD sim/reco meeting</u>

- F. Pietropaolo and B. Viren are working on new procedures and for FD

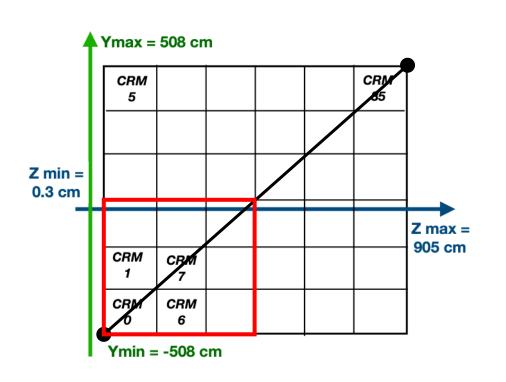

# Geometry

- Currently using 2-view version ported using the gdml from V. Galymov

- Work from A. Scarpelli

- Working on porting <u>V. Galymov's 3-view geometry</u>

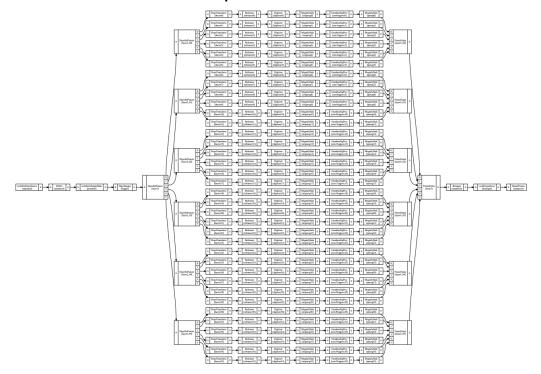

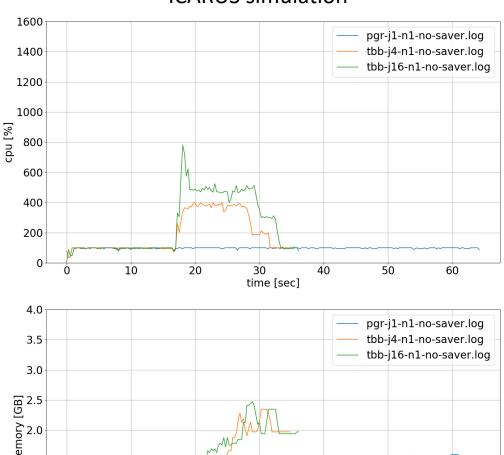

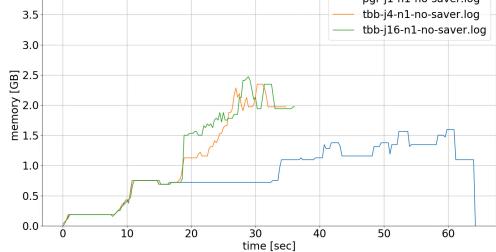

# Wire-Cell Graph and Multi-threading

- Task level multi-threading using TBB

- like LArSoft

- Memory-CPU load balancing

#### WC Graph for FD VD simulation

#### **ICARUS** simulation

### Summary

#### Initial integration with LArSoft done

- TPC sim + signal processing

- https://github.com/HaiwangYu/wire-cell-toolkit/tree/dunevd/cfg/pgrapher/experiment/dune-vd

### Will gradually update the placeholders:

- Field Response

- 3-view geometry

- Noise model

#### Validations:

- geometry

- sim::SimChannel

- raw::RawDigit

Further tunings and optimizations

# DUNE 10kt 1x2x6 workspace

#### Work form Wengiang Gu:

- full gen-g4-tpcsim chain working with dune v09\_10\_00

- seems to have issues with latest v09\_16\_00, working on it

- validation from the collaboration is very welcome

gen: prod\_muminus\_0.1-5.0GeV\_isotropic\_dune10kt\_1x2x6.fcl

g4: supernova\_g4\_refactored\_dune10kt\_1x2x6.fcl

/dune/app/users/wgu/larsoft/v09\_12\_00/srcs/dunetpc/fcl/dunefd/g4/standard\_g4\_refactore d\_dune10kt.fcl

TPC Sim: opdet\_multidetsim\_refactored\_dune10kt\_1x2x6.fcl

wire-cell-cfg/pgrapher/experiment/dune10kt-1x2x6/wcls-simdrift-simchannel.jsonnet

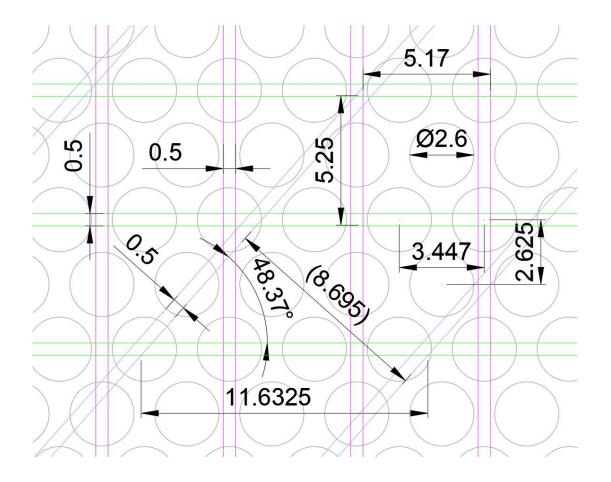

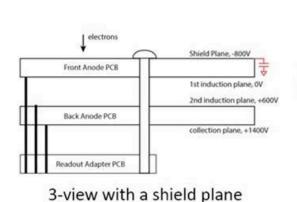

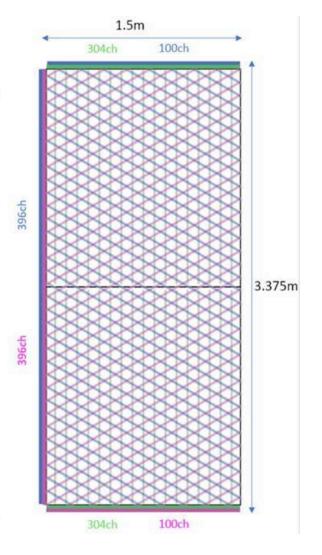

#### New 3V Reference Design(?)

- The layout shown here has a total channel count of 3200. The holes are 2.823mm apart on an equilateral triangular pattern. Hole size is 2.3mm (0.5mm min wall thickness).

- The collection strips are perpendicular to the beam @ 4.89mm pitch. The two induction plane strips are ±30° w.r.t. the beam @ 7.335mm pitch.

- The nominal gap width is 0.5mm, always splitting a row of holes in equal halves.

- If we implement a shield layer as the first plane facing the cathode, both anode PCBs will be perforated with the same pattern (60% open), with the holes aligned.

- · The shield efficiency could be up to 95%.

Ø2.3 1,89 4.89

```

!! The following modules have been misconfigured: !!

Module label: PDFastSim

module_type : PDFastSimPAR

Any parameters prefaced with '#' are optional.

Missing parameters:

DoReflectedLight: <bool>

IncludePropTime: <bool>

UseLitePhotons: <bool>

OpaqueCathode: <bool>

OnlyOneCryostat: <bool>

VUVHits: << delegated >>

```