# **DUNE Ethernet Readout**100G UDP IP CORE

Rob Halsall

Matt Roberts

Chris Lyford

14-10-2021

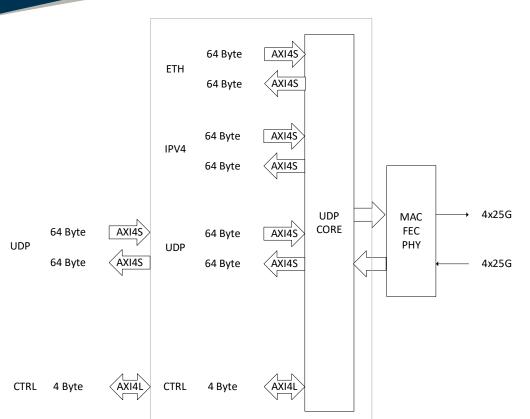

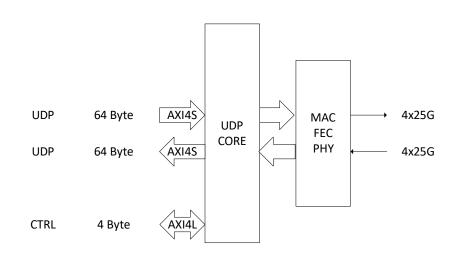

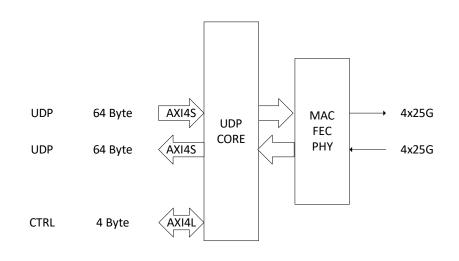

#### 100G UDP Core

- Parameterised & Scalable

- UDP plus extendable via ETH & IPV4 ports

- ARP & PING compile options

- Control Registers Mem Mapped via AXI4L

- UDP Tx & Rx via AXI4S

- Uses TKEEP to allow 'any' packet size

- Supports Jumbo frames

- Optional 'Farm Mode' on Tx Channel using TID

- Traffic Filter on Rx Channel

- Clocks AXI4S ~195MHz & PHY ~322MHz

- Wrap to hide excess functionality

#### 100G UDP Core

- AXI4S

- 64Byte @ 195MHz nominal

- AXI4S Tx data frame -> Outgoing UDP packet

- Incoming UDP packet -> AXI4S Rx data frame

- Loopback will return tx data frame on rx channel

#### 100G UDP Core

AXI4L

xml file – flat memory map

- Approximately 32x 32 bit Control Registers

- Source & destination addresses mac/ip/port

- Rx Filter settings

- Stats registers

- ...

- Tx Channel Farm Mode RAM

- 256 entry mac/ip/port table

- Selected by Tx AXI4S 8 bit TID signal

- mac entries can be arp populated

# 100G UDP Core – Entity/generic

```

G FPGA VENDOR

: string := "xilinx";

--! Selects the FPGA Vendor for Compilation

: string := "all";

G FPGA FAMILY

--! Selects the FPGA Family for Compilation

G FIFO IMPLEMENTATION : string := "auto";

--! Selects how the Fitter implements the FIFO Memory

G FIFO TYPE

: string := "inferred mem"; --! Selects how to implement the Core's FIFOs

--! Number Of Positions In ARP Table

G NUM OF ARP POS

: natural := 32;

: boolean := false;

--! Generate Clk Crossing FIFOs At The I/O of UDP Payloads

G UDP CLK FIFOS

G EXT CLK FIFOS

: boolean := false;

--! Generate Clk Crossing FIFOs At The I/O of Unsupported Packet Types

G TX EXT IP FIFO CAP

: integer := 2048;

--! Capacity In Bytes Of Uns IPV4 Protocol Packets FIFOs in Tx Path

G TX EXT ETH FIFO CAP

--! Capacity In Bytes Of Uns Ethernet Type Packets FIFOs in Tx Path

: integer := 2048;

G TX OUT FIFO CAP

: integer := 2048;

--! Capacity Of FIFO at End Of Tx Path. Necessary For 100GbE, Less Important for 1/10GbE. Can Be 0.

G RX IN FIFO CAP

: integer := 2048;

--! Capacity Of FIFO at Start Of Rx Path. At least 16 Words Recommended.

G RX INPUT PIPE STAGES : integer := 1;

--! Pipeline Stages From External MAC/PHY To Rx Path

--! Generate Logic For Internal Ping Replies

: boolean := true;

G INC PING

: boolean := true;

G INC ARP

--! Generate Logic For Interal ARP Requests And Replies

--! KHz Of Tx Path, Used For ARP Refresh Timers, Not Essential

G CORE FREQ KHZ

: integer := 322262;

G INC ETH

: boolean := false;

--! Generate Logic To Transmit Externally Provided Ethernet Payloads

G INC IPV4

: boolean := false

--! Generate Logic To Transmit Externally Provided IPV4 Payloads

```

Porting across Vendor/families requires wrapped/configured/licensed mac/fec/phy

#### 100G UDP Core - Entity/Ports/UDP AXI4S

```

-- AXI4-Stream UDP Transmit Data:

: in std logic;

--! UDP Tx In Clk

udp axis s clk

udp axis s reset : in std logic;

--! UDP Tx In Reset

udp axis s tdata : in std logic vector (511 downto 0); --! UDP Transmit Axi4s

udp axis s tvalid : in std logic;

--! UDP Transmit Axi4s

udp axis s tkeep : in std logic vector(63 downto 0); --! UDP Transmit Axi4s

udp axis s tlast : in std logic;

--! UDP Transmit Axi4s

udp axis s tid : in std logic vector(7 downto 0);

--! UDP Transmit Axi4s, route packets via LUT entry using this signal & Farm Mode

udp axis s tuser : in std logic vector(31 downto 0); --! UDP Transmit Axi4s

udp axis s tready : out std logic;

--! UDP Transmit Axi4s

-- AXI4-Stream UDP Receive Data:

udp axis m clk : in std logic;

--! UDP Rx Out Clk

udp axis m reset : in std logic;

--! UDP Rx Out Reset

udp axis m tdata : out std logic vector (511 downto 0); --! UDP Receive Axi4s

udp axis m tvalid : out std logic;

--! UDP Receive Axi4s

udp axis m tkeep : out std logic vector(63 downto 0); --! UDP Receive Axi4s

udp axis m tlast : out std logic;

--! UDP Receive Axi4s

udp axis m tid : out std logic vector(7 downto 0); --! UDP Receive Axi4s

udp axis m tuser : out std logic vector(31 downto 0); --! UDP Receive Axi4s

udp axis m tready : in std logic;

```

Non-record structure AXI4S Wrapper – required for IP Packaging/Vitis

#### 100G UDP Core - Entity/Ports/PHY AXI4S

```

tx core clk

: in std logic;

--! Tx Path Main Clock, Set To PHY Tx Clk or Set to Lower Clk and Buffer Full Packets Before PHY

: in std logic;

--! Rx Path Main Clock, can set to PHY Rx Clock, or any f down to ~200MHz

rx core clk

-- AXI4-Stream Slave Side (UDP Core Tx Data):

rx axis s clk

: in std logic;

--! UDP Core Rx PHY Clock

rx axis s rst : in std logic;

--! UDP Core Rx Active-High Reset

rx axis s tdata : in std logic vector(511 downto 0); --! Rx Axi4s Signals From PHY

rx axis s tvalid : in std logic;

--! Rx Axi4s Signals From PHY

rx axis s tkeep : in std logic vector(63 downto 0); --! Rx Axi4s Signals From PHY

rx axis s tlast : in std logic;

--! Rx Axi4s Signals From PHY

: in std logic vector(7 downto 0);

--! Rx Axi4s Signals From PHY (unused)

rx axis s tid

rx axis s tuser : in std logic vector(31 downto 0);

--! Rx Axi4s Signals From PHY (unused)

rx axis s tready : out std logic;

--! Rx Path Backpressure, only used for debugging

-- AXI4 Stream Master Out (UDP Core Rx Data):

tx axis m clk : in std logic;

--! UDP Core Tx PHY Clock

tx axis m rst : in std logic;

--! UDP Core Tx Active-High Reset

tx axis m tdata : out std logic vector(511 downto 0); --! Tx Axi4s Signals To PHY

tx axis m tvalid : out std logic;

--! Tx Axi4s Signals To PHY

tx_axis_m_tkeep : out std_logic vector(63 downto 0); --! Tx Axi4s Signals To PHY

tx axis m tlast : out std logic;

--! Tx Axi4s Signals To PHY

: out std logic vector (7 downto 0); --! Tx Axi4s Signals To PHY (unused)

tx axis m tid

tx axis m tuser : out std logic vector(31 downto 0); --! Tx Axi4s Signals To PHY (unused)

tx axis m tready : in std logic;

--! Tx PHY Backpressure, USED

```

- Interface to Wrapped MAC/FEC/PHY

- Non-record structure AXI4S Wrapper required for IP Packaging/Vitis

#### 100G UDP Core - Entity/Ports/AXI4L

```

-- AXI4-Lite Interface (defined in axi4lite pkg):

: in std logic;

--! AXI4-Lite Clock

axi4lite aclk

axi4lite aresetn : in std logic;

--! AXI4-Lite Active-Low Asynchronous Reset

axi4lite araddr : in std logic vector(31 downto 0); --! Axi4-Lite Signals

axi4lite awaddr : in std logic vector(31 downto 0); --! Axi4-Lite Signals

axi4lite arvalid : in std logic;

--! Axi4-Lite Signals

axi4lite awvalid : in std logic;

--! Axi4-Lite Signals

axi4lite bready : in std logic;

--! Axi4-Lite Signals

axi4lite rready : in std logic;

--! Axi4-Lite Signals

axi4lite wdata : in std logic vector(31 downto 0); --! Axi4-Lite Signals

axi4lite wstrb : in std logic vector(3 downto 0); --! Axi4-Lite Signals

axi4lite wvalid : in std logic;

--! Axi4-Lite Signals

axi4lite arready : out std logic;

--! Axi4-Lite Signals

axi4lite awready : out std logic;

--! Axi4-Lite Signals

axi4lite bresp : out std logic vector(1 downto 0); --! Axi4-Lite Signals

axi4lite bvalid : out std logic;

--! Axi4-Lite Signals

axi4lite rdata : out std logic vector(31 downto 0); --! Axi4-Lite Signals

: out std logic vector(1 downto 0); --! Axi4-Lite Signals

axi4lite rresp

axi4lite rvalid : out std logic;

--! Axi4-Lite Signals

axi4lite wready : out std logic;

--! Axi4-Lite Signals

```

Non-record structure AXI4L Wrapper – required for IP Packaging/Vitis

#### 100G UDP Core

**UDP** Core

IDP Sneeds

Instantiating the Core

Memory Map

Rx Path

restbench

Tx Path

----

Doxygen Index

Docs » UDP Core

View page source

Science & Technology Facilities Council

#### **UDP** Core

The UPP Core Converts between Axi4s Data Frames & 802.3 Ethernet Packets. Incoming UDP payloads are enclosed into 802.3 Ethernet Packets to be transmitted over an Ethernet Network by a PHY IP. Similarly UDP Payloads are extracted from received Packets which pass user set filtering requirements.

The core can be generated with the capabilities to reply to Ping & ARP Requests, and send ARP requests to maintain its own ARP table. It also can be generated to receive and transmit other Ethernet Type or IPV4 Protocol Packets, allowing the user to add other packet capabilities.

The Core is designed to be scalable, and can operate at speeds of 1GbE, 10GbE, 40GbE and 100GbE. It is also Vendor agnostic and has been tested on both IntelFPGA and Xilinx devices.

The operation of the core is controlled using a series of memory mapped control registers accessed via an Axi4lite interface, described in Core Settings. The full memory map of the core including absolute addresses can be seen at Memory Map.

The architecture of the Core is split up into two main functional blocks; the Tx Path and the Rx Path. Information on instantiating the UDP Core can be found in Instantiating the Core.

A Testbench and a script to drive it is also included in the project. It can be used as an example on how to instantiate the Core.

Control plane Axi4lite modules required by the Core need to be generated using XML2VHDL before use. The testbench script drives XML2VHDL to produce the necessary files. You will need to modify the testbench script to add the location off the main XML2VHDL script.

#### License

BSD 3-Clause License

Copyright(c) 2021 UNITED KINGDOM RESEARCH AND INNOVATION

Electronic System Design Group, Technology Department, Science and Technology Facilities Council

Redistribution and use in source and binary forms, with or without modification, are permitted provided that the following conditions are met:

- 1. Redistributions of source code must retain the above copyright notice, this list of conditions and the following disclaimer.

- 2. Redistributions in binary form must reproduce the above copyright notice, this list of conditions and the following disclaimer in the documentation and/or other materials provided with the distribution.

- 3. Neither the name of the copyright holder nor the names of its contributors may be used to endorse or promote products derived from this software without specific prior written permission.

- Hosted on STFC Gitlab

- Automatic documentation

- Sphinx/Read the Docs/doxygen

- Mem Map Tables from XML

- Helper Scripts

- VUNIT Simulation

- BSD 3-Clause License

- packaged

#### 100G UDP Core

Changelog

Docs » Memory Map Technology Electronic System Design Group **Memory Map Auto Generated Register Tables** The following tables have been automatically generated using the XML file used to create the Memory-Mapped Register locations. Descriptions have been extracted from the XML file used to generate the Memory-Mapped Register locations. Mapped Registers and their corresponding fields. All Register The Absolute Addresses are shown at this level of hierarchy. They may change if a connection to an upstream AXI4-Lite is made.

- Hosted on STFC Gitlab

- **Automatic documentation**

- Sphinx/Read the Docs/doxygen

- Mem Map Tables from XML

- **Helper Scripts**

- **VUNIT Simulation**

- **BSD 3-Clause License**

- packaged

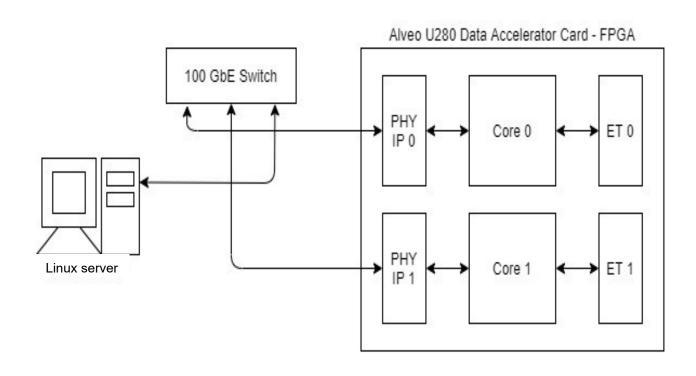

#### 100G UDP Core – H/W Test

- Alveo U280 & HTG RFSoC

- FPGA <-> FPGA via switch

- Ran Embedded Test overnight, no errors or dropped packets

- Script reads switch counters over time period to give a measured speed – 99.8 Gb/s

- JTAG AXI4L core & xtcl setup

- , ILA

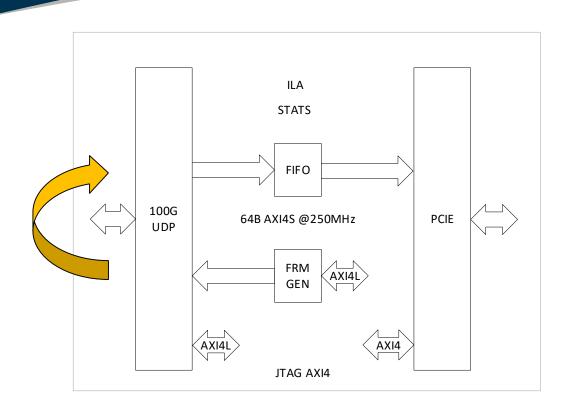

#### 100G UDP-PCIe Test Top Level

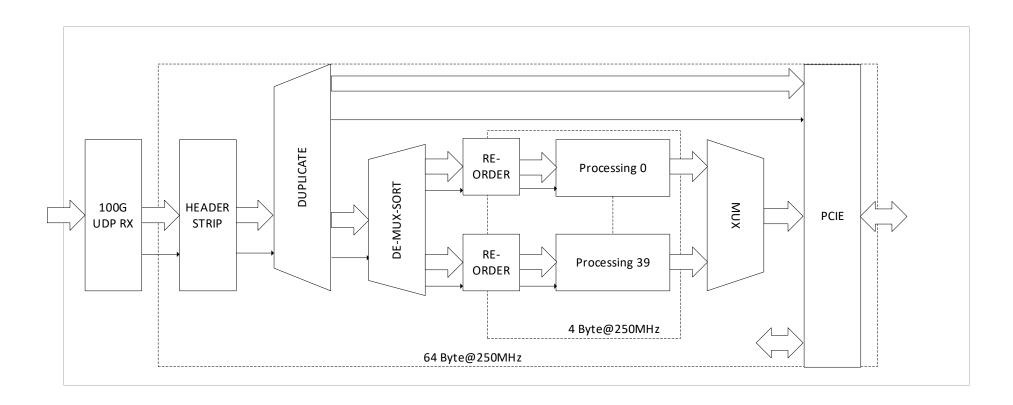

# **Full Processing FPGA Top Level**