# ArgonCube 2x2 at FNAL: Update on Module-0

Lane Kashur

2x2 Integration Meeting

10 February 2022

# Module-0: Previous Updates

Oct. 2021

- Module arrives at MSB

- Initial checkout begins

- Data loggers read out

- Field shell integrity test

- Slow controls temp. monitoring

- Basic LRS connectivity

Nov. 2021

- CRS pORC at MSB

- CRS connectivity tests

Dec. 2021

→ Module moved to LArTF

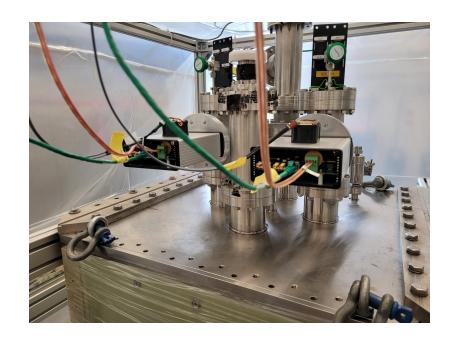

#### Module-0 at LArTF

Module unboxed in January (partial) Test stand prepared

- Benchtop power supplies for PACMAN(s), PACMAN fans, and Slow Controls

- Server rack / network switch for remote access

Test stand underwent successful pORC review

#### **Charge Readout Testing**

#### Connectivity:

- Tile Power Draw

- Establish Hydra Networks

#### Functionality:

- Trigger Rate

- Pedestal

- Channel Thresholding

- Self-Trigger

Testing is underway with remote guidance from LBL (Stephen Greenberg)

### Charge Readout Testing: Tile Power Draw

Enable power to LArPix tiles, verify voltage and current readback are in spec

(VDDA 1870mV, IDDA 100-150mA, VDDD 1670mV, IDDD 500-530mA)

| TPC | VDDA     | IDDA          | VDDD     | IDDD          |

|-----|----------|---------------|----------|---------------|

| 1   | <b>V</b> | Tile 2: 320mA | <b>V</b> | Tile 6: 680mA |

| 2   | <b>V</b> | <b>V</b>      | <b>V</b> | Tile 6: 690mA |

TPC 1, Tile 2 IDDA consistent with measurement at Bern. High IDDD on Tile 6 seen with all v1rev3 PACMANs.

Tile power draw in spec / consistent with previous measurements

# **Charge Readout Testing: Establish Hydra Networks**

Create Hydra networks and verify communication with ASICs

All ASICs incorporated into Hydra networks, communication verified

Also checked for increase in UARTs inaccessible for IO and failed root chip connections (compared to Bern/MSB)

- No drastic increase in inaccessible UARTs

- Some additional root chip failures will investigate further

# Charge Readout Testing: Trigger Rate

Set channel thresholds at half dynamic range, run chips in self-trigger mode with no periodic reset. Identify channels with:

- Trigger rate > 10kHz

- Trigger rate > 1kHz

Add to "Disable List"

Data taken, need to compare with Bern measurements

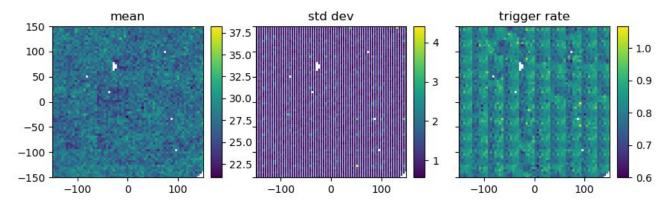

### **Charge Readout Testing: Pedestal**

Run chips using internal periodic trigger, identify channels with:

- Mean ADC > 50

- Std ADC > 10

Add to "Disable List"

Data taken, need to compare with Bern measurements

Example: TPC 1, Tile 1

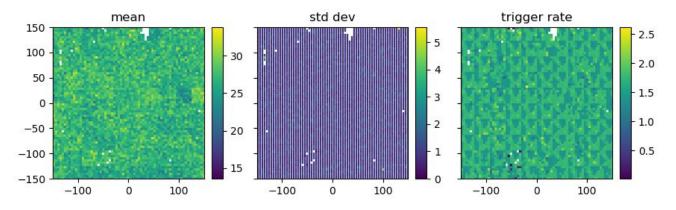

### **Charge Readout Testing: Pedestal**

Run chips using internal periodic trigger, identify channels with:

- Mean ADC > 50

- Std ADC > 10

Add to "Disable List"

Data taken, need to compare with Bern measurements

Example: TPC 2, Tile 8

# **Charge Readout Testing: Channel Thresholding / Self-Trigger**

Set channel thresholds, collect data continuously in self-trigger mode and verify:

- Trigger rate uniformity

- Trigger rate stability

#### **Module-0 Temperature Monitoring**

### **DAQ** and Computing

#### **Server Access**

acd-srv01 → see Geoff's slides

larpix-control: python library for CRS DAQ

InfluxDB: time series database

Grafana: visualization tool for live monitoring

#### Data

Data from CRS testing available on acd-srv01 at /data/LArPix/

More details <u>here</u>.