# DAPHNE at Italy initial tests.

21 February, 2022

# Daphne testing in Italy

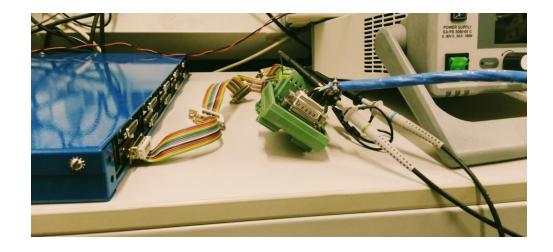

- DAPHNE arrived in Italy on February 3.

- DAPHNE: #8, #9, #10.

- Testing started 2 weeks ago.

# 1.General visual inspection:

## **DAPHNE #8**

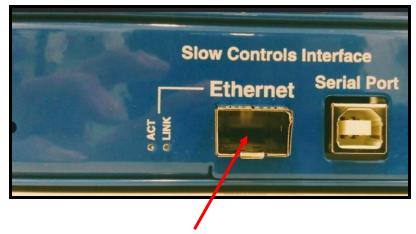

The SFP Slow Control input is bent, preventing the correct insertion of the SFP Module.

The JTAG Connector (Micro JTAG) is broken.

#### **2. DAPHNE #8 and #9** the following tests were performed:

- 1. Power consumption is around 19 watts at idle.

- 2. Serial communication with the microcontroller was established.

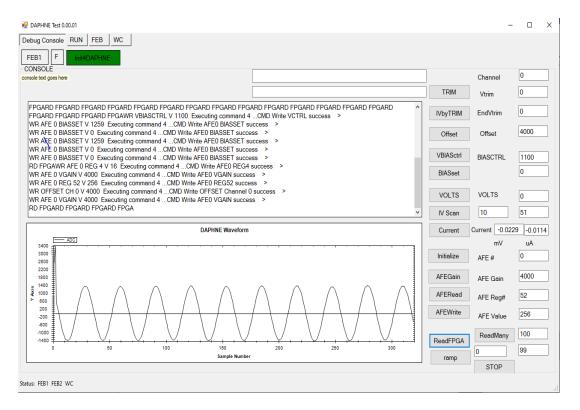

- 3. The microcontroller and FPGA was programmed.

- 4. The response of the microcontroller and the PFGA was verified.

- 5.FPGA clock verified:

- Alignment in the AFE of the 8 channels with the clock.

- Alignment with the frame clock.

- 6. Verified and calibrated Trim and Bias.

- 7. Verified 3.3V supply for the cold electronics

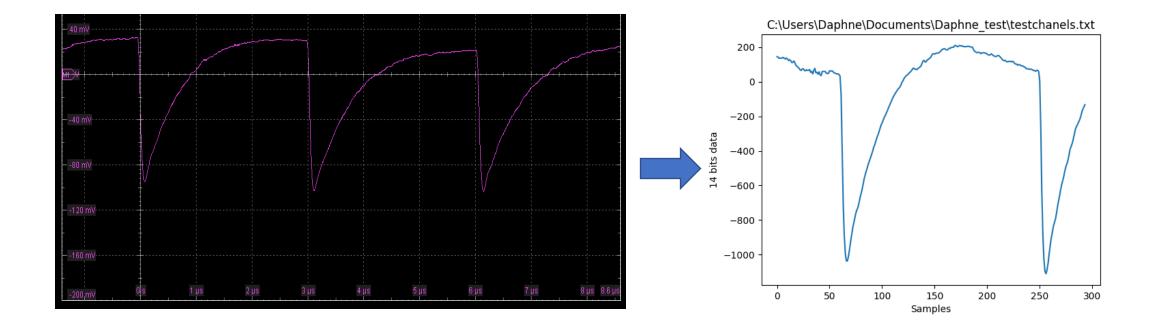

#### 3. Analogic test:

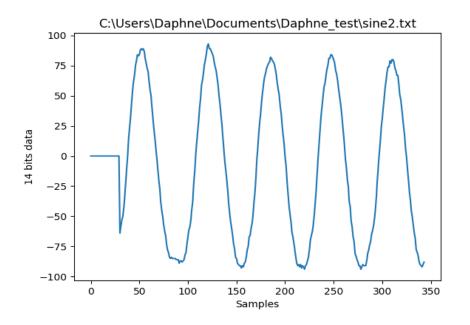

- 1. The AFE 0 channel 0 was fed with a sinusoidal analog signal of 200 mV with a frequency of 1MHz.

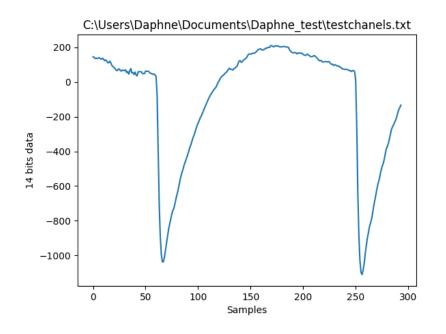

- 2. The FPGA data was read and graphed. (See Figure )

- Digitalized Channel 0

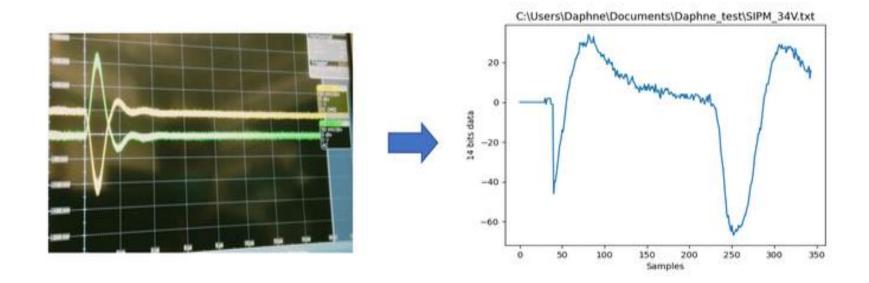

- LED pulse on 48 SiPMs (FBK) in liquid nitrogen, 31.6V (+4.5V overvoltage), readout with cold amplifier

- 150mV amplitude (300 mV differential) corresponds to roughly 750 photons (1 p.e. = 400 uV peak differential)

- could be due to crosstalk in the DAPHNE input transformer (CM pins not yet grounded), if we are reading out the neighbouring channel instead of the correct one

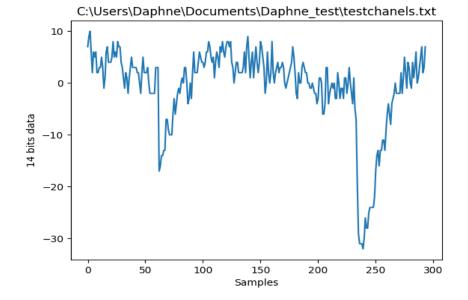

- We tried to remap the cold amplifier wires to channel  $\boldsymbol{0}$

When we set the offset to channel zero, we get a change in the amplitude of the pulse. (WR OFFSET CH 0 V1000, WR AFE 0 REG 52 V 256)

# **Next Steps**

- Undestand our signal: Test offset.

- Now the digitalization is fix in the channel zero (AFE 0), and this is in conflict with our cold amplifier setup, which is accesible through channel 4 or 5.

- We don't know if there is a command to aquire data per individual channel different that channel zero. (We believe that this feature is very important for upcoming test).

- Make the modification to the differential to single ended transformer at the input of the AFEs to supress the know crosstalk issue.

- Calibrate the gain and the offset per channel with the cold amplifier.

- Determine the signal to noise ratio.

- We'll need the external trigger.