# **DAPHNE Test at Milano-Bicocca**

E. Cristaldo , M. Delgado , C. Gotti , F. Terranova July 11<sup>th</sup> , 2022

### Introduction

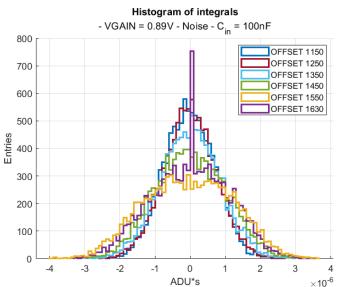

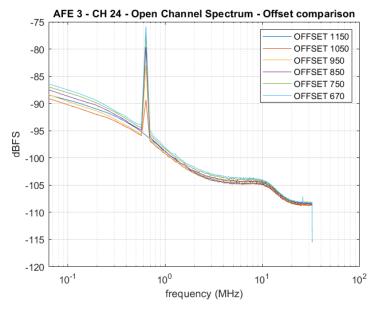

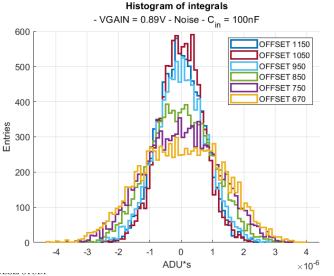

- Noise component at different OFFSETS.

- Digital filter tests.

### Noise at the AFE inputs

- As we proceeded with our test, we noticed an increase in the noise levels as we changed the OFFSET value.

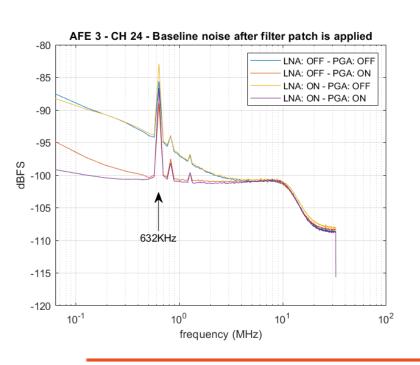

- The ~630KHz component increase as the offset is moved away from the center. The contribution of this component increase equally as the OFFSET is moved in both directions.

- Also, we noticed a slight deterioration with the 1/f contribution as we moved the OFFSET to lower values from the center.

- The value center is ~1150 for this configuration.

- VGAIN 0,89V OFFSET GAIN 2 LNAG 12dB – PGAG 24dB

#### Noise at the AFE inputs

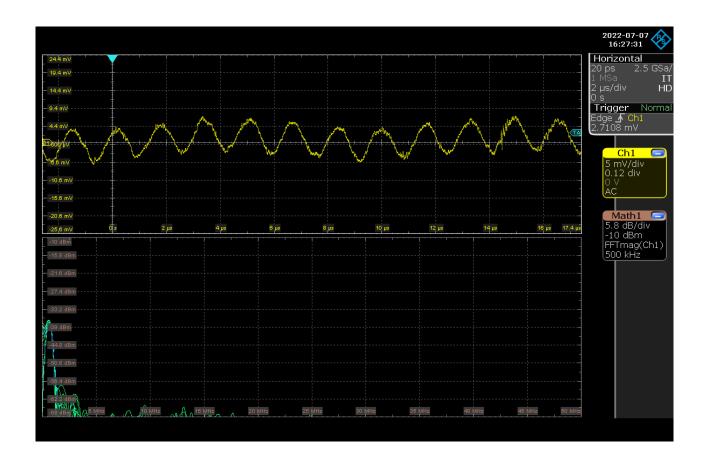

- The component visible in the AFE waveforms is present at the AFEs +5A.

- The ripple is within expected values but unfortunately the AFE PSRR is not enough to filter it out. (Apparently, when we center the pedestal the AFE is capable to filter it out)

- We also checked +3,3A and +1,8A and they are very clean. This can be explained by the presence of the 3,3V LDO and a choke transformer filtering +1,8A from +1,8D.

#### Noise at the AFE inputs

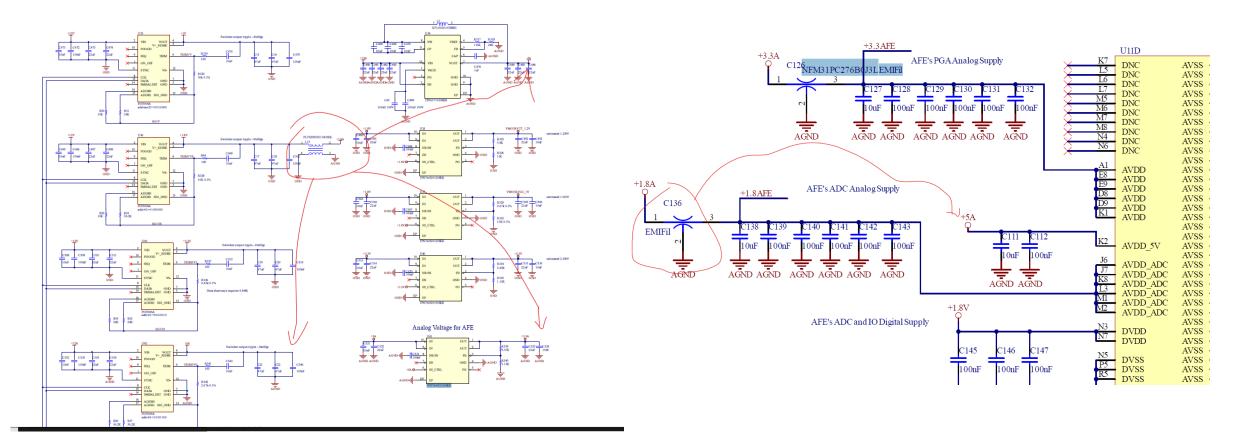

- After looking at the schematic and consideration, we requested additional changes to DAPHNE V2A to mitigate the noise issue.

- Replicating the +1.8A filter choke (L13 PLT5BPH5013R1SNL) on all analog voltage rails (i.e +5A +3.3A -5A) connecting pind 3 and 4 to AGND.

- Replicating EMIFil (C136 NFM31PC276B0J3L EMIFil) in the +5A AVDD\_5V.

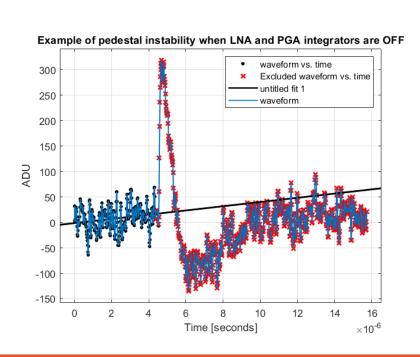

- We have noticed that with integrators OFF, we have a 1/f noise component that causes a pedestal instability due to the presence of low noise components.

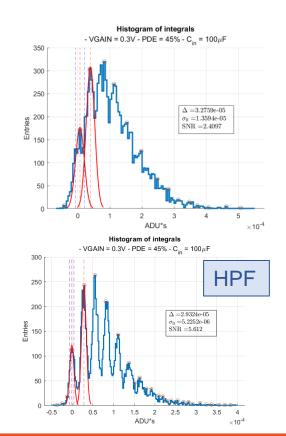

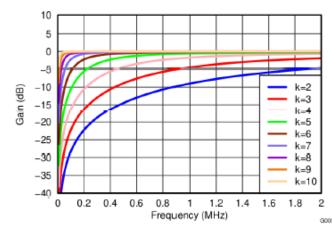

- Just by applying an 80KHz digital high pass filter is enough to improve drastically the histogram.

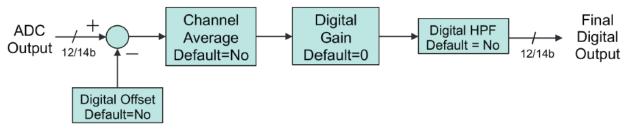

- The AFE5808 has a digital HPF functionality described in page 48.

- We tested the digital filter with positive results, but the main drawback is that at the end it centers the signal at the middle scale just as turning on the LNA and PGA integrators, which limits the dynamic range.

A solution is to implement this filter in the FPGA after the AFE Final Digital Output, adding the

capability to restores the pedestal.

Comment about the pedestal recovery: Removing the pedestal with a HPF is ideal for the data analysis and the triggering mechanism. Pedestal recovery is needed to correctly calibrate each channel to obtain the best dynamic range.

Figure 79. ADC Digital Block Diagram

Figure 58. Digital High-Pass Filter Response

$$y(n) = \frac{2^k}{2^k + 1} [x(n) - x(n-1) + y(n-1)]$$

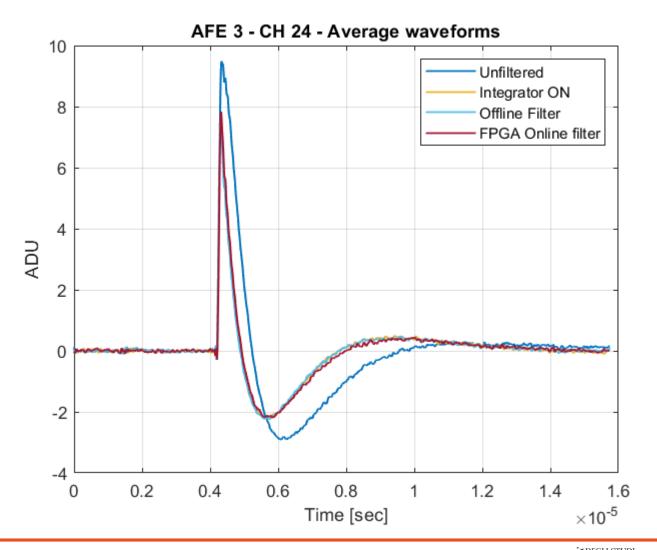

- We have implemented a very rudimentary proof of concept HPF with pedestal recovery for DAPHNE.

- We have inserted it in Jamieson's firmware, specifically working in a fork of commit e448dfc13fa5a73cb7bd0bad0c785dc7f6af6892, between the AFE frontend module and the SPY buffers.

- The LPF filter just calculates the average for a window of 2<sup>13</sup> samples.

- The HPF has a form  $y[n] = n_1x[n] + n_2x[n-1] + n_3x[n-2] + (-d_1)y[n-1] + (-d_2)y[n-2]$

- We have found that using  $n_1 = 0.9378$ ;  $n_2 = -1.8166$ ;  $n_3 = 0.8788$ ;  $d_1 = -1.8876$ ;  $d_2 = 0.8886$ , we can obtain the same response as if the integrators where on.

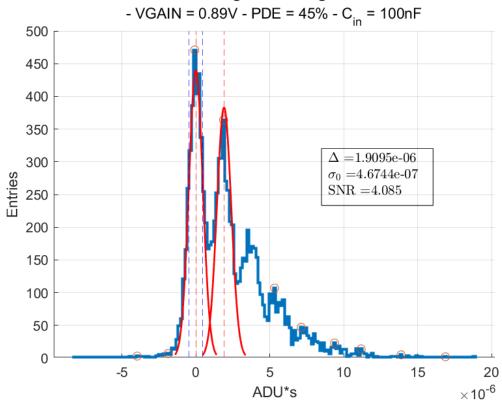

## **Integrators OFF**

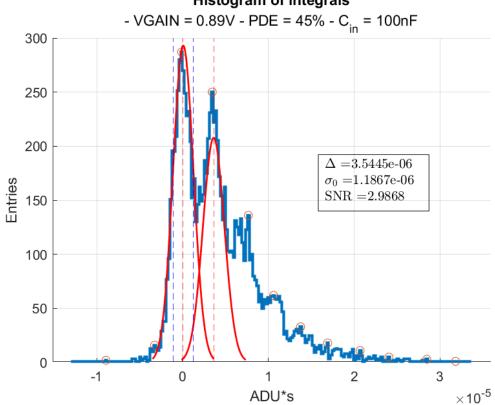

#### Histogram of integrals

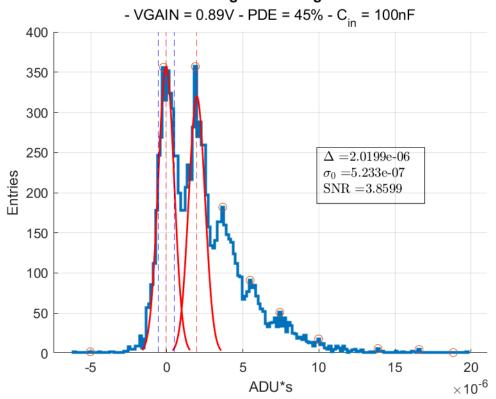

### **Integrators ON**

#### Histogram of integrals

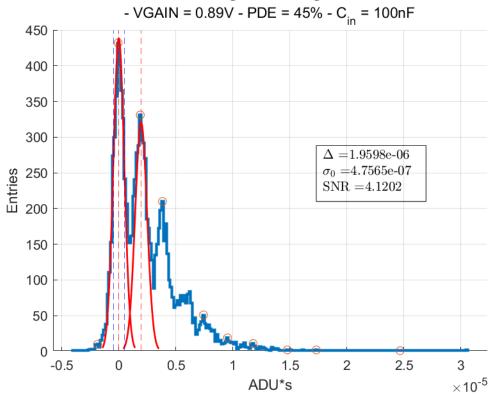

#### Pedestal Recovered

#### Histogram of integrals

#### **Pedestal Removed**

#### Histogram of integrals

#### Digital Filtering Slow control Pedestal monitor LPF y[15:0] DAQ adder X[15:0] Trigger **HPF** minus **AFE** processor y\_pedestal\_rem[15:0]

- Here we can have multiple strategies.

- It's recommended that we feed the Trigger processor with the "pedestal removed" signal. In that way, the block is independent of the pedestal value in addition to have the best SNR.

- For the DAQ:

- 1. We can select either to have "pedestal removed", "pedestal recovered", or "raw unfiltered" and perform the post-processing.

- 2. The pedestal can be monitored externally with the slow control, and/or added to each waveform as a number in the Data Frame when "pedestal removed" to DAQ is selected.