14 November 2022

C. Gotti INFN/Univ. Milano-Bicocca

On behalf of the DUNE FD1 PD Photosensors & Electronics WGs

Detailed description of the cold amplifier:

**Cryogenic front-end amplifier design for large SiPM arrays in the DUNE FD1-HD photon detection system**

C. Brizzolari *et al* 2022 *JINST* **17** P11017

https://doi.org/10.1088/1748-0221/17/11/P11017

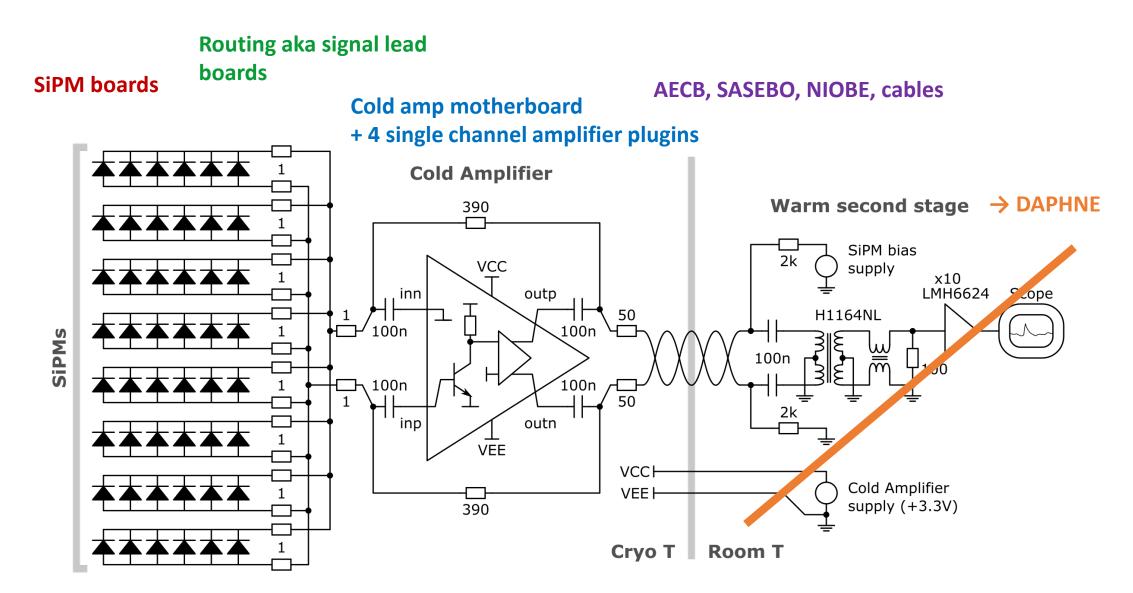

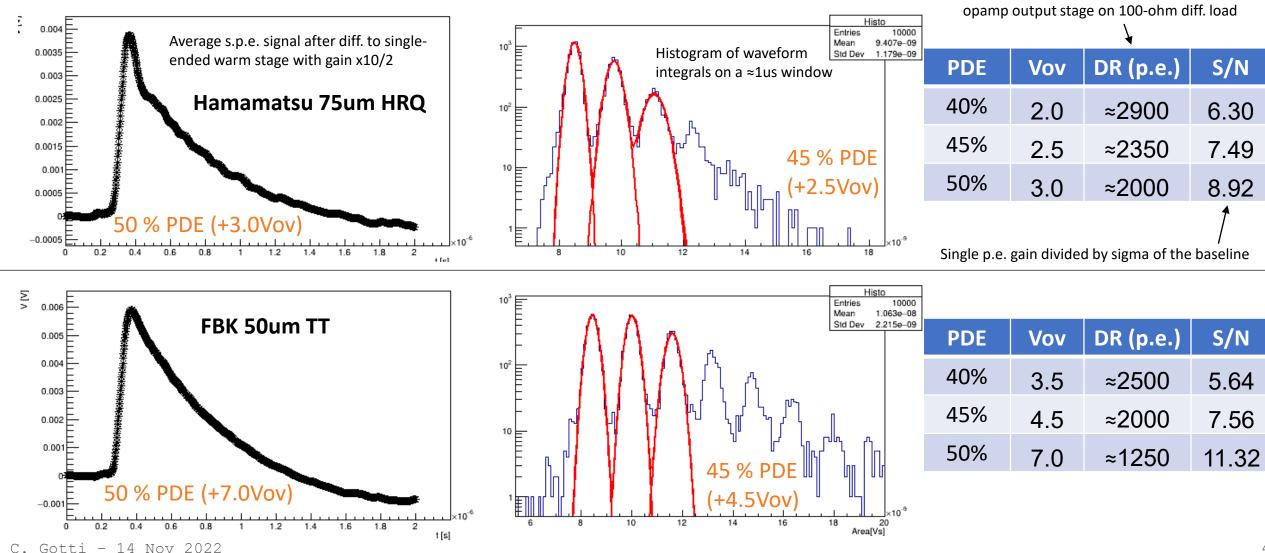

- FD1-HD configuration, 48 SiPMs in parallel ٠

- Test bench results, no supercells, no signal lead boards ٠

**Requirements:**

- ≈2000 p.e. dynamic range

- <100 ns signal rise time

- S/N>4

Dynamic range before saturation of the

## Lessons learned from ProtoDUNE2

- Testing of supercells in LN2 and LAr in several labs has been very useful also for the cold amplifiers

- Allowed us to arrive at CERN with a system that was already well validated

- Electrical Integration of all components was smooth

- SiPM boards and routing boards are transparent

- In particular, no issues observed from ≈1m long routing boards

- Same signal shape, similar S/N and general performance with entire supercells compared to compact setup with just SiPM boards and cold amplifier

- Somewhat higher sensitivity to external disturbances with entire supercells or modules compared to compact setup, but not surprising and anyway under control

- Signal transmission looks fine also with 30 m cables

- Matching of characteristic impedances does not look critical (≈70 ns signal rise time)

- System grounding under control

- Very good yield from PCB production

- 160/160 amplifiers produced for protoDUNE2 working out of the box

- No failures (so far...)

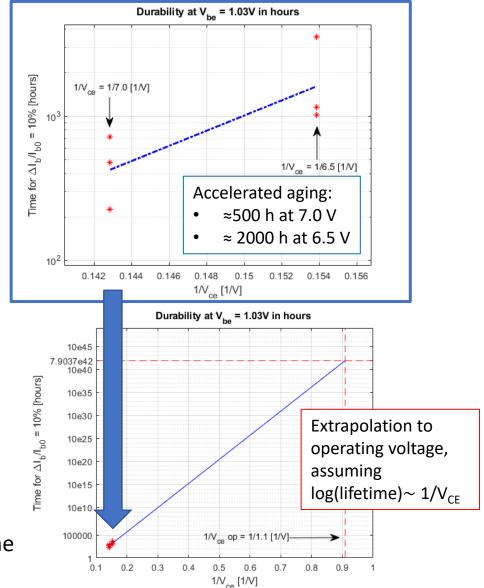

# Lifetime of components at cryo T

- At cryogenic temperature, increased carrier mobility can enhance degradation due to hot carrier effects (HCE)

- Aging accelerated by operation at high voltage (above max rating)

→ Li et al IEEE TNS doi:10.1109/TNS.2013.2287156

→ Cressler, Mantooth, Extreme Environment Electronics ISBN 9781138074224

#### **BFP640 SiGe transistor**

- Maximum datasheet values (room T): V<sub>CE</sub>=4.1 V, I<sub>C</sub>=50 mA

- Operated at  $V_{CE}$ =1.1 V,  $I_C$ =0.4 mA  $\rightarrow$  Ample margin

- Stressed up to V<sub>CE</sub>=7.0 V

- Degradation criterion: 10% increase in base current (decrease in beta)

- Lifetime at the operating point extrapolated to very high values

#### THS4531 fully differential opamp

- Maximum datasheet values (room T): V<sub>s</sub> = 5.5 V

- Operated at  $V_s = 3.3 V \rightarrow Ample margin$

- Stressed for HCE up to V<sub>s</sub>=8.0 V

- Preliminary results at INFN LNS (P. Litrico et al) indicate very long lifetime

### Open issues

- Complete lifetime and reliability measurements before the final design review

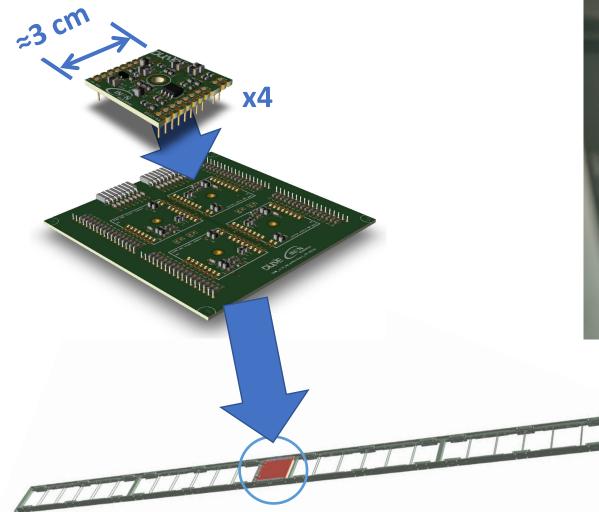

- For DUNE: from motherboard + 4 single-channel plug-ins to a single board with 4 channels?

- Lower production cost

- Higher mechanical reliability (less connectors)

- Lower flexibility, i.e. impossible to replace a single amplifier without dismounting the module

→ not a problem?

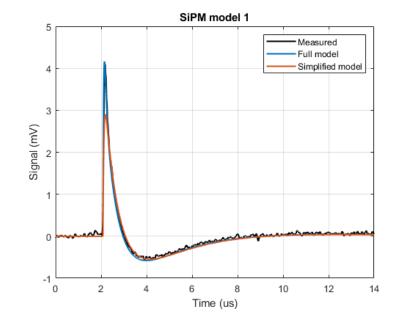

- Is undershoot an issue?

- Study the possibility of removing it by deconvolution  $\rightarrow$  no hardware changes necessary

- If necessary, might consider modifying the DAPHNE input stage (LAN transformer)

- If the above are not enough, increase value of AC coupling capacitors at cold

- Possibly need to use X7R ceramics instead of just COG

- Synergy with vertical drift developments