areaDetector Challenges and Perspectives for Sirius High-Throughput Detectors

Marco Montevechi Filho

EPICS Collaboration Meeting April 2023

# What we have/What we want

- In-house detector development currently deployed at 5 beamlines

- Control software architecture integrated with EPICS

- Detector data acquisition architecture partially/completely integrated with EPICS

|                                 |                           |              |       | Timepix3 (2013)                                 | Timepix4 (2019)                              |

|---------------------------------|---------------------------|--------------|-------|-------------------------------------------------|----------------------------------------------|

| Technology                      |                           |              |       | 130nm – 8 metal                                 | 65nm – 10 metal                              |

| Pixel Size                      |                           |              |       | 55 x 55 μm                                      | 55 x 55 μm                                   |

| Pixel arrangement               |                           |              |       | 3-side buttable<br>256 x 256                    | 4-side buttable<br>512 x 448                 |

| Sensitive area                  |                           |              |       | 1.98 cm <sup>2</sup>                            | 6.94 cm <sup>2</sup>                         |

|                                 | Data driven<br>(Tracking) | Mode         |       | TOT and TOA                                     |                                              |

| les                             |                           | Event Packet |       | 48-bit                                          | 64-bit                                       |

| Noc                             |                           | Max rate     |       | 0.43x10 <sup>6</sup> hits/mm <sup>2</sup> /s    | 3.58x10 <sup>6</sup> hits/mm <sup>2</sup> /s |

| Ħ                               |                           | Max Pix rate |       | 1.3 KHz/pixel                                   | 10.8 KHz/pixel                               |

| Readout Modes                   | Frame based<br>(Imaging)  | Mode         |       | PC (10-bit) and iTOT (14-bit)                   | CRW: PC (8 or 16-bit)                        |

| Rei                             |                           | Frame        |       | Zero-suppressed (with pixel addr)               | Full Frame (without pixel addr)              |

|                                 |                           | Max count    | trate | ~0.82 x 10 <sup>9</sup> hits/mm <sup>2</sup> /s | ~5 x 10 <sup>9</sup> hits/mm <sup>2</sup> /s |

| TOT energy resolution           |                           |              |       | < 2KeV                                          | < 1Kev                                       |

| TOA binning resolution          |                           |              |       | 1.56ns                                          | 195ps                                        |

| TOA dynamic range               |                           |              |       | 409.6 μs (14-bits @ 40MHz)                      | 1.6384 ms (16-bits @ 40MHz)                  |

| Readout bandwidth               |                           |              |       | ≤5.12Gb (8x SLVS@640 Mbps)                      | ≤163.84 Gbps (16x @10.24 Gbps)               |

| Target global minimum threshold |                           |              | old   | <500 e <sup>-</sup> Detector                    | <500 e <sup>-</sup>                          |

- Current implementations deal with 210 Gbps

- Future detectors can require up to ~1.8 Tbps

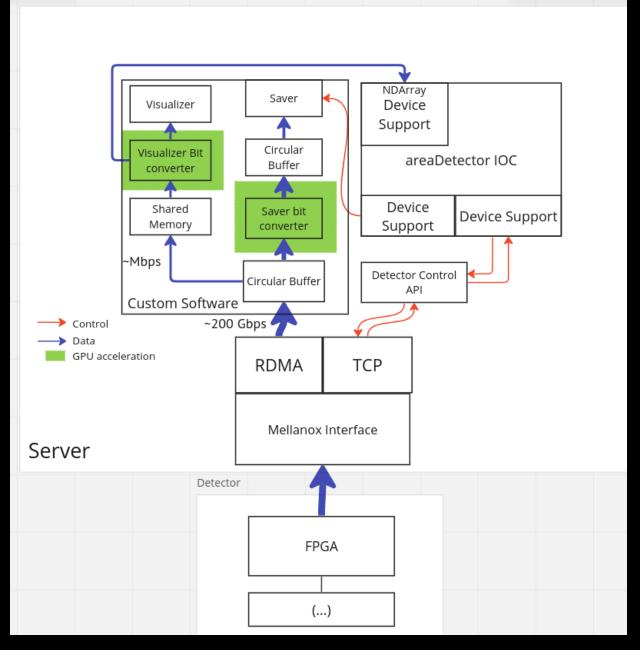

### What we have

- Software architecture decoupled from areaDetector

- Data pipeline is defined at compile time

- No customizable metadata

- Implementation not modularized (monolithic)

- Can choose between with/without hardware acceleration (GPUs)

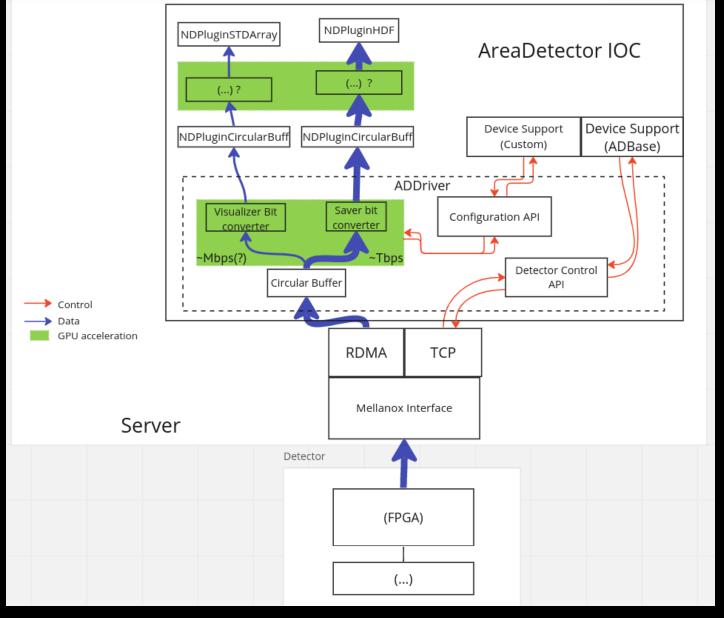

## What we want

- Use areaDetector resources as much as possible

- Reconfigurable data pipeline

- Customizable metadata, ROIs, etc.

- Modularized implementation

- Integrated hardware acceleration

## Final questions:

- 1. Does the proposed architecture make proper use of areaDetector or are we abusing it? Is it meant for high-throughput?

- 2. Hardware acceleration options: should we develop new plugins/drivers or extend existing ones?

- 3. Are there plugins/drivers that already use hardware acceleration?

- 4. Are there ongoing efforts to develop such hardware acceleration capabilities? If yes, how could we team up on this?

### Thanks!

- Marco Montevechi Filho (Control Software Developer): marco.filho@lnls.br

- Érico Rolim (Control Software Developer): <a href="mailto:erico.rolim@lnls.br">erico.rolim@lnls.br</a>

- Eduardo Pereira Coelho (Control Software Group Leader): <a href="mailto:eduardo.coelho@lnls.br">eduardo.coelho@lnls.br</a>

- Jean Marie Polli (Detectors Group Leader): <a href="mailto:jean.polli@lnls.br">jean.polli@lnls.br</a>

- Daniel Tavares (Head of the Data Acquisition and Processing Division): <a href="mailto:daniel.tavares@lnls.br">daniel.tavares@lnls.br</a>