#### Self-trigger algorithm

Detection algorithm 64R-32R-16R, VHDL implementation and future work

Edgar Rincón-Gil

Universidad EIA-Colombia

March 13, 2023

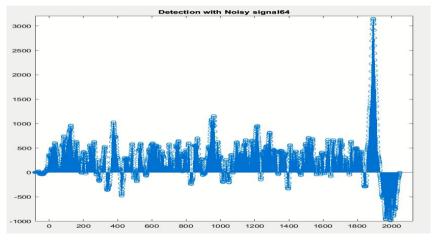

## Simulation: Using a 64 register multiplication for the matching filter

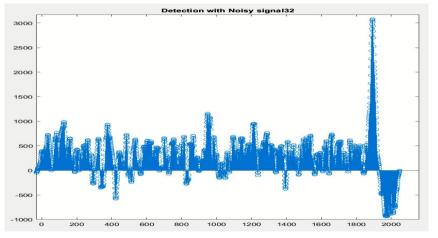

## Simulation: Using a 32 register multiplication for the matching filter

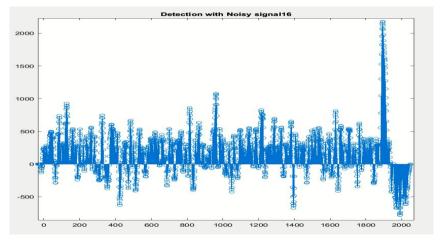

## Simulation: Using a 16 register multiplication for the matching filter

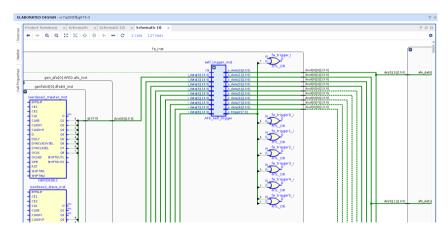

## RTL schematic of the self-trigger integrated inside DAPHNE V2a firmware

#### Integration of a self-trigger algorithm for 40 channels

```

28 1. Slice Logic

30

Site Type

Used | Fixed | Available | Util% |

34 | Slice LUTs

8718

133800 I

6.52

35 I

LUT as Logic

4.57

6109

133800

LUT as Memory

2609

46200

5.65

LUT as Distributed RAM

37 I

0

LUT as Shift Register

2609

Slice Registers

15749

5.89

267600

40 I

Register as Flip Flop

15749

267600 I

5.89

0

Register as Latch

41 I

0

267600 I

0.00

F7 Muxes

258

0

66900

0.39

F8 Muxes

45

0.13

0

33450

45

```

# Integration of a self-trigger algorithm using a 16 register multiplication

```

Used | Fixed | Available | Util%

Site Type

100 +-----------

Block RAM Tile

I 130.5 I

102 i

RAMB36/FIFO*

13 I

365

3.56

103 I

FIF036E1 only |

12 i

RAMB36E1 only |

104 I

1 1

105 1

RAMB18

235 I

0

730

32.19

FIFO18E1 only |

31 I

106 I

RAMB18E1 only |

107 I

204

109 * Note: Each Block RAM Tile only has one FIFO logic availabl

accommodate a RAMB18E1

110

111

112 4. DSP

113 -----

114

Site Type

118 I DSPs

600 I

119 I

DSP48E1 only L

600 I

120 +---

```

121

#### Code available on:

https://github.com/edgar-rincon-g/DAPHNE\_V2a.git branch: main

#### **Conclusions**

- ► A self-triggger algorithm using a 16 register multiplication is as reliable, as the the algorithm that uses a 64 register multiplication for the matching filter.

- ► The 16 register algorithm for detection, consumes less resources from the FPGA, making possible a 40 channels implementation using 600 DSPs(multipliers).

- ► A self trigger algorithm for 40 channels was successfully integrated into Fermilab's/Jamieson's code.

- ▶ DAPHNE V2a firmware is ready to be tested using a 40 channels self-trigger algorithm, based on matching filters.

#### What is next

- Do more tests on the self-trigger algorithm, and use more data coming from CERN or Milano.

- ► Another approach is being coded, but not yet finished. It uses combinational logic to implement the multipliers in order to optimize the use of DSPs.

- Continue to study and improve the algorithm. Because its highly dependant on the signal mean computing, during a 320 samples window.