# **FE ASIC for PDS Amplification**

Shanshan Gao on behalf of BNL CE Team

06/27/2023

### **Dual Calorimetry: Improving Light Collection and Charge Resolution**

#### Optimized Vertical Drift FD3-4: Light R/O technology optimization

Most (if not all) large mass, UG detectors for LowEn (solar) neutrino are Light r/o (scintillator or Cherenkov) based detectors [featuring  $4\pi$  coverage for a high & uniform LY - the base for a high detection efficiency and good energy resolution for LowEn events]

#### **LAr-PDS optimization options**

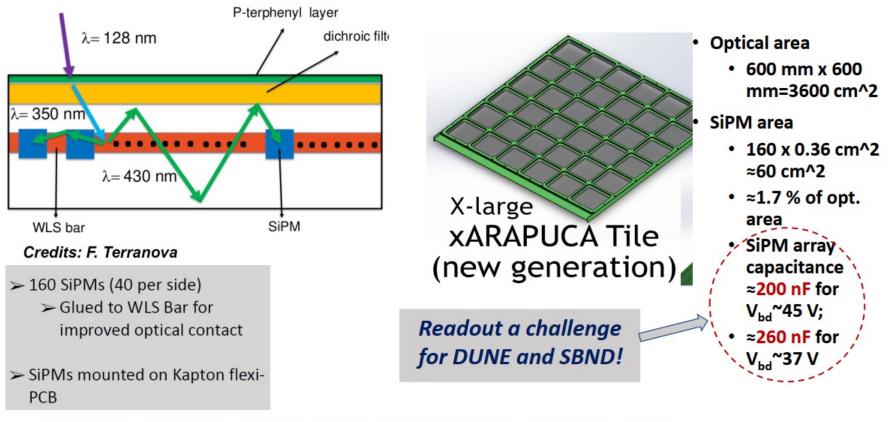

- ARAPUCA(w/ SiPM) technology is still young, with large margins of improvement thanks to well proven flexibility

- ARAPUCA bar w/ few (12)SiPM/channel + Warm Elec [Anode plane coverage] protoDUNE-SP-2018

- X-ARAPUCA bar w/ more (48)SiPM/channel + Cold & Warm Elec [Anode plane] ⇒ DUNE FD1- 2022

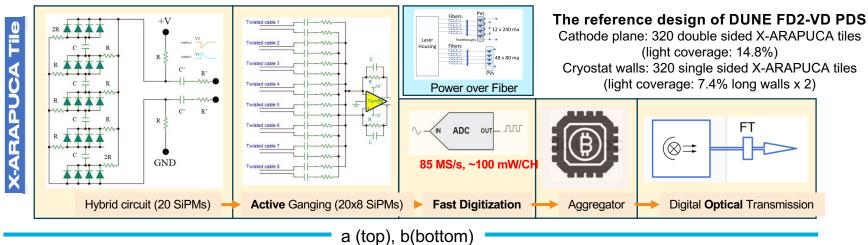

- X-ARAPUCA large tile w/ many (80)SiPM/channel + PoF-CE-SoF & Warm ADC [HV <u>Cathode plane</u> & Membrane Walls] ⇒ DUNE FD2 - 2023

- Next "natural" optimization step:

- X-ARAPUCA + PoF & CE(FE+ADC) & SoF + design flexibility for massive increase of coverage on FieldCage

#### ⇒ convert TPC Field Cage structure into a fully active PDS

• extended optical coverage for High and Uniform (Scintillation) LY

#### OR

- Change technology of Light signal read-out

- ·Integrated light pixels in Anode plane (Solar/Q-pix)

- ·Combine light pixels in Anode plane with X-ARAPUCA tiles on the Cathode plane

## Vejlko's talk on Lidine 2021

### DUNE FD-2: ARAPUCA (Argon R&D Advanced Program at UniCAmp).

M.C. Queiroga Bazetto, V.L. Pimentel, A.A. Machado and E. Segreto, in Campinas, Brazil

Veljko. Radeka, Lidine 2021, Sept 14

### "Giant" SiPM Capacitance

| Technology                       |      | "НРК" | "FBK" |

|----------------------------------|------|-------|-------|

| <b>C/A</b> [nF/cm <sup>2</sup> ] |      | 3.5   | 8.5   |

| Vop                              | [V]  | 60    | 30    |

| C <sub>6cm</sub> <sup>2</sup>    | [nF] | 21    | 51    |

| C25                              | [nF] | 5     | 12.5  |

| V <sub>25</sub>                  | [V]  | 120   | 60    |

6cm<sup>2</sup> SiPM subarray

$\tau_f$

Assumptions (approx.): -

- Number of readout channels ~8000x6cm<sup>2</sup> ~4.8 m<sup>2</sup>

- Readout power dissipation < 80 W

Why "Giant"?

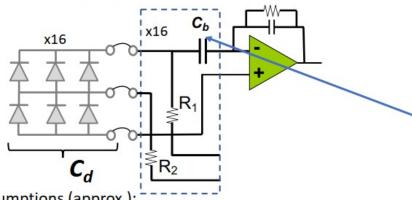

SiPM capacitance  $C_d$  (in any practical arrangement) is much higher than in any known detector

- C<sub>d</sub> is large, but so is the charge/pe, Qs ~ 0.4 pC (2.4 x 10<sup>6</sup> e<sup>-</sup>)

- The charge is bound to that giant capacitance, can we "see" it??

- How to "extract" the charge while applying the bias to SiPMs?

- Does C<sub>b</sub>, the decoupling (radiopure) HV capacitor have also to be "giant"?

Study based on the nEXO PRE development

3

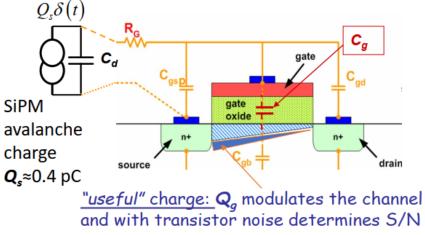

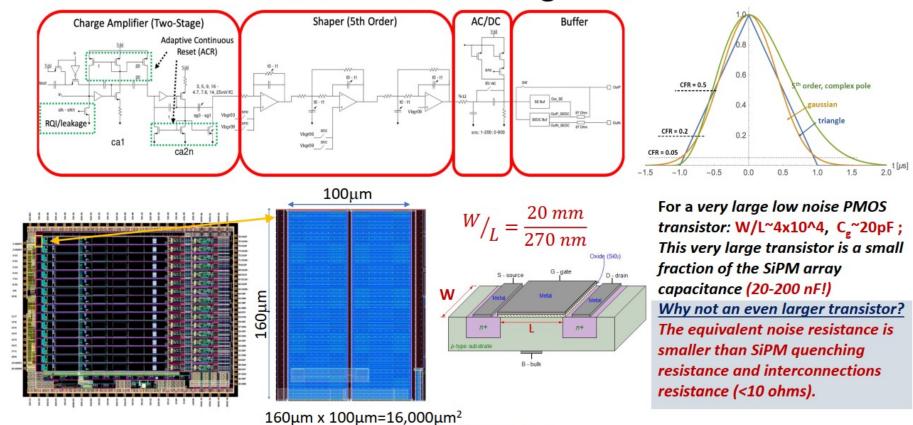

#### How much of the avalanche charge can we really "see"? SiPM – transistor capacitance mismatch

R<sub>G</sub>

Example: **Transistor gate:** C<sub>a</sub> =25pF (very large transistor)

| <b>-</b> 9                 | <u>nEXO</u>    | <u>xARAPUCA</u> |

|----------------------------|----------------|-----------------|

| SiPM array: C <sub>d</sub> | ≥20 nF         | >200 nF         |

| $(Q_g/Q_s)=(Cg/Cd)$        | <i>≤</i> 1/800 | <i>≤1/8000</i>  |

We "see" ~ 1 part in 10<sup>3</sup> or 10<sup>4</sup> of the SiPM avalanche charge  $Q_s$

A long way from the optimal sharing of charge:

$(Q_g/Q_s)_{max} = 1/2$ for (Cg/Cd)=1

Veljko. Radeka, Lidine 2021, Sept 14

$\frac{Q_g}{Q_s} = \frac{C_g}{C_g + C_d}$

$Q_{s}\delta(t)$

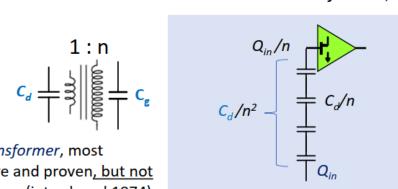

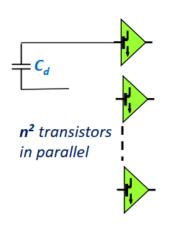

#### SiPM-to-transistor capacitance matching: SNR vs transformation ratio n

*n*= transformation ratio for *EM and ES transformers*; for *transistors in parallel*:  $n = n_{trans}^{1/2}$

EM transformer, most effective and proven, but not radio pure (introduced 1974)

For C<sub>d</sub>=20 nF, C<sub>g</sub>=25 pF  $\rightarrow$  $n_{opt} = \{C_d/C_g\}^{1/2} \approx 28, S/N \text{ is}$ increased by  $n_{opt}/2=14$

ES (Electrostatic) transformer (introduced 1990)

ES transformer n=4 improves S/N by a factor of ~ 3.95; compared to parallel connection of SiPMs.

For n=4, it would take *n*<sup>2</sup>=16, times as large a transistor area and power for the same result as with EM or ES transformer.

Veliko. Radeka, Lidine 2021, Sept 14

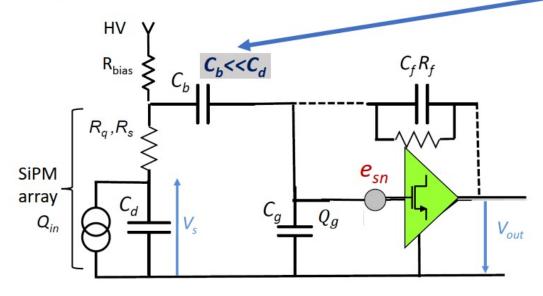

#### Optimal readout for SiPM arrays: <u>Weak coupling to amplifier</u>

$Q_{in}$  = avalanche charge  $C_d$  = capacitance of SiPM array in parallel; n = ES transformation ratio

**Basic limitation:** Only *adiabatically* transferred fraction of avalanche charge to transistor gate,  $Q_g \approx \frac{c_g}{c_d} Q_{in}$  contributes to S/N.

<u>Conventional approach</u>: Strong coupling -active (forced) transfer of charge is accompanied by corresponding increase in noise with no benefit to S/N. It requires  $C_b >> C_d$ , resulting in (de)coupling capacitors in tens of nanofarads.

$\label{eq:shows: C_b} \begin{array}{l} must be larger than \\ \textbf{C}_g, \ but \ can \ be \ \textbf{much smaller} \ than \ \textbf{C}_d: \\ \textbf{C}_d \!\!>\!\!>\!\!\textbf{C}_g \\ \textbf{e.g., 20 nF} \!\!>\!\! \underline{\textbf{O}_5 nF} \!\!>\!\! 25 \, \textbf{pF} \end{array}$

Veljko. Radeka, Lidine 2021, Sept 14

18

#### Solution: C<sub>b</sub> has to be larger than C<sub>g</sub> but can be much smaller than C<sub>d</sub>

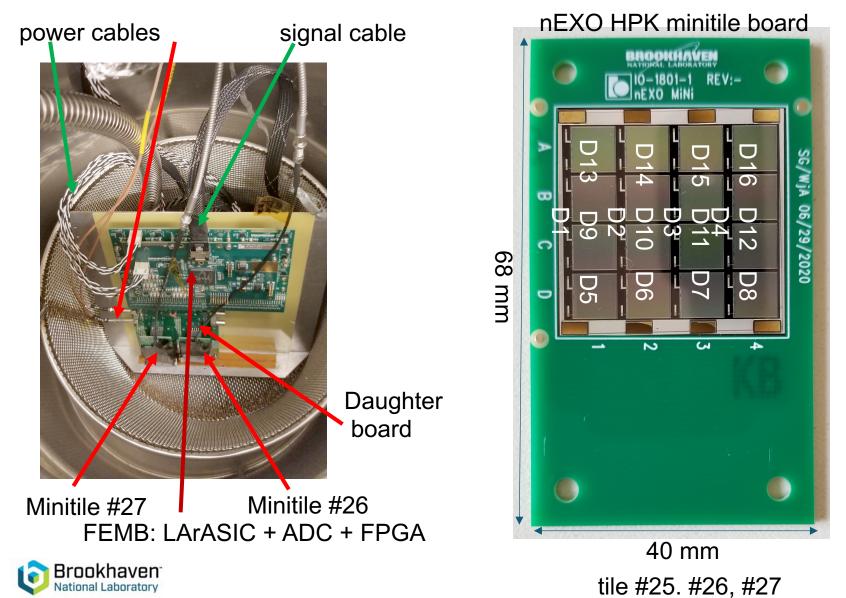

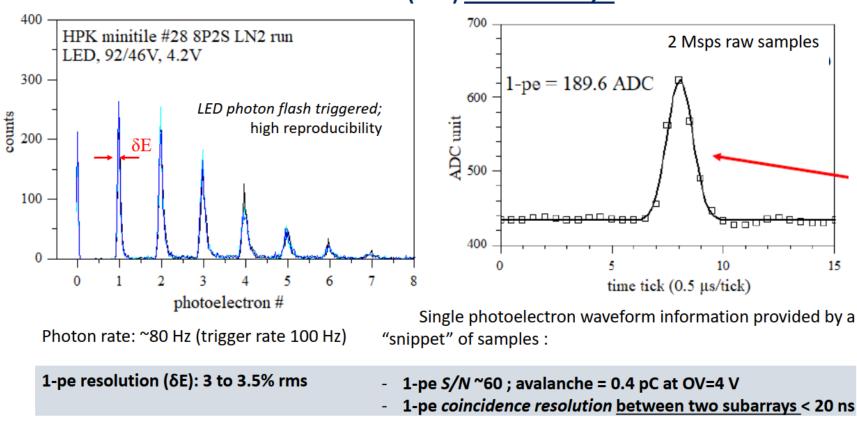

BNL: Demonstration of 6 cm^2 SiPM(HPK) 20 nF subarrays with LArASIC in LN2

Veljko. Radeka, Lidine 2021, Sept 14

20

#### **Excellent** S/N obtained from the demonstration at BNL

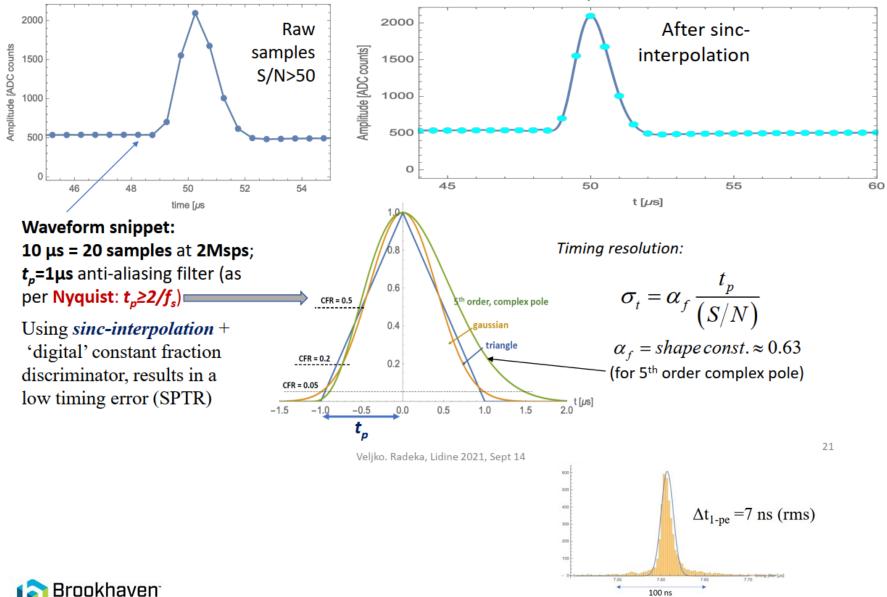

### Waveform reconstruction and 1-pe timing resolution (SPTR)

National Laboratory

### LArASIC = Antialiasing Filter

Veljko. Radeka, Lidine 2021, Sept 14

### **New FE ASIC to address physics requirements**

#### Some solid physics input on the light vs. time and the information to be extracted

Physics Modeling and Simulation is ongoing at BNL

#### Veljko's comments

- A problem arises how to read several ARAPUCAs. Can we benefit from a multi-channel ASIC? 16 ARAPUCAs are spread over a large area. Given the very large capacitance of SiPMs, we could afford low impedance connections with high capacitance and low inductance. This may be ok for a "slow" readout with peaking time ~ 1 µs, but propagation time must be considered if a much faster readout is needed. This brings us to the next question:

- How fast a readout is really needed in this case? As we know for event timing resolution even better than 100 ns, peaking time of ~ 1 µs is fine. If the physics (once it is understood) requires much faster waveform recording, then the anti-aliasing filter has to be made correspondingly faster, with serious consequences all along the chain (ADC, data serializer, transmission)

- Two points above may require a new FE ASIC design. We may be able to keep the data system as is charge readout, if we use pulse shape discrimination between the fast and slow light components. This will still need a new FE ASIC to provide both the fast and slow signal. However, it will avoid the need to increase the sampling frequency

- The new FE ASIC design may need to take into account

- Fast peaking time (~50 ns) followed by a peak detector

- Dual gain configuration to cover large (> 2 k pe) signal dynamic range

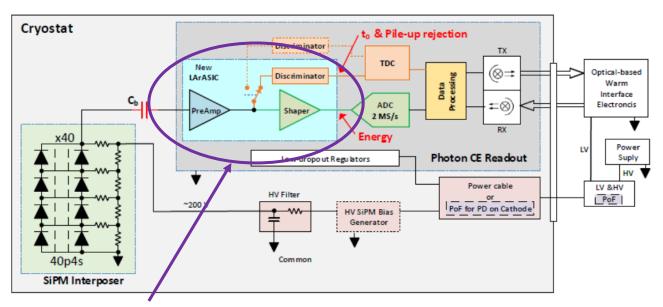

The ultimate FD2-VD PDS readout scheme

(ongoing R&D carried by DUNE SP PDS group)

Propose new FE ASIC design

### **R&D of Advanced Analog FE for Noble Liquid Detectors**

- Deep knowledge in low noise electronics systems for noble liquid detectors

- Expertise in low noise microelectronics for applications in extreme environments

- Successful development of AFE ASICs in large HEP experiments recently

- Expertise in signal processing and detector performance studies

- Explore both charge and light readout in noble liquid detectors

- Integral system design approach to optimize detector design

- Invention of LAr calorimeter at BNL ~half century ago

- Cryogenic temperature and high radiation

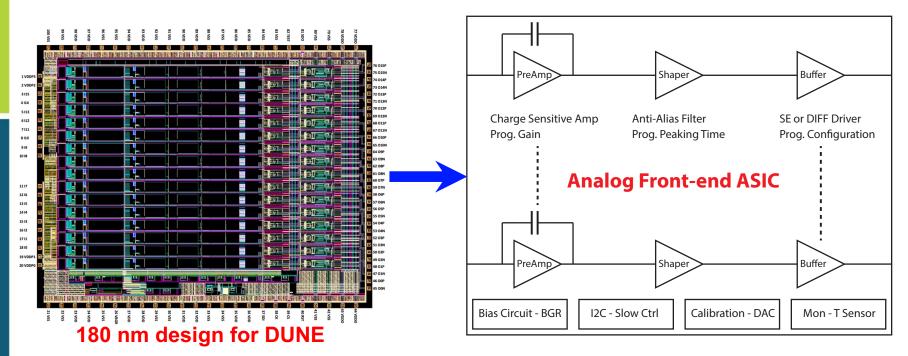

- LArASIC for DUNE FD1-HD/FD2-VD LArTPC, AFE for ATLAS LAr calorimeter HL-LHC upgrade

- Wire-cell in LArTPC reconstruction

- DUNE, nEXO, PIONEER, FLArE, FCC-ee etc.

- Electrode, analog signal processing, readout electronics system and integration systematically

## **Study on New Front-End ASIC**

- CSA design based on LArASIC suitable for charge and light detection

- Explore advanced CMOS node 65 nm suitable for both cryogenic temperature and high radiation environments

- Long cryogenic lifetime and radiation tolerance

- Wide signal dynamic range with excellent linearity

- Versatile configurations to optimize signal processing

- Flexible control and monitoring interface with precision calibration

- Programmable output stage to ease digitization interface

- Demonstrated performance of in charge readout of ProtoDUNE and light readout of nEXO

- Cryogenic model by DUNE and radiation model by RD53

- Follow well established design rules

- Thick oxide for higher supply voltage with more gain options

- Short peaking time options for better time resolution and pile-up rejection

- Standard I2C with built-in charge calibration

- Buffer is readily available for integration with custom or COTS ADC for downstream signal processing

- Studies for trade-off of technical parameters (SNR, power, shaping etc.) to reach optimal balance of performance parameters (energy resolution, time resolution, spatial resolution etc.)

### **Advanced AFE for Noble Liquid Detectors**

- Analog front-end ASIC with multiple (16+) channels and programmability

- Integrated auxiliary circuits for direct application in detector systems

- High performance analog front-end block for easy expansion to targeted design of future experiments, e.g. FCC-ee

- Key features and challenges

- 65 nm CMOS with thick oxide → Max Vdd (1.8 V, 2.5 V) to support extended dynamic range

- *Fast* peaking time (in the order of 10 ns) → support signal processing with stringent *time resolution*

- Low power consumption → support detector electrodes with fine segmentations

- Cryogenic operation with long lifetime → achieve optimum SNR

- Long term goals: fast front-end architecture (~GHz bandwidth), high radiation tolerance → FCC-hh

## **New LArASIC Requirements (1)**

|                                      |                                         | New ASIC opportunities                                                        |                   |                               |

|--------------------------------------|-----------------------------------------|-------------------------------------------------------------------------------|-------------------|-------------------------------|

|                                      |                                         | DUNE FD3/4                                                                    |                   |                               |

|                                      | DUNE FD1/FD2(bottom)<br>Charge Readout  | DUNE FD2/3/4 Light<br>Readout                                                 | Charge<br>Readout | PIONEER                       |

| ASIC                                 | P5B LArASIC                             | new                                                                           | new               | new                           |

| CMOS process                         | 180nm (discontinued)                    | 65nm                                                                          | 65nm              | 65nm                          |

| Supply Voltage                       | 1.8V                                    |                                                                               |                   |                               |

|                                      |                                         | low noise LDO is                                                              | low noise LDO     | low noise LDO is              |

| Integrated Regulators                | No                                      | preferred                                                                     | is preferred      | preferred                     |

| Input channels                       | 16                                      |                                                                               |                   |                               |

| Power consumption per<br>channel /mW | ~6mW/ch with SE mode                    |                                                                               |                   |                               |

| Gain                                 | 4.7, 7.8, 14.0, 25 mV/fC<br>(4 options) |                                                                               |                   |                               |

| Input leakage current                | 100pA/500pA/1nA/5nA                     |                                                                               |                   |                               |

| Peak time                            | 0.5, 1.0, 2.0, 3.0 us                   | ~100ns                                                                        | ~ 1 us, 2us       | 20ns                          |

| Detector Capacitor                   | 150~200 pF                              | weak-coupling                                                                 | 150-200 pF        | 20pF                          |

| Input Impediance                     | 50 Ohm?                                 | 200 Ohm?                                                                      |                   | as low as<br>possible         |

|                                      |                                         | as large as possible,<br>resolution: 1pe? split<br>signal and record both low |                   | um to 40, 50 fC               |

| dynamic range                        | 100 fC @ 14mV/fC                        | and high gains?                                                               |                   | up to $40 \sim 50 \text{ fC}$ |

| non-linearity                        | <1% (0.1%)                              | ?                                                                             |                   | < 1% (?)                      |

| Baseline options                     | 200mV/900mV                             |                                                                               |                   |                               |

### **New LArASIC Requirements (2)**

|                       |                         | New ASIC opportunities        |                |                    |

|-----------------------|-------------------------|-------------------------------|----------------|--------------------|

|                       | DUNE                    |                               |                |                    |

|                       | FD1/FD2(bottom)         | DUNE FD2/3/4 Light            | DUNE FD3/4     |                    |

|                       | Charge Readout          | Readout                       | Charge Readout | PIONEER            |

| ASIC                  | P5B LArASIC             | new                           | new            | new                |

|                       | ENC ~ 500 e- @ 150pF    |                               |                | <850 e, as long as |

| noise                 | Cd at LAr               | sub 1pe resoluton             |                | possible           |

| SNR                   | >10                     |                               |                | >10                |

| Crosstalk             | <0.1%                   |                               |                | <0.1%              |

| temperature           | 77K - 300K              | 77K - 300K                    | 77K - 300K     | 160K - 300K        |

| Lifetime              | 30years                 | 30years                       | 30years        |                    |

| digitial interface    | SPI                     | I2C                           | I2C            | I2C                |

| Reference             | BGR                     | BGR / CMOS ?                  | BGR / CMOS ?   | BGR / CMOS ?       |

| anti-alias filter     | high-order filter       |                               |                |                    |

|                       |                         |                               | Temperature    | Temperature        |

| Monitor               | Temperature sensor      | Temperature sensor            | sensor         | sensor             |

|                       | 6-bit, range related to |                               |                |                    |

| DAC                   | gain                    | 10-bit (?)                    | 10-bit (?)     | 10-bit (?)         |

|                       | SE (H-Z) , SE( 50Ohm),  |                               |                |                    |

| Output stage          | DIFF                    |                               |                |                    |

| Integrated Test       |                         |                               |                |                    |

| Charge Injection Cap. | ~200fF (design)         |                               |                |                    |

| Radiation Tolerance   | N/A                     | N/A                           | N/A            |                    |

|                       |                         | In order to extend the        |                |                    |

|                       |                         | dynamic range, detector       |                |                    |

|                       | needs HCE mitigation    | signals is split into 2 weak- |                |                    |

| note                  | design                  | coupling channels to FE       |                |                    |

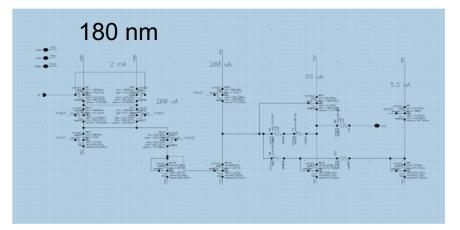

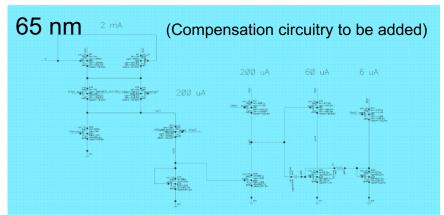

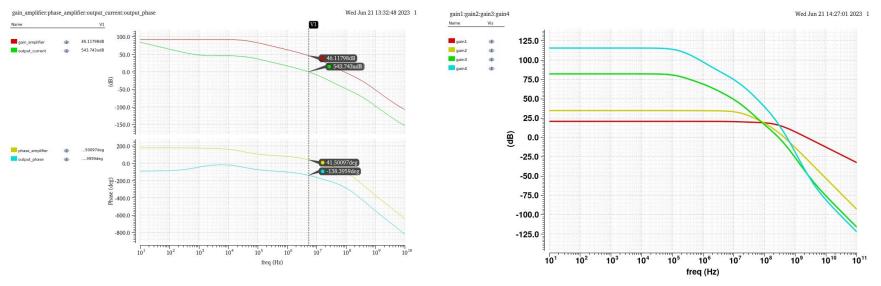

### **Ongoing 180nm to 65nm Mitigation**

• Amp1 translated to 65 nm

- Designed for the same power budget

- Input capacitance maintained at 40-50 pF

### Summary

- A weak coupling between the SiPM and input transistor is sufficient, where Cd>>Cb>>Cg. A charge sensitive amplifier (CSA), or a "voltage amplifier" is coupled to a SiPM parallel/series array by a decoupling capacitor only an order of magnitude larger than transistor capacitance, and independent of a much larger SiPM array capacitance (Cb~200-500pF for a SiPM array of 10 nF, or even 100 nF).

- The LAr FE ASIC has the required characteristics, and it made possible experimental verification of the noise calculations. Measurement results confirm calculation results and demonstrate that all the specifications can be met

#### Extract the requirements of a new FE ASIC

- Synergies with Projects

- DUNE FD3&FD4 charge readout

- 180nm fabrication for LArASIC was discontinued by TSMC

- DUNE PD readout

- PIONEER ATAR readout

- future experiments, e.g. FCC-ee

- With the support of BNL LDRD, evaluation of new FE ASIC design has started.

- Initial simulation studies with 65nm process

- At BNL, we're planning with physics simulation as inputs to motivate the technical R&D, and will continue the development towards the FD3 PDS readout development.

# Backups

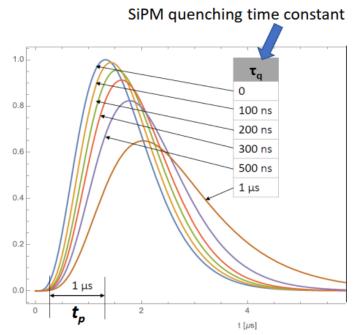

#### Is SiPM design optimal for large Area Photo detectors?: The role of Quenching Time Constant $\tau_a$ (and quenching resistance)

Long <u>quenching time constant</u> and short <u>integration time</u> makes the signal increasingly difficult to detect.

**S/N** with ES transformation by **n**:

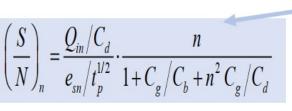

$$\left(\frac{S}{N}\right)_n = \frac{Q_{in}/C_d}{e_{sn}/t_p^{1/2}} \cdot \frac{n}{1 + C_g/C_b + n^2 C_g/C_d}$$

**Q**<sub>in</sub>= avalanche charge

C<sub>d</sub>= capacitance of <u>all SiPMs in the array connected in parallel</u>

$C_a/C_d \approx 0.05$  for weak coupling (slide 18)

t<sub>p</sub>= peaking ("integration") time of anti-aliasing filter

e<sub>sn</sub>=noise spectral density of input transistor

|                                     | t <sub>p</sub>    | t <sub>p</sub> =100ns                     | t <sub>p</sub> =500ns                     | $t_p = 1\mu s$                             |

|-------------------------------------|-------------------|-------------------------------------------|-------------------------------------------|--------------------------------------------|

| <u>xARAPUCA</u> :<br>single channel | $	au_q$ =100ns    | Ball def=0.58<br>1pe S/N=2.9<br>SPTR=31ns | ball def=0.93<br>1pe S/N=9.4<br>SPTR=37ns | ball def=0.98<br>1pe S/N=12.5<br>SPTR=53ns |

| 1pe S/N=12.5                        |                   |                                           |                                           |                                            |

| at <b>n=4, t<sub>p</sub>=1us,</b>   | t <sub>n</sub>    | t <sub>n</sub> =100ns                     | t_ =500ns                                 | $t_n = 1\mu s$                             |

|                                     |                   | ball def=0.2                              | ball def=0.58                             | ball def=0.77                              |

| <i>t<sub>a</sub>=</i> 100ns         | $\tau_{q}$ =500ns | 1pe S/N=1                                 | 1pe S/N=5.9                               | 1pe S/N=9.8                                |

|                                     |                   | SPTR=110ns                                | SPTR=76ns                                 | SPTR=81ns                                  |

Veljko. Radeka, Lidine 2021, Sept 14

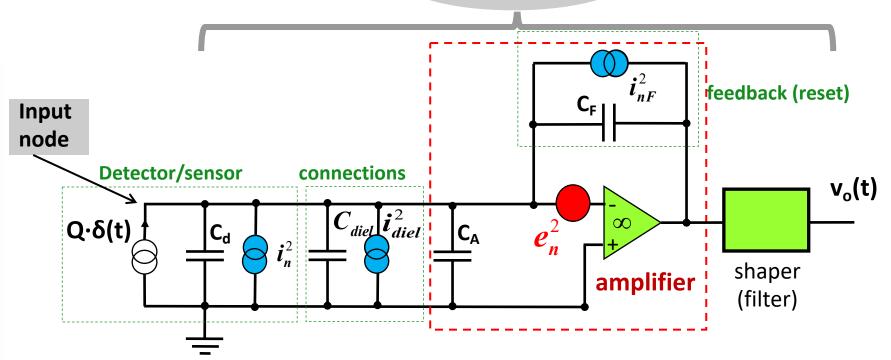

### **Noise Sources in Detector-Amplifier**

**Overall system** processing function:  $h(t); w(t); H(j\omega)$

Dominant noise sources are from the components and circuits **directly connected to the input node**. Noise sources from the rest of the signal processing chain should be made negligible.

- $i_n^2$  arises in the sensor, e.g., from the leakage (dark) current;  $i_{nF}^2$  may arise in feedback circuit

- $i_{diel}^2$  thermal fluctuations in dielectrics (dielectric loss noise)

$e_n^2$  noise associated with the input transistor:

MOSFET gain: "<u>series white noise</u>" trapping-detrapping: 1/f eq. noise voltage generator in series

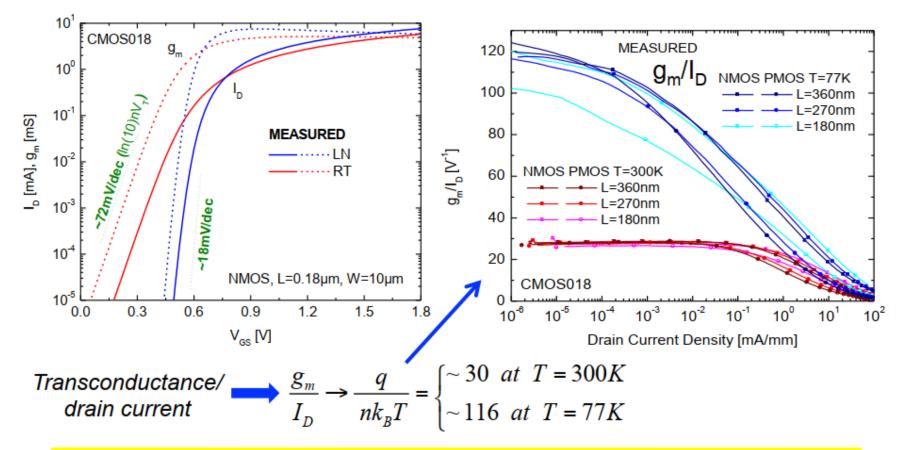

### **CMOS Characteristics in LAr**

At 77-89K, charge carrier *mobility* in silicon <u>increases</u> and *thermal fluctuations* <u>decrease</u> with *kT/e*, resulting in a *higher gain, higher* g<sub>m</sub>/I<sub>D</sub>, *higher speed* and lower noise.

## **Readout Concepts**

| Readout scheme                                                                 | 1) Continuous waveform<br>sampling and recording<br>"data streaming"                                     | 2) Event driven peak<br>sampling and timing<br><i>"data push"</i> (analog sensing)        | 3) Continuous sampling with<br>event waveform "snippet"<br>readout.<br>"data push" (digital sensing)                           |

|--------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------|

| Event sampling – sensing -<br>recording illustration                           |                                                                                                          |                                                                                           |                                                                                                                                |

| Data rate/tile<br>(total event rate = ~ 4 x 10^3<br>s <sup>-1</sup> /subarray) | 12 x 16=192 b/(sample tile)<br>384 Mbps/tile                                                             | ~ 1.536 Mbps/tile<br>< 2 Mbps/tile                                                        | Snippet [20 samples] x event<br>rate = 20 x event rate x 192 b=<br>≈ 16 Mbps/tile<br>For 32 samples snippet:<br>≈ 26 Mbps/tile |

| Comments                                                                       | Highest data rates. Most of<br>the R&D and design studies<br>so far have been devoted to<br>this effort. | Peak sensing techniques well<br>established.<br>Does not provide waveform<br>information. | Low data rate and low cable mass.<br>Lower power dissipation                                                                   |

## SiPM + LArASIC Test Stand at BNL