#### High-performance test bench for the automation of DAPHNE board minimum performance tests (Update 07/09/23)

Diego Restrepo (PhD in Physics)

Jaime Osorio (PhD in Physics)

Oscar Zapata (PhD in Physics)

Jorge Lopez (PhD in Physics)

Fabian Castaño (PhD in Electronics Engineering and Computer Science)

Universidad de Antioquia (DUNE collaboration member since June 2022)

## **Test bench advantages**

- It was identified the necessity of implement automatic test.

- Manual test involves a lot of time, reprocessing, nonstandardization, and posible failures.

- Automatic test offers better performance, multiple evaluation simultaniously, standardization and trazability.

- Also can to be use to do diagnosis and evaluation of performance in real time

## **Internal Goals**

- To define minimum operating requirements and testing protocol for DAPHNE board in DUNE environment.

- To design and manufacturing an electronic test bench based on the defined requirements and evaluation variables.

- To evaluate and validating the test bench performance through comparative tests with standard measurement and signal generation equipment.

## **Internal Goals**

- To evaluate the performance of a DAPHNE board using the test bench and compare it to the performance achieved through traditional testing methods.

- Use the test bench infrastructure to simulate hardware event signals and assess the performance of the DAPHNE board.

#### **Proposed technical tests**

- **Operating voltage test:** it verifies that the board operates within its specified voltage range in different points.

- **Board impedance test:** crucial test for maintaining signal integrity, power distribution and high-frequency performance.

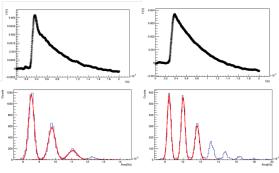

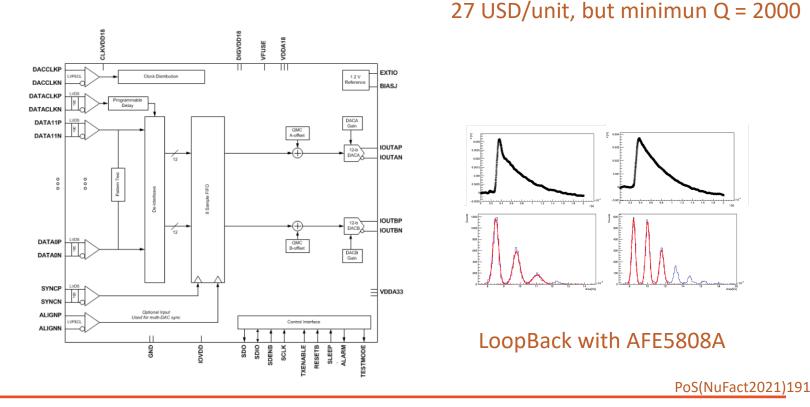

- Test of the operation of the digitizing systems (AFEs) using event signal simulations: this test helps validate the AFE's performance, linearity, noise levels, dynamic range, and overall fidelity in digitizing signals from various sources.

- Optical coupling test for communication: verifying the alignment, efficiency, and reliability of the optical coupling between the transmitting and receiving components, such as optical fibers, connectors and couplers

## **Proposed technical tests**

- **Test of the PL operation (Fast DAQ):** involves testing the PL's timing accuracy, synchronization capabilities, data integrity, and overall system throughput.

- Test of the signal conditioning system: It involves assessing parameters such as gain, frequency response, linearity, noise levels, distortion, and impedance matching.

- Test of PS operation (Slow control and configuration): it involves testing the PS reliability, responsiveness, and accuracy in performing slow control tasks, such as adjusting settings, configuring parameters, or managing system states.

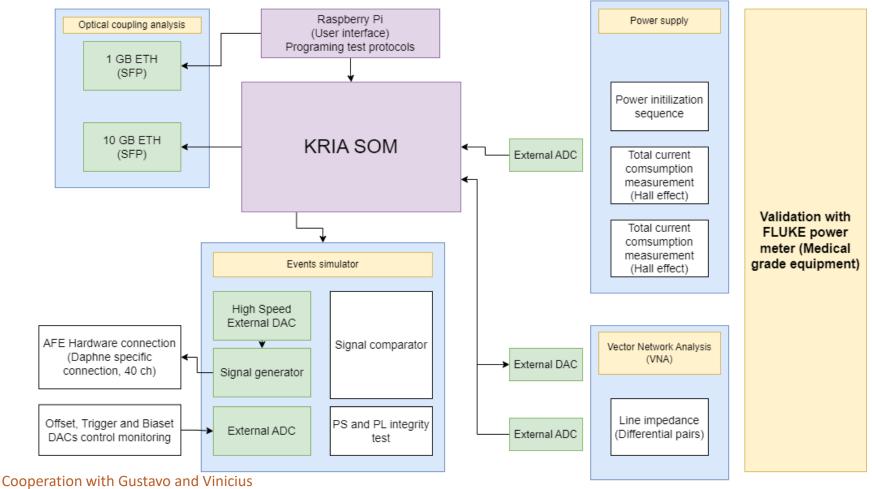

#### **Test bench architecture**

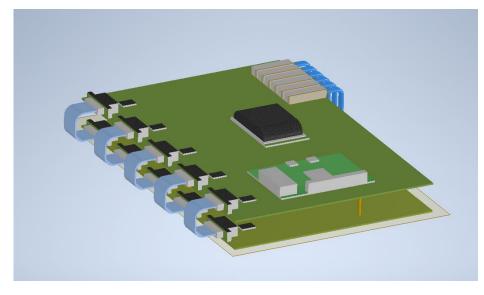

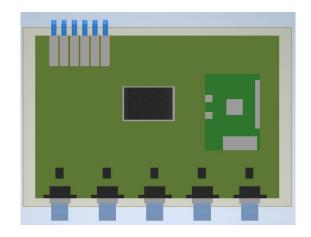

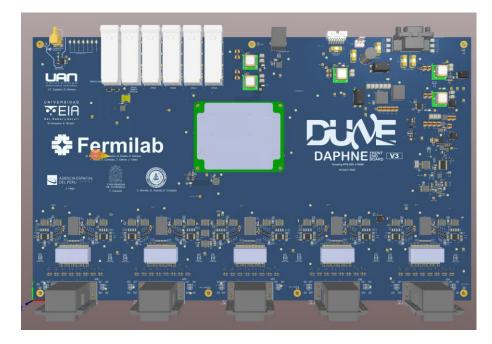

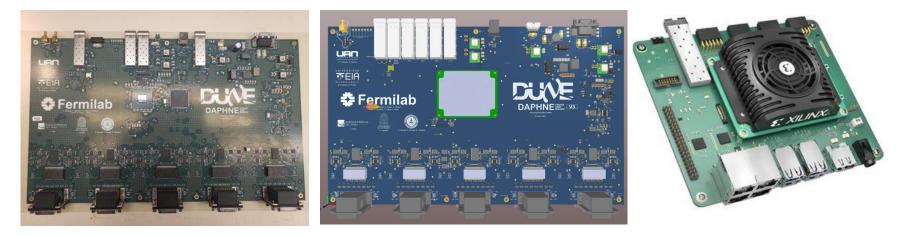

## **Test bench form factor**

- The test bench board will be coupled to the form factor of the DAPHNE board to optimize time and movements during diagnostics.

- The design will take into account that the main processor of the system is the Xilinx KRIA SOM.

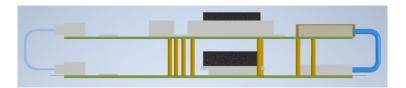

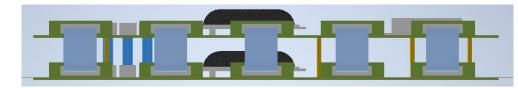

# **Vector Network Analyzer Diagram**

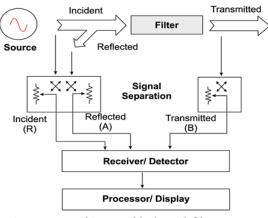

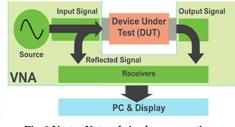

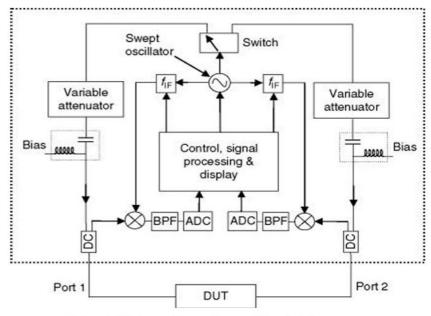

• Evaluation of Reflection and Transmission wave to calculate the characteristic impedance of trace

Fig. 5. VNA architecture blocks with filter as DUT.

Fig. 2. Vector Network Analyzer operation

Fig. 4.Network analyzer block diagram

#### **Test bench as event signal simulator**

DAC12DL3200 S ACTIVE https://www.ti.com/product/DAC12DL3200

12-bit, low-latency, dual 3.2-GSPS or single 6.4-GSPS, RF-sampling DAC (LVDS interface)

DAC38RF82 ▲ CTIVE https://www.ti.com/product/DAC38RF82 Dual-Channel, 14-Bit, 9-GSPS, 1x-24x Interpolating, 6 & 9 GHz PLL Digital-to-Analog Converter (DAC)

https://www.ti.com/product/DAC38RF84

14-Bit, 9-GSPS, 6x-24x Interpolating, 6 & 9 GHz PLL Digital-to-Analog Converter (DAC)

PoS(NuFact2021)191

#### Test bench as event signal simulator

#### DAC3154 S ACTIVE

https://www.ti.com/product/DAC3154

Dual-channel, 10-bit, 500-MSPS digital-to-analog converter (DAC) with input FIFO and current sour

#### Test bench as event signal simulator