## 4D Tracking @ SLAC

- Pioneered the <u>High Granularity Timing Detector</u> (HGTD) at ATLAS

- Designed the 20ps TDC of the ASIC chip (**Bojan Markovic**)

- HGTD Physics and Simulation convenership for 6 years (Ariel Schwartzman)

- Currently investigating <u>4D tracking</u> detectors for future HL-LHC upgrades beyond Run 4, and future colliders

https://cds.cern.ch/record/2870326

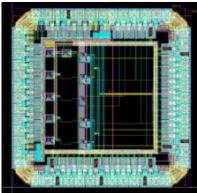

- Expertise in designing pixel front-end ASIC with both TDCs and ADCs for various applications.

- Recent examples of timing circuits include TDC designs for high-energy physics, ultra-fast photon science, and biomedical imaging, and ADC designs for high-energy physics and photon science

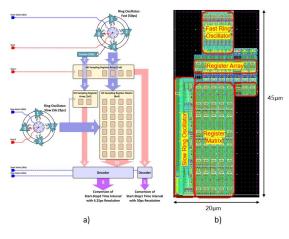

- Within DOE's HEP Detector R&D program funding, we developed a TDC architecture in 28nm CMOS capable of reaching 6.25ps timing resolution within core area of 45µm x 20µm and average power consumption of 18.4 µW for 10% occupancy (2.9 µW for 1% occupancy)

## **RDC3** plans

- DOE's HEP Detector R&D program SLAC project focused on development of <u>electronics for 4D in 28nm node</u>:

- Sub-10ps TDC (Bojan Markovic)

- Constant fraction discriminator (CFD) (Victor Turbiner, EE Ph.D student)

- ADC (Aldo Pena Perez)

- DOE's Accelerate Innovations in Emerging Technologies 3D Integrated Sensing Solutions project (SLAC, Fermilab, LLNL)

- Develop LGAD sensors in commercial 12" CMOS process and couple to dedicated front-end in 28nm with wafer-to-wafer bonding (Julie Segal, Christopher Kenney, Lorenzo Rota, Bojan Markovic)

Abstract submitted

- Physics, simulation, and detector optimization

- HL-LHC 4D tracking upgrade and future Higgs Factories and high energy colliders (Ariel Schwartzman + students)

- 4D Clustering/Seeding/Tracking algorithms and physics event reconstruction

- Synergies with 5D calorimetry