## Full 10kt Sim/SigProc Update

Haiwang Yu (BNL) 2023-11-06

### **Full 10kt initial test**

- Initial testing showed in the 2023 Jan Collab. Meeting

- https://indico.fnal.gov/event/53965/contributions/257909/

- Memory/time could be reduced

- Some updates on memory reduction and plans on speed optimization today

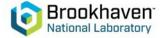

## Wire-Cell Dataflow graph

- Motivated by multi-threading/memory share needs

- Need per-APA class instance per-APA memory increasing

- components

- services

Currently no easy way to skip components

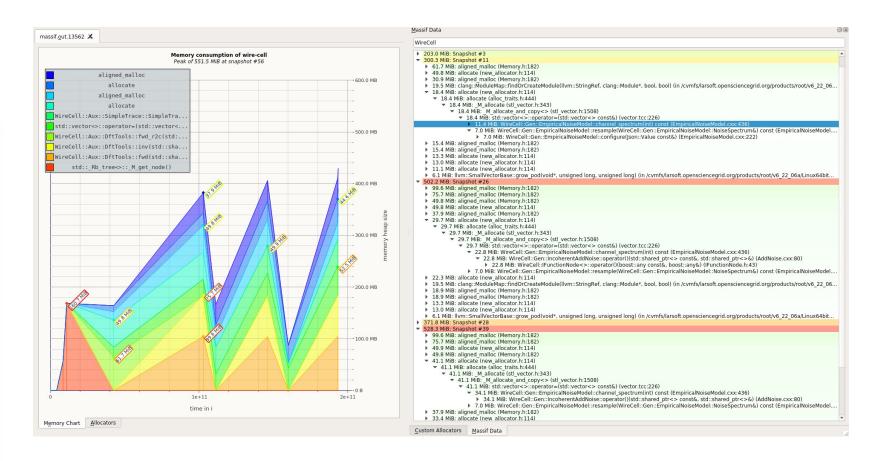

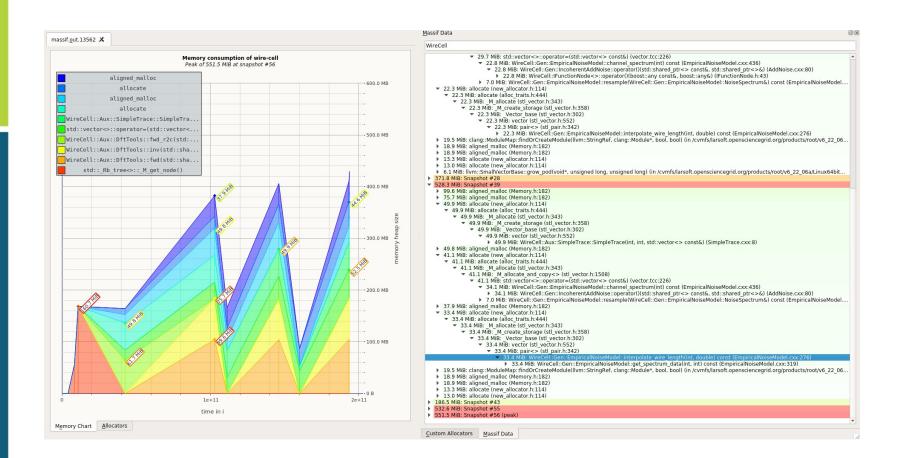

#### Use one NoiseModel for all APAs

Some caching used in the NoiseModel service (profiling in backup slides)

- currently every AddNoise component has its own NoiseModel service

- noise spectra determined by plane, wire-length, gain, shaping

- → could be independent of APAs

- → one NoiseModel for all APAs

- Need a lock to protect cache modification (service needs to be thread safe)

- The per-APA increasing part is gone if use this

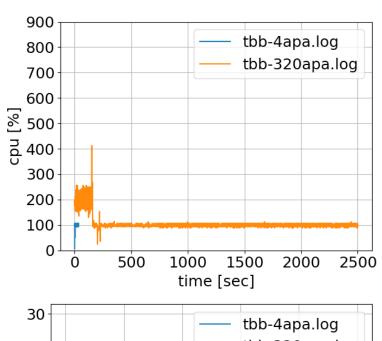

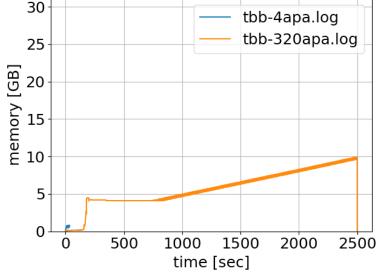

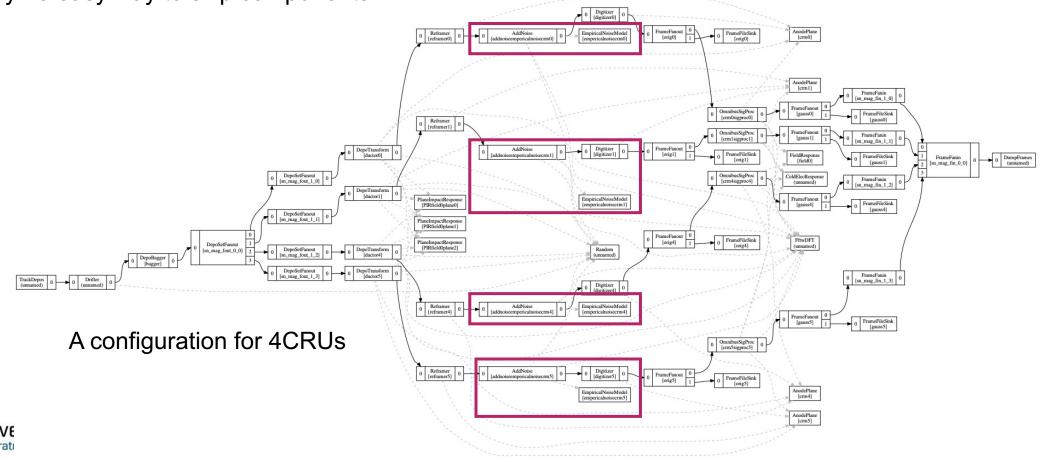

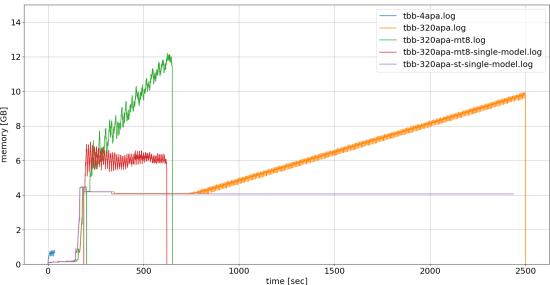

- ST: 2430 sec, ~4GB

- 8-threads: 620 sec, ~6GB

- 180 compiling jsonnet, 420 core processing

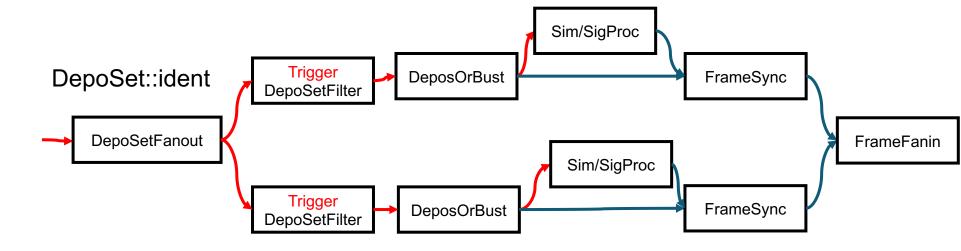

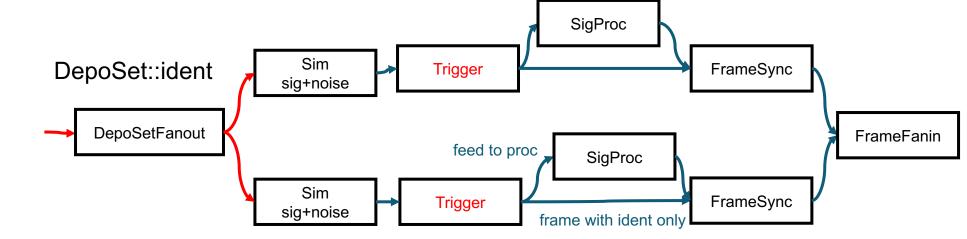

## Shortcuts to skip some processing

issue #148

Cheat trigger to skip both Sim/SigProc

- Sim all APAs

- Trigger alg. to determine whether to do SigProc

#### **Next**

Validate the single noise model method

Finish the async nodes/skip path

• <a href="https://github.com/WireCell/wire-cell-toolkit/pull/169">https://github.com/WireCell/wire-cell-toolkit/pull/169</a>

Further reduce the per-APA component memory

Randomness: neither engines in WCT is deterministic for now

- issue 242

- Easier to fix the pgrapher one (single thread only).

- Longer term to fix the TbbFlow (multi-thread).

# backup

```

---// fixme: see https://github.com/WireCell/wire-cell-gen/issues/29

---local make_noise_model = function(anode, csdb=null) {

31

type: "EmpiricalNoiseModel",

32

....name: "empericalnoise%s"% anode.name,

33

-data: -{

34

----anode: wc.tn(anode).

35

----dft: wc.tn(tools.dft),

36

color= chanstat: if std.type(csdb) == "null" then "" else wc.tn(csdb),

37

....spectra_file: params.files.noise,

38

....nsamples: params.daq.nticks,

39

40

-period: params.daq.tick,

41

wire length scale: 1.0*wc.cm, // optimization binning

42

uses: [anode, tools.dft] + if std.type(csdb) == "null" then [] else [csdb],

43

44

...}.

----local noise models == [make noise model(anode) for anode in tools.anodes],

45

46

47

--- local add noise = function(model) g.pnode({

48

....type: "AddNoise",

49

....name: "addnoise%s"%[model.name],

50

51

---- data: {

52

....rng: wc.tn(tools.random),

dft: wc.tn(tools.dft),

53

.... model: wc.tn(model),

54

----nsamples: params.daq.nticks,

55

replacement_percentage: 0.02, // random optimization

56

....}}, nin=1, nout=1, uses=[tools.random, tools.dft, model]),

57

58

----local noises == [add_noise(model) for model in noise_models],

59

```

Each APA cache its own noise spec.