#### **DAPHNE Status**

**Deywis Moreno Consortium Meeting** December 12, 2023

#### **Outline**

- DAPHNE\_V2A firmware

- Self-trigger

- DAPHNE\_V3 update

## **Current Monitoring**

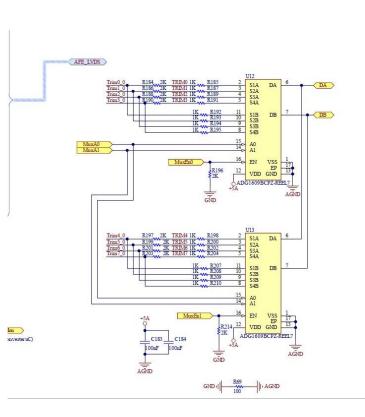

PGA280+ADS1259

Analog mux to select the Trim current to be measured

Current on Load Resistor calculated from the Voltage measured by the 24-bit ADC

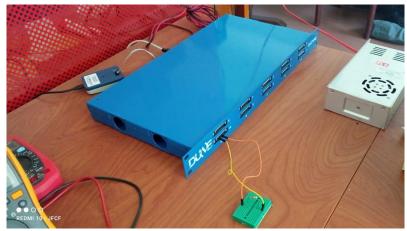

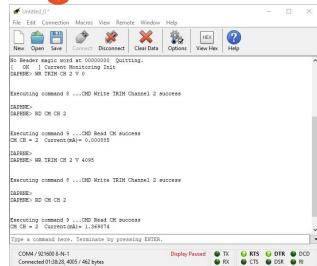

**Current Monitoring Testing**

Tests performed on DAPHNE V1 at UAN and Fermilab

1K resistor connected between Trim 2 (pin 11) and AGND (using the Cold Electronics VR pin 14), E connector

WR TRIM CH xx V yy: set Trim Voltage on channel xx to yy value (from 0 to 4095 referred to DAC output). We will implement a command that take this value in Volts

RD CM CH X: measurement of the SiPM current of channel X (in mA)

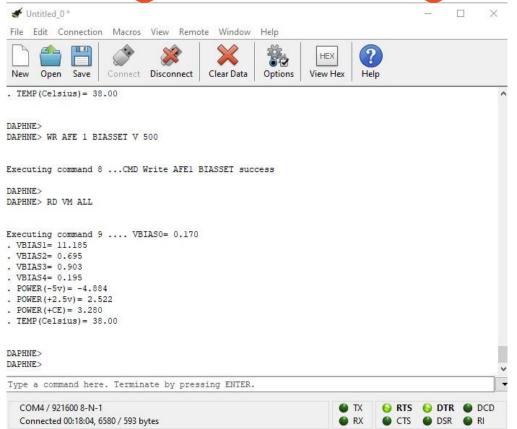

### Voltage Monitoring Test

WR VBIASCTRI V xx: set the General Bias to XX (from 0 to 1000), referred to DAC output from 0 to 1 V (DC-DC converter)

WR AFE X BIASSET V YY: set voltage on AFE X (from 0 to 4) to YY (from 0 to 4095 referred to DAC output), we will implement an update to enter the direct value in volts

RD VM ALL: measurement of the VBias (from 0 to 4) in volts, power supplies (-5V, 2,5 V, Cold electronics) and microcontroller temperature

# **Monitoring Work Ongoing**

- Calibration of the Voltage monitoring

- Improvement of the uC temperature measurement (calibration, mathematical model, etc) according to the datasheet

- Verification and calibration of the CM analog multiplexing circuit (originally designed by Sten H. for Mu2E FEB)

- Experimental test performed on DAPHNE V2 at Milano-Bicocca in with the help of Esteban C. (Scheduled for December 12th 2023)

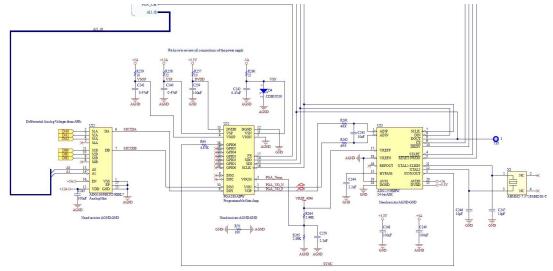

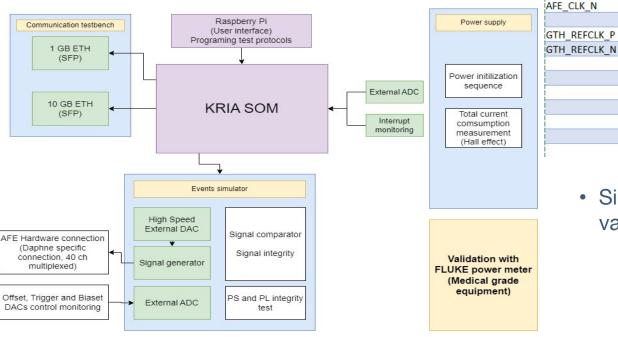

#### High-performance test bench for the automation of DAPHNE

AFE CLK P

board minimum performance tests

Signal's definition and test point validation

Timming signals Voltage signals Clock signals Power signals Columnal

CLK625 P

CLK625 N

CLK100 P

CLK100 N

25MHZ CLK

VREF 4096

+3.3VDPS

+1.8VDPS

+3.3VD

+1.8VD

+5VD

PG3V3A

PG1V8A

+3.3VA

PG1V8A

+5.5V

+3.6V

-5VA

+5VA

TRIM[7..0]

OFFSET[7..0]

VBIAS CTRL

VGAIN[4..0]

**VBiasRaw**

BiasSet

DA

DB

BiasMon

BIAS SET[4..0]

Test bench Architecture

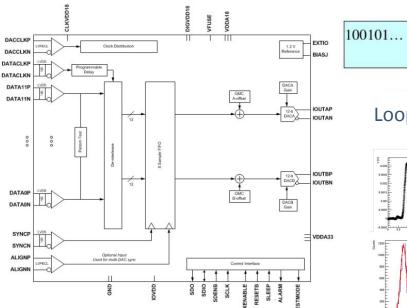

## Test bench as event signal simulator

Part selection

DAU3154

Dual-channel, 10-bit, 500-MSPS digital-to-analog converter (DAC) with

input FIFO and current sour

DAC

#### LoopBack with AFE5808A

# **Self-Triggering**

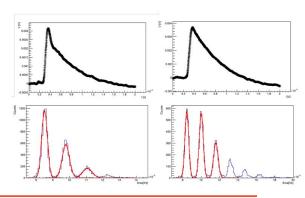

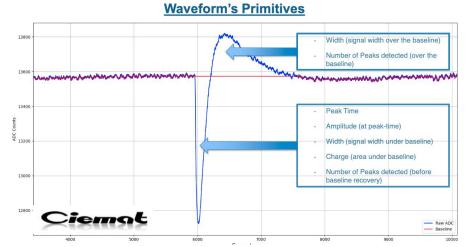

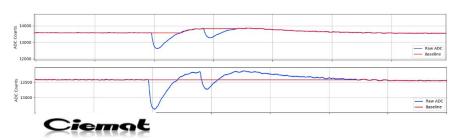

- Different algorithms are under testing at Ciemat

- University EIA is also working in a match filter for triggering

- In previous WG meetings discussions for a join work is planned

Self-trigger algorithm for the Photon Detection System(PDS) in DUNE

> Edgar V. Rincón Gil, email: edgar.rincon@eia.edu.co Daniel Ávila Gómez, email: daniel.avila@eia.edu.co

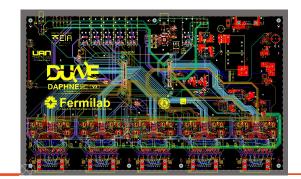

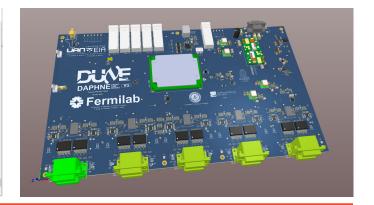

#### DAPHNE V3

- 12 PCBs produced; 10 DAPHNE V3 assembled

- 2 DAPHNE V3 were delivered (vendor was unsure of ball grid array quality)

- Many bad ball grid array connections found

- Boards were reworked (all BGA connections reflowed individually). 1 board now looks good & is being tested, the other has no obvious BGA problems, but the Kria SOM doesn't boot properly.

- Decision to rework the remaining 8 boards will be made this week.

```

Started Target Communication Framework agent.

Starting Record Runlevel Change in UTMP...

Finished Record Runlevel Change in U[ 13.709709] kria-dashboard.sh

PetaLinux 2022.2 release S10071807 xilinx-kr260-starterkit-20222 ttyPS1

ilinx-kr260-starterkit-20222 login: petalinux

llinx-kr260-starterkit-20222:~$

linx-kr260-starterkit-20222:~

```

#### **Work ongoing**

- DAPHNE V2A installation and integration at CERN is progressing

- Design of a DAPHNE test bench ongoing

- Self-Trigger algorithms under development in many labs. Performance Comparison needs to be done

- DAPHNE\_V3 testing is ongoing; decision on rework of remaining 8 boards will be made late this week.