### Cold Electronics Development for LAr TPC

Hucheng Chen On behalf of the Cold Electronics Team March 21<sup>st</sup>, 2013

a passion for discovery

## Outline

- Introduction

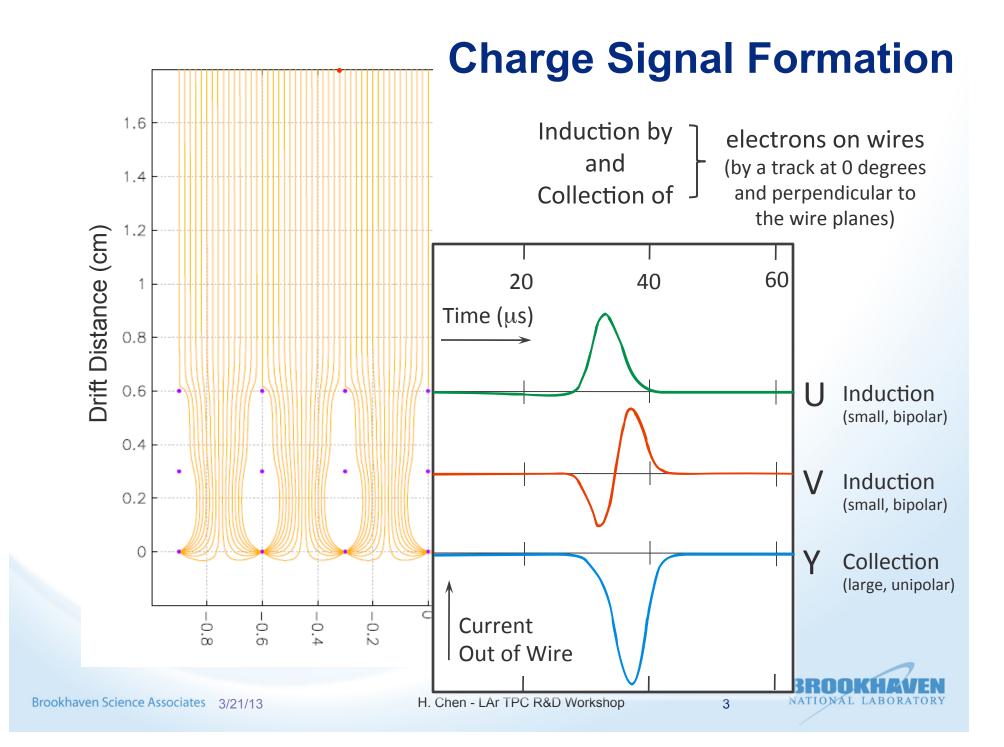

- LAr TPC Signal Properties

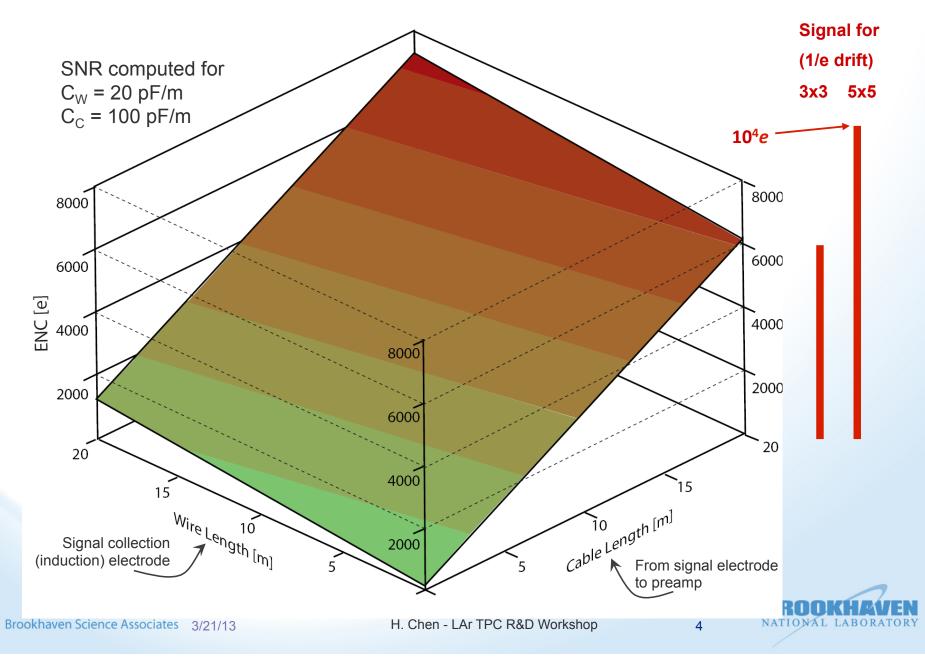

- Why Use Cold Electronics

- Cold Electronics Development

- MicroBooNE

- LBNE

- 35 Ton

- CMOS Lifetime

- CMOS in DC operation: analog FE ASIC

- CMOS in AC operation: logic circuit and FPGAs

- Summary

## **Why Use Cold Electronics**

#### Cold Electronics Development

- MicroBooNE

- LBNE

- 35 Ton

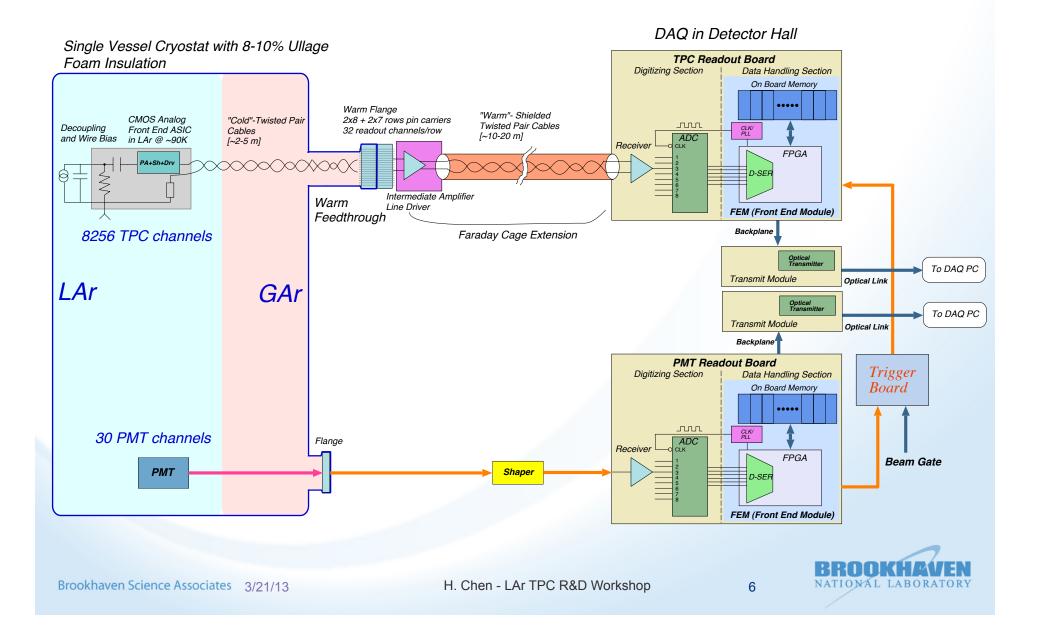

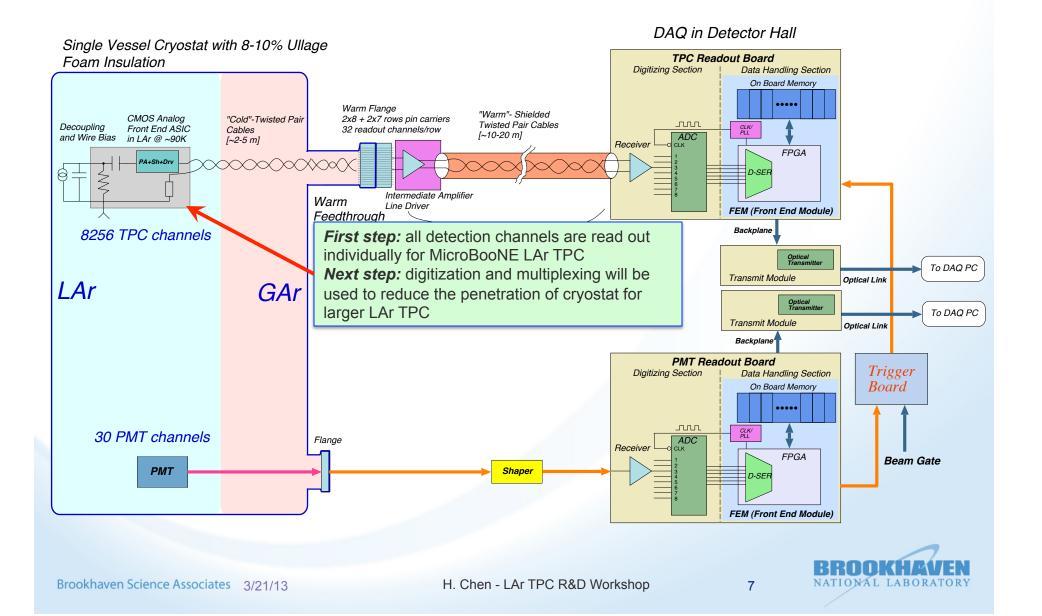

### **MicroBooNE Readout Electronics System**

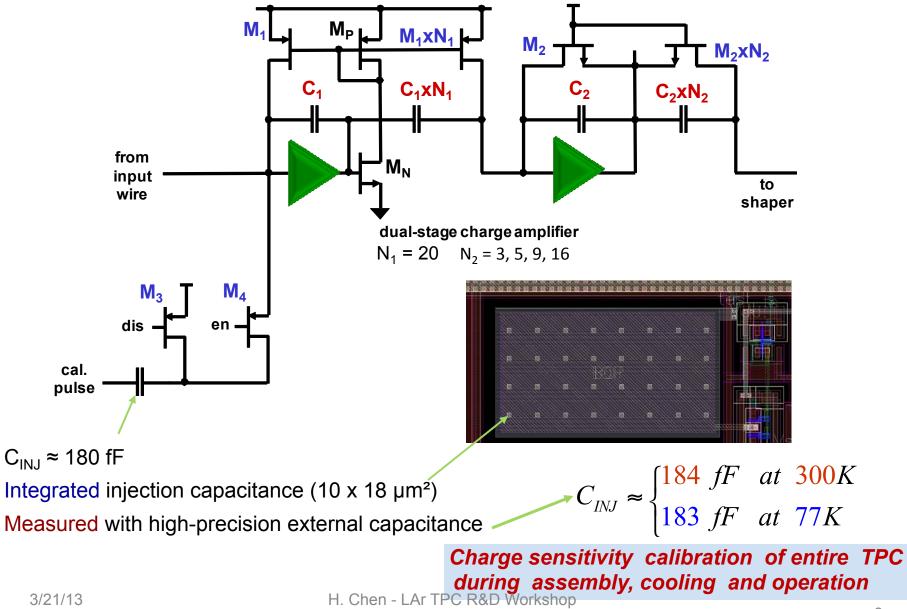

#### Cold Electronics ASIC - Front-End Detail and Calibration Scheme

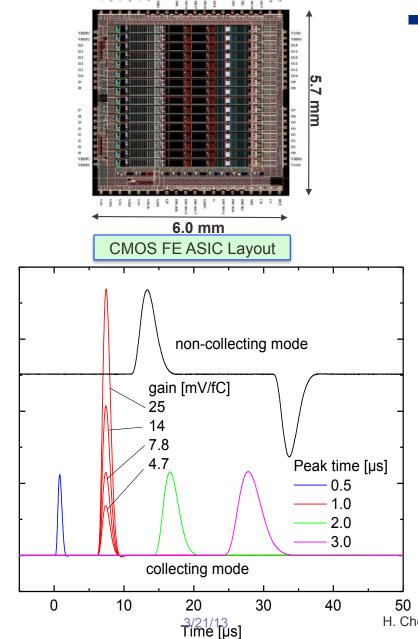

CMOS Analog Front End ASIC

- 16 channels per chip

- Charge amplifier, high-order filter

- Adjustable gain: 4.7, 7.8, 14, 25 mV/ fC (55, 100, 180, 300 fC)

- Adjustable filter time constant (peaking time): 0.5, 1, 2, 3 µs

- Selectable collection/non-collection mode (baseline)

- Selectable dc/ac (100 µs) coupling

- Rail-to-rail analog signal processing

- Band-gap referenced biasing

- Temperature sensor (~ 3mV/°C)

- 136 registers with digital interface

- 5.5 mW/channel (input MOSFET 3.6 mW)

- ~ 15,000 MOSFETs

- Designed for long cryo-lifetime

- Technology CMOS 0.18 µm, 1.8 V, 6M, MIM, SBRES

H. Chen - LAr TPC R&D Workshop

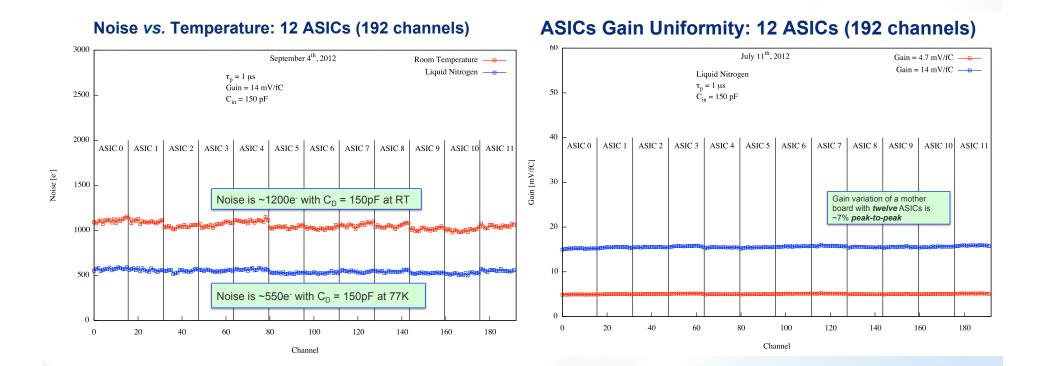

Horizontal cold motherboard with 12 ASIC chips (192 channels) populated

Vertical cold motherboard with 6 ASIC chips (96 channels) populated

#### Cold Mother Board

- House front end ASIC

- Rogers 4000 series base material

- Provide detector signal interconnections

- Provide ASIC control and monitoring signals, calibration network

- Provide bias voltage distribution for wire planes

- Horizontal version

- 96 "Y" channels

- 48 "U" channels

- 48 "V" channels

- Vertical version

- 96 "U" or "V" channels

Brookhaven Science Associates 3/21/13

H. Chen - LAr TPC R&D Workshop

#### Cold Electronics Development

- MicroBooNE

- LBNE

- 35 Ton

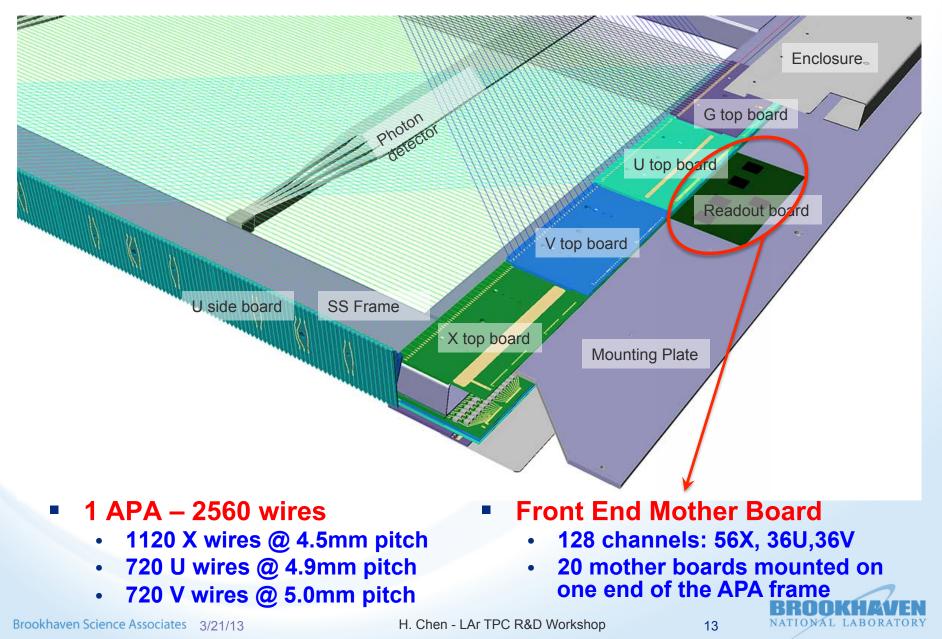

## **Cold Electronics for LBNE LAr TPC**

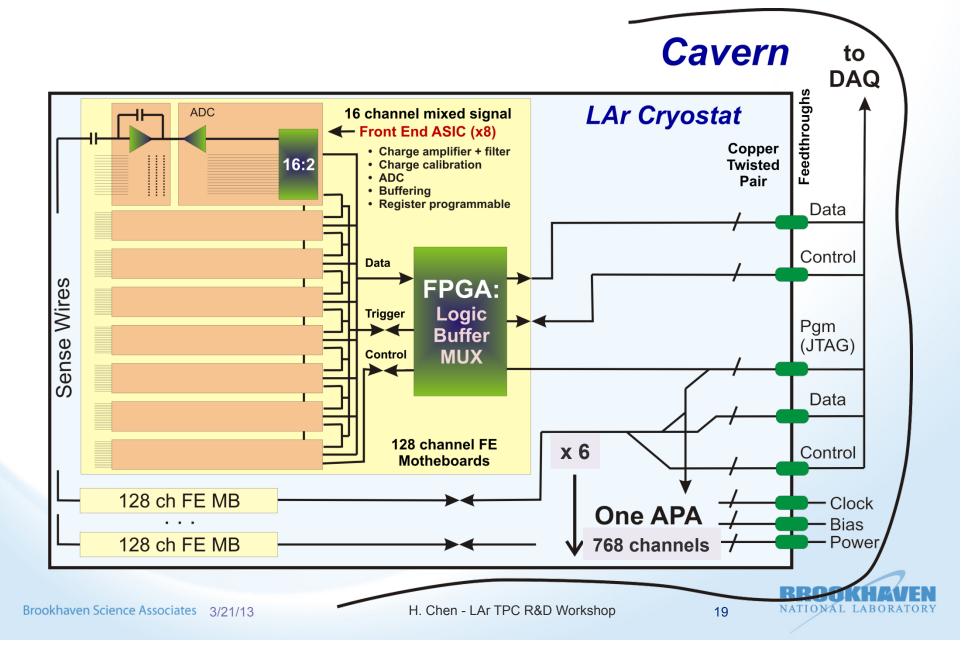

#### **Cold Electronics for LBNE LAr TPC** Cavern to DAQ 16 channel mixed signal ADC LAr Cryostat Front End ASIC Charge amplifier + filter Buffer 16:2 Charge calibration • ADC Nx Redundancy MUX • Zero-surpression Logic Buffering Control Token passing bus N:N Register programmable ASIC - Bias 20:1 - Power Control MUX Sense Wires Feedthroughs Logic Control ASIC Nx Redundancy MUX 16:1 Logic Control N:N CM or LV differential ASIC Bias digital signaling 20:1 Power Control 128 channel FE Optical x20 **Motheboards** or Copper 128 ch FE MB Driver One APA . . . 128 ch FE MB 2560 channels Brookhaven Science Associates 3/21/13 H. Chen - LAr TPC R&D Workshop NATIONAL LABORATORY 14

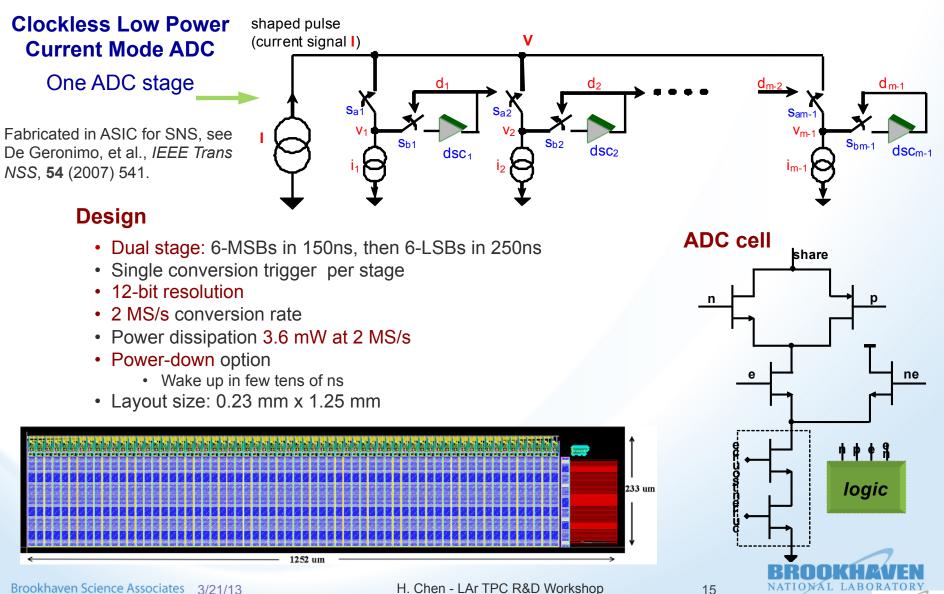

#### **ADC** - Architecture

Brookhaven Science Associates 3/21/13

H. Chen - LAr TPC R&D Workshop

BROOKHAVEN

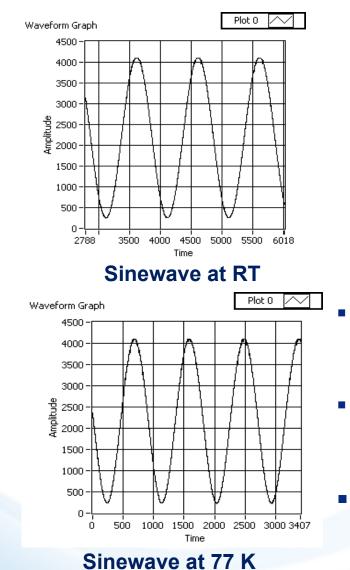

### **Single Cold ADC Test Results**

ADC HIST 240000 220000 200000 180000 160000 140000 COUNT 120000 100000 80000 60000 40000 20000 0-1365 1370 1375 1381 1361

#### **ADC Output Histogram DC**

#### **Measured linearity**

• DNL < 1.5 LSB for majority of codes

BIN

- INL ~1% of Range

- Equivalent input noise measurement

- 1.27 LSB

- Effective resolution: 11.6 bits

- The ADC has been tested with an FPGA, both immersed in LN<sub>2</sub>

NATIONAL LABORATORY

Brookhaven Science Associates 3/21/13

#### Cold Electronics Development

- MicroBooNE

- LBNE

- 35 Ton

### **Cold Electronics for 35T LAr TPC**

#### 3 APA – 2304 wires total

- Each APA has 768 wires

- 336 X wires @ 4.5mm pitch

- 216 U wires @ 4.9mm pitch

- 216 V wires @ 5.0mm pitch

Brookhaven Science Associates 3/21/13

#### Front End Mother Board

- 128 channels: 56X, 36U,36V

- 6 mother boards mounted on one end of the APA frame

H. Chen - LAr TPC R&D Workshop

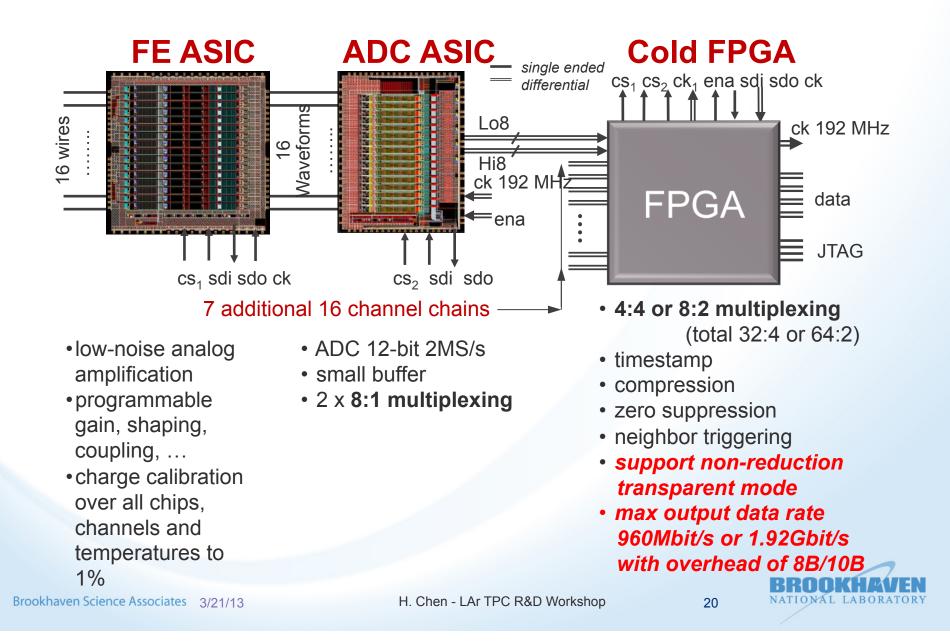

## **Cold Electronics for 35T LAr TPC**

### **Key Components of Cold Electronics**

# **Cold FPGA Test**

|        |               |            | Speed of GTX |          | Memory     | Core        |                     |   |

|--------|---------------|------------|--------------|----------|------------|-------------|---------------------|---|

| Vendor | Family        | Technology | [Gbps]       | # of GTX | [Mbit]     | Voltage [V] | Status              |   |

| ALTERA | Arria GX      | 90nm       | 3.125        | 4 - 12   | 1.2 - 4.5  | 1.2         | Tested by BNL       | ~ |

| ALTERA | Arria II      | 40nm       | 6.375        | 8 - 24   | 2.9 - 16.4 | 0.9         | Tested by BNL       | X |

| ALTERA | Stratix II GX | 90nm       | 6.375        | 4 - 20   | 1.4 - 6.7  | 1.2         | Tested by SMU       | V |

| ALTERA | Cyclone IV E  | 60nm       | N/A          | N/A      | 0.3 - 3.9  | 1.0, 1.2    | Tested by BNL       | V |

| ALTERA | Cyclone IV GX | 60nm       | 3.125        | 2 - 8    | 0.5 - 6.5  | 1.2         | Being tested at BNL | ~ |

| ALTERA | Cyclone V GX  | 28nm       | 3.125        | 4 - 12   | 1.2 - 12.2 | 1.1         | To be tested        |   |

| XILINX | Virtex 5      | 65nm       | 6.5          | 0 - 24   | 0.9 - 18.6 | 1.0         | To be tested        |   |

Cyclone IV GX Transceiver Starter Board

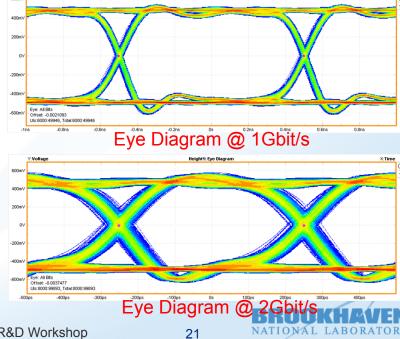

- Test of Cyclone IV GX Transceiver Starter Board in LN<sub>2</sub>

- Transceiver works well at both 1Gbit/s and 2Gbit/s

- JTAG configuration works

- AS configuration works with Altera EPCS device

- Internal memory works with SignalTap

- Internal PLL and fabric work for clock generation

- On board SRAM works with BIST

Brookhaven Science Associates 3/21/13

H. Chen - LAr TPC R&D Workshop

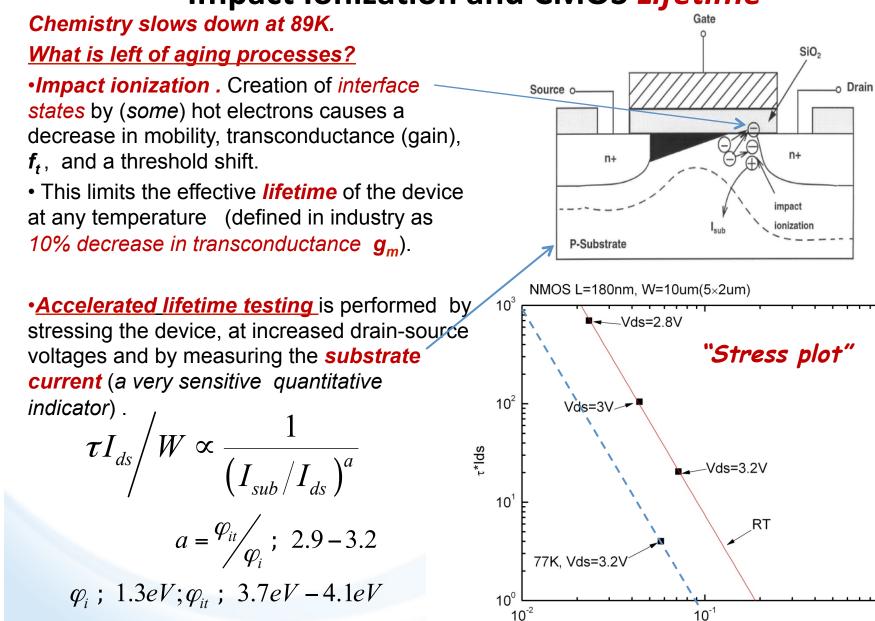

#### Impact Ionization and CMOS Lifetime

Brookhaven Science Associates 3/21/13

$10^{\circ}$

Isub/Ids

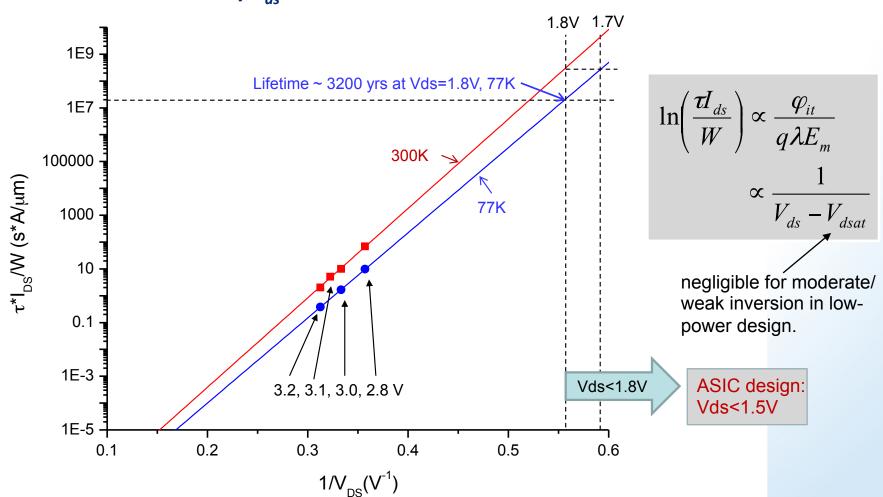

Lifetime VS  $1/V_{ds}$  extracted from the stress measurements

NMOS L=180nm, W=10µm (5x2µm); nominal core voltage 1.8V. The projected lifetime at 300K is ~ an order of magnitude longer than at 77K. Reducing  $V_{ds}$  at 77K by ~ 6% makes the lifetime equal to that at 300K. Design at low  $I_{ds}$ /W for longer lifetime.

Brookhaven Science Associates 3/21/13

H. Chen - LAr TPC R&D Workshop

#### CMOS in AC operation: Logic Circuits and FPGAs

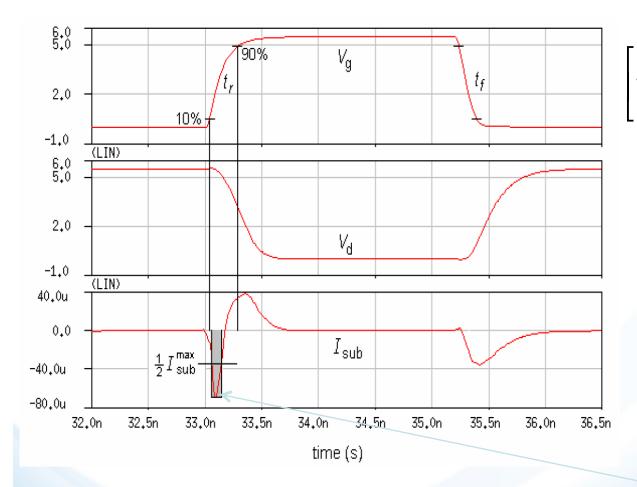

• It has been long established, e.g. Quader&Hu et al. (1994), that *ac* and *dc* hotcarrier induced degradation is the same if the *effective stress time* is taken into account. This quasi-static model, confirmed recently by White&Bernstein (2006), considers the *ac* stress as a series of short *dc* stresses strung together.

• The lifetime of a logic circuit driven at a clock frequency can be related to the lifetime of the NMOS transistor under continuous *ac* operation in terms of the ratio of the effective stress time during a change of state and the clock period. Thus the *lifetime of digital circuits (ac operation) is extended by the inverse duty factor*  $4/(f_{clock}t_{rise})$ , *compared to dc operation.* This factor is large (>100) for deep submicron technology and clock frequencies needed for LAr TPC readout.

• Design guidelines for digital circuits and FPGAs: Keep the inverse duty factor high. As a an additional conservative measure, reducing  $V_{ds}$  by 10% adds an order of magnitude margin to the lifetime.

#### Effective Stress Time is a small fraction of the Clock Cycle:

$\left|\frac{ac \text{ stress time}}{dc \text{ stress time}}\right| \approx \frac{\left(f_{clock}t_{rise}\right)}{4}$

Standard method for accelerated stress testing of FPGAs: observe ring oscillator frequency under severe V<sub>ds</sub> stress (Wang et al. 2006)

(Degradation of I<sub>ds</sub> leads to increased rise (propagation) time and reduced ring oscillator frequency.)

25

Hot-carrier induced degradation occurs only when the <u>substrate current</u> is high, i.e., nominal  $V_{ds}$  and high  $I_{ds}$ .

### Summary

- Cold electronics installed close to the detector elements is critical to make possible giant LAr TPCs and improve signal to noise ratio

- CMOS at Low Temperature

- Started from .18um CMOS technology with only 300K models for analog front end; parameters extracted at 77K

- **<u>CMOS found functioning at cryogenic temperature with</u>** <u>increased gain (g<sub>m</sub>/l<sub>ds</sub>) and lower noise</u>

- **Development of Cold Electronics for LAr TPC**

- The CMOS analog FE ASICs equipped mother boards are being tested for final production of MicroBooNE experiment

- We have accumulated ~1500 chip•immersions in LN<sub>2</sub> without any failures due to thermal contraction/expansion

- ADC characterization test and cold FPGA lifetime study are being conducted

- Analog FE ASIC + ADC ASIC + Cold FPGA will be used to equip the 35 Ton LAr TPC Brookhaven Science Associates 3/21/13

H. Chen - LAr TPC R&D Workshop