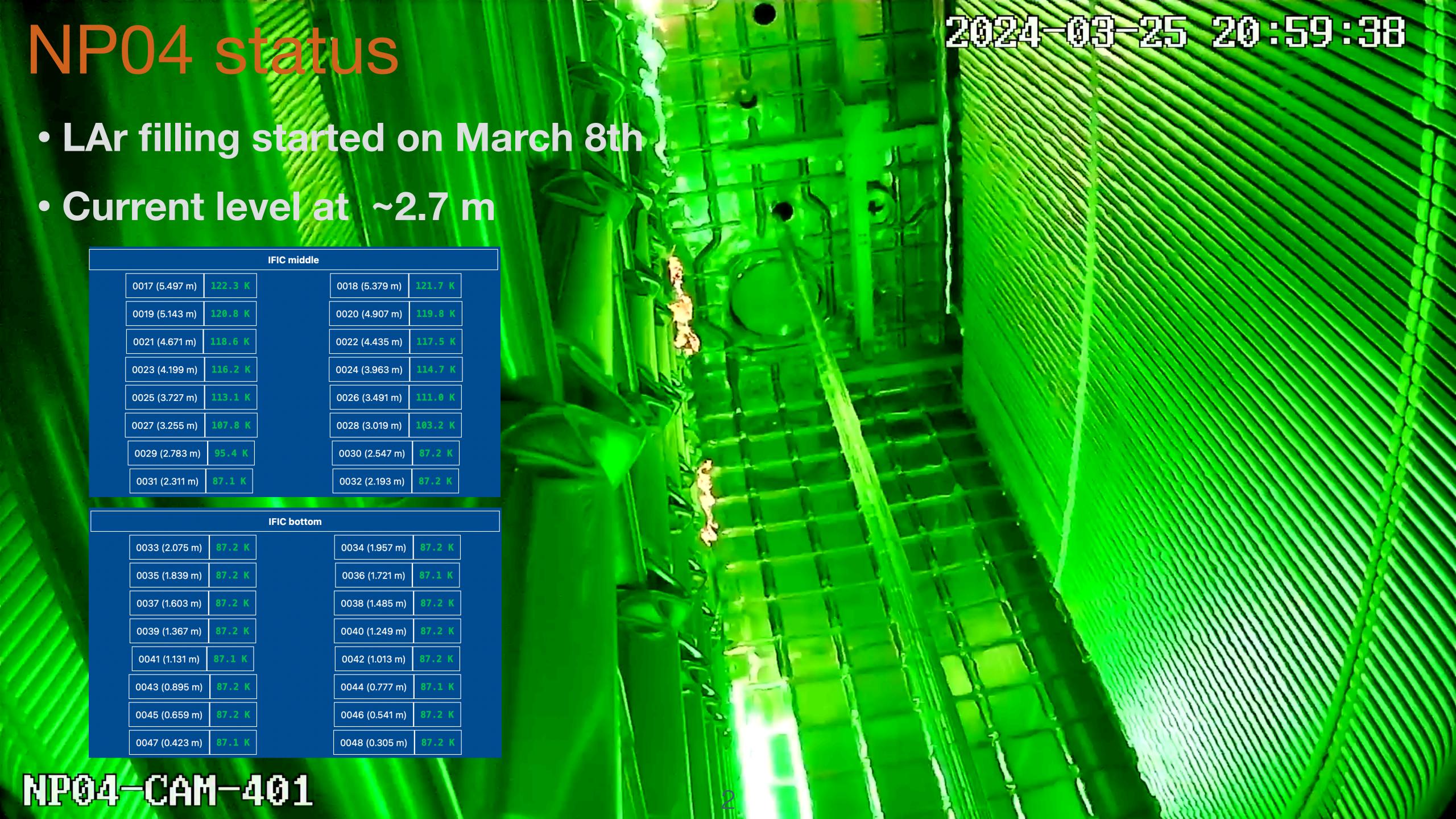

# NP04 status and plans

A. Cervera IFIC-Valencia

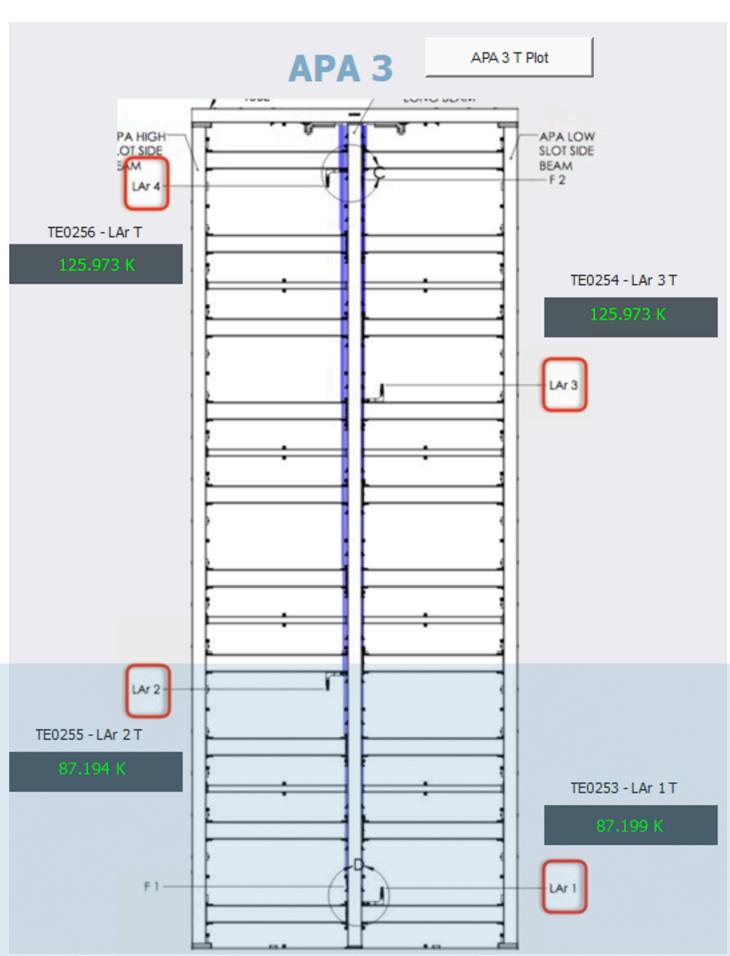

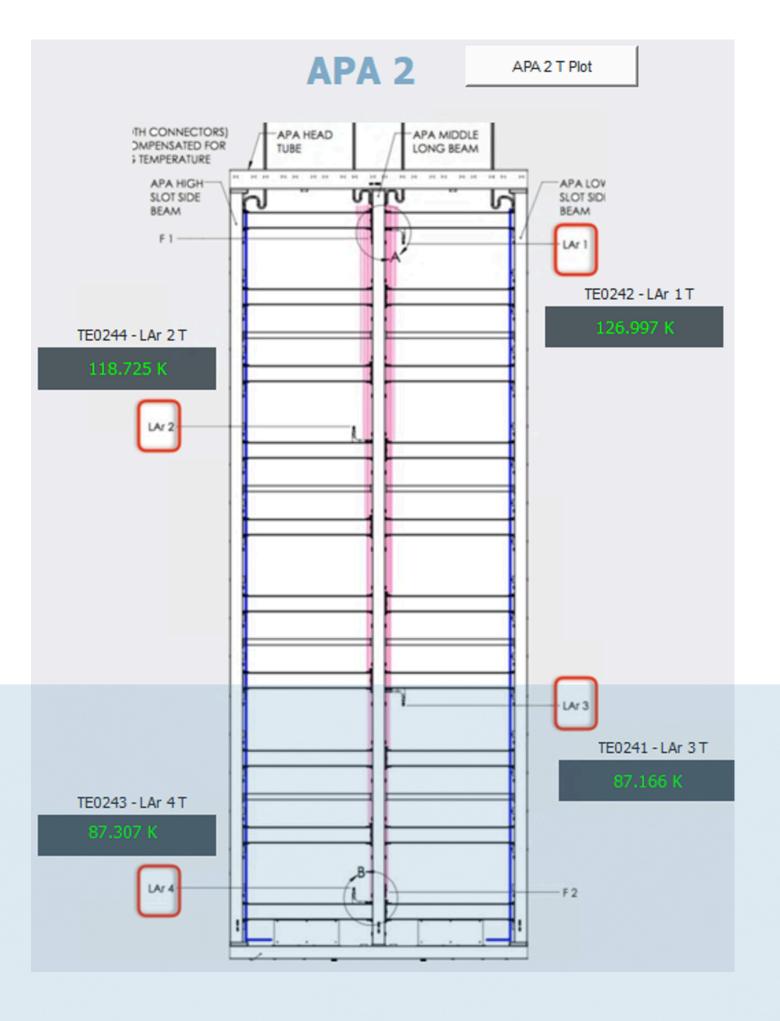

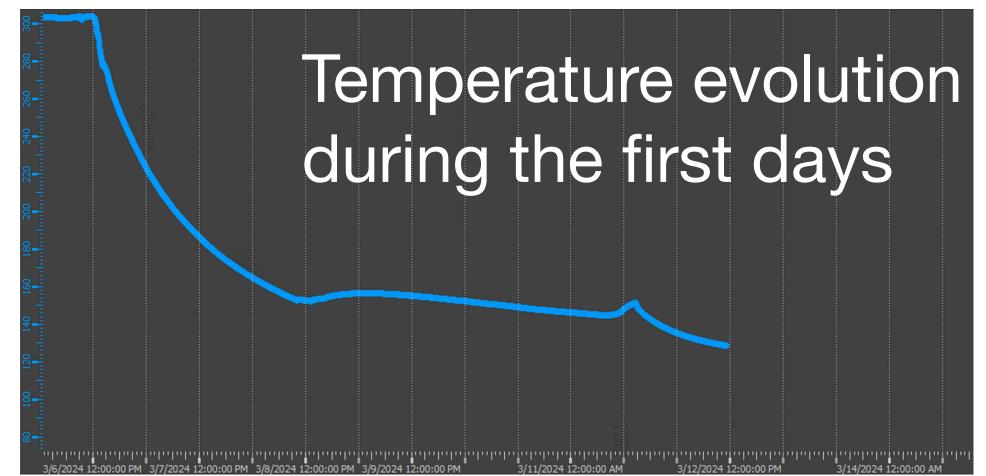

# Temperatures in APAs

LAr level

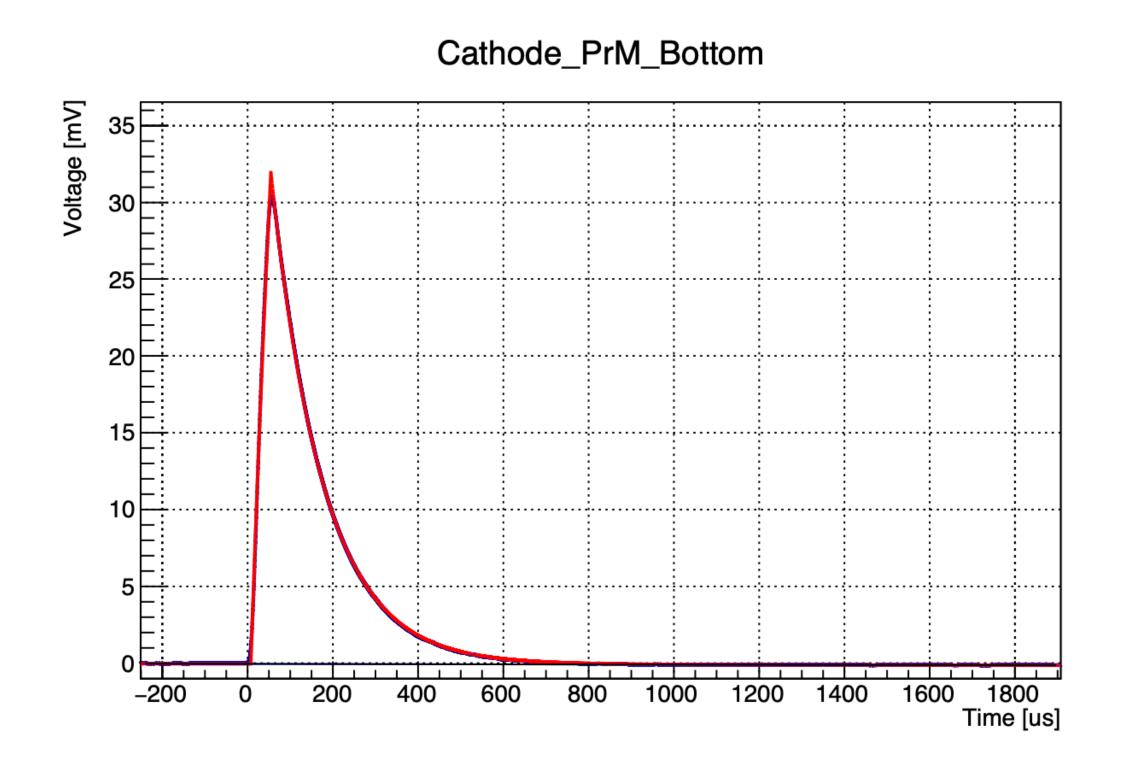

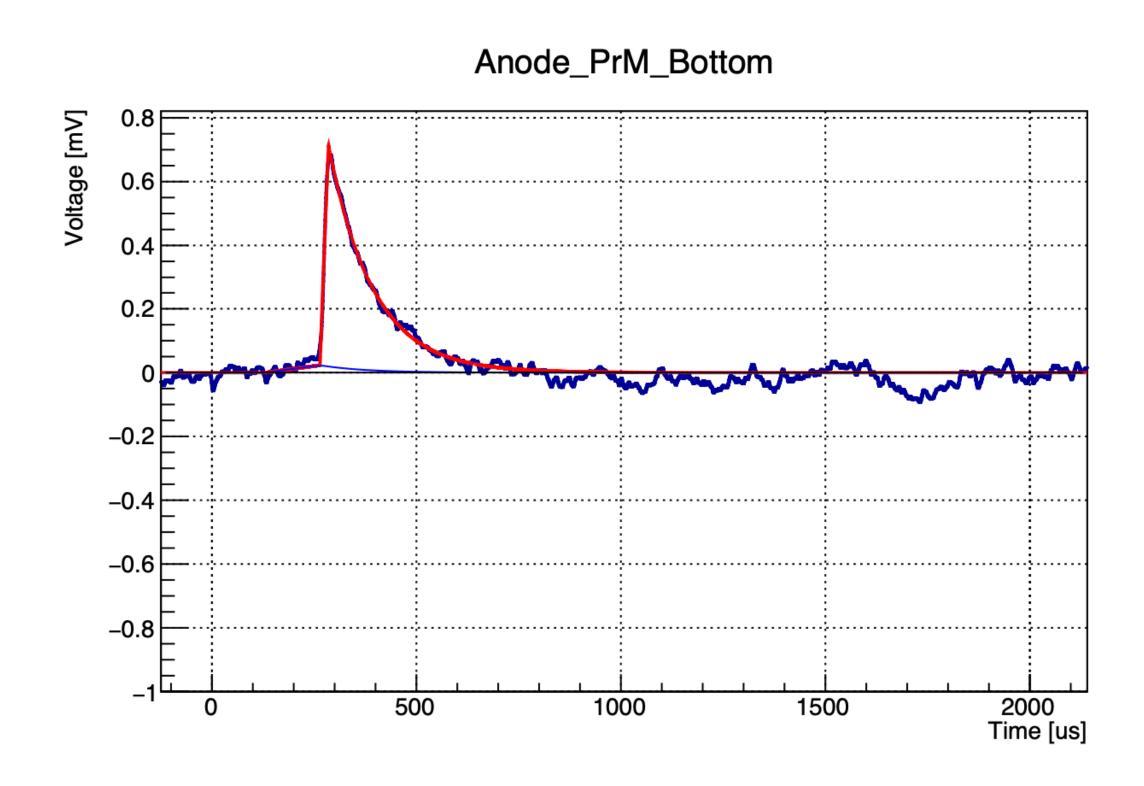

# LAr purity

- First PrM immersed on Friday

- Very good purity for raw LAr

- ~60 μs of electron lifetime, which corresponds to ~5 ppb O<sub>2</sub> equivalent.

## Next steps

- LAr filling will be completed in about 3 weeks (~ April 20th)

- Purification will take about 3 weeks

- Regular data taking from Mid May

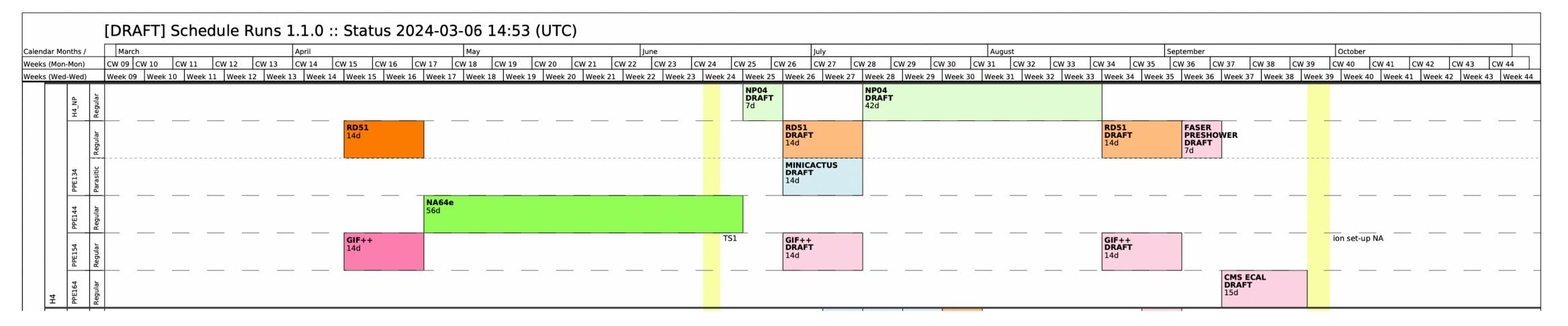

- This is the preliminary beam schedule. Probably some updates at today's overlapping NP04 coordination meeting

https://ps-sps-coordination.web.cern.ch/ps-sps-coordination/schedules/ps/2024/v1.1.0/schedule\_runs\_v110\_20240306\_all.pdf

## Preliminary run plan for PDS

Preliminary run plan available with description of the different configurations

https://docs.google.com/document/d/1elJR-hDbb46q2zSVWW0pGjzX4X-2Mx0B2IIFZySZX-M/edit?usp=sharing

|                            |         | February |         |  |  | Mar | ch      |    |   | Apı | ril |     |        | May | 1 |      |        | June  | е |   |

|----------------------------|---------|----------|---------|--|--|-----|---------|----|---|-----|-----|-----|--------|-----|---|------|--------|-------|---|---|

|                            |         |          | purging |  |  | COO | l filli | ng |   |     |     | pur | ificat | ion |   | regu | ular d | ation |   |   |

| Study                      | trigger |          |         |  |  |     |         |    |   |     |     |     |        |     |   |      |        |       |   |   |

| IV curves and Vbd          | none    |          |         |  |  | d   | d       | d  | d | d   | d   |     |        |     |   |      |        |       |   |   |

| Test data in GAr           | self    |          |         |  |  |     |         |    |   |     |     |     |        |     |   |      |        |       |   |   |

| DCR                        | TI      |          |         |  |  | d   | d       | d  | d | d   | d   |     |        |     |   |      |        |       |   |   |

| Light yield vs pur.        | self    |          |         |  |  |     |         |    |   |     |     | d   | d      | d   | d |      |        |       |   |   |

| Gain calibration           | TI      |          |         |  |  |     |         |    |   |     |     |     |        |     |   | W    | W      | W     | W | W |

| Self-trigger efficiency    | TI+self |          |         |  |  |     |         |    |   |     |     |     |        |     |   |      |        |       |   |   |

| Light yield map with laser | self    |          |         |  |  |     |         |    |   |     |     |     |        | ?   |   |      | ?      |       |   |   |

| Physics                    | self    |          |         |  |  |     |         |    |   |     |     |     |        |     |   |      |        |       |   |   |

6

d=daily, w=weekly, TI=Timing interface command

Anselmo Cervera Villanueva

## Forming a PDS team for NP04 data taking

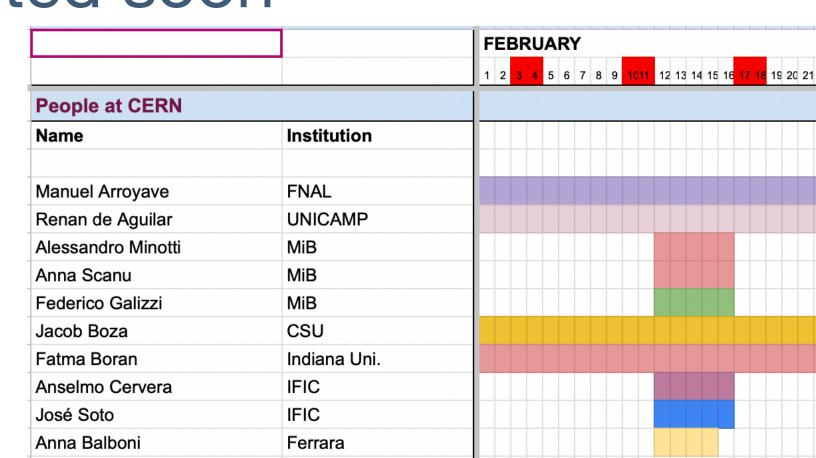

- We had back in February a expert training week with Manuel as coach.

- This group of people has been active, developing several tools and helping with data and documentation

- The group will be extended with the arrival of new people already next week

- The existing documentation will be improved in order to facilitate new expert's training

- A list of tasks is being prepared and will be distributed soon

- Office space in building 892 has been requested

Access to all info, including documentation and tasks

https://docs.google.com/spreadsheets/d/ 14fpCjNZFnyq72wugfSGXdAcTrgFroA1Al2In7VeyZIY/edit#gid=0

#### Where are we with the PDS?

- Bias voltage studies ongoing (next slide)

- LED Calibration module: standalone operation tested, integration with DAPHNE ongoing (see below).

- Calibration trigger: command sent by Timing Interface to both DAPHNE and the LED calibration module. DAPHNE responding (C. Benitez), almost there with calibration module.

- Integration with DAQ: Full DAPHNE configuration through DAQ to be released next week. Now its partially manual. We are already able to read day files. See later slides

- Slow controls: only DAPHNE power through DCS. Bias voltages, currents and temperatures accessible through DAQ OPmods

- Online Monitoring: . Through DAQ DQM, example available.

- Self trigger data format and algorithms (see last slide)

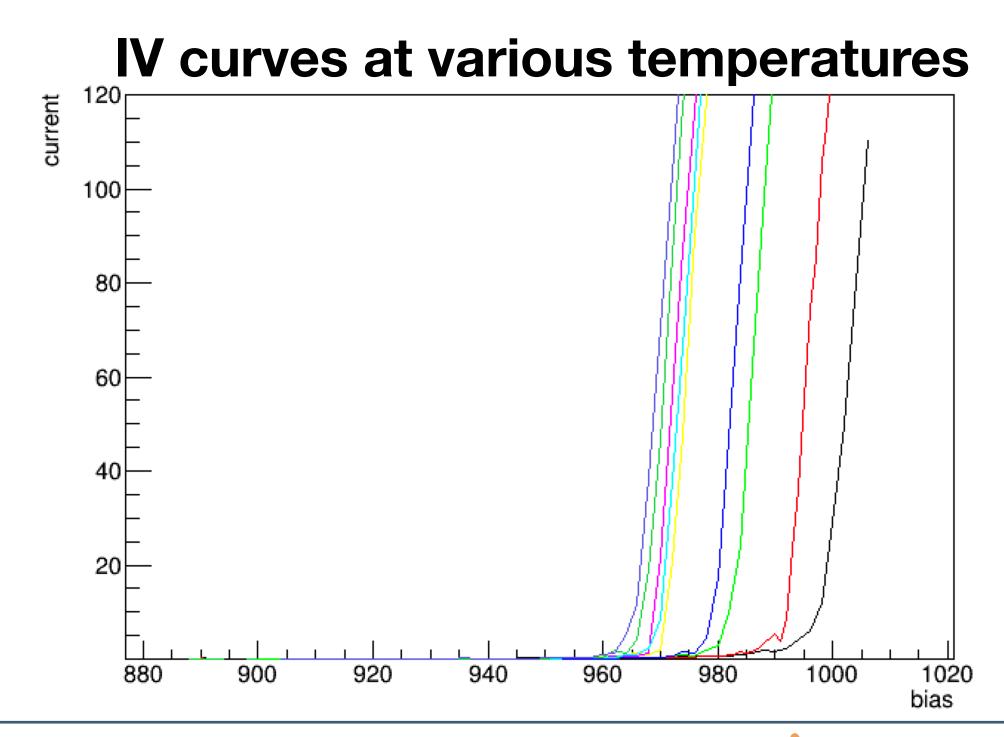

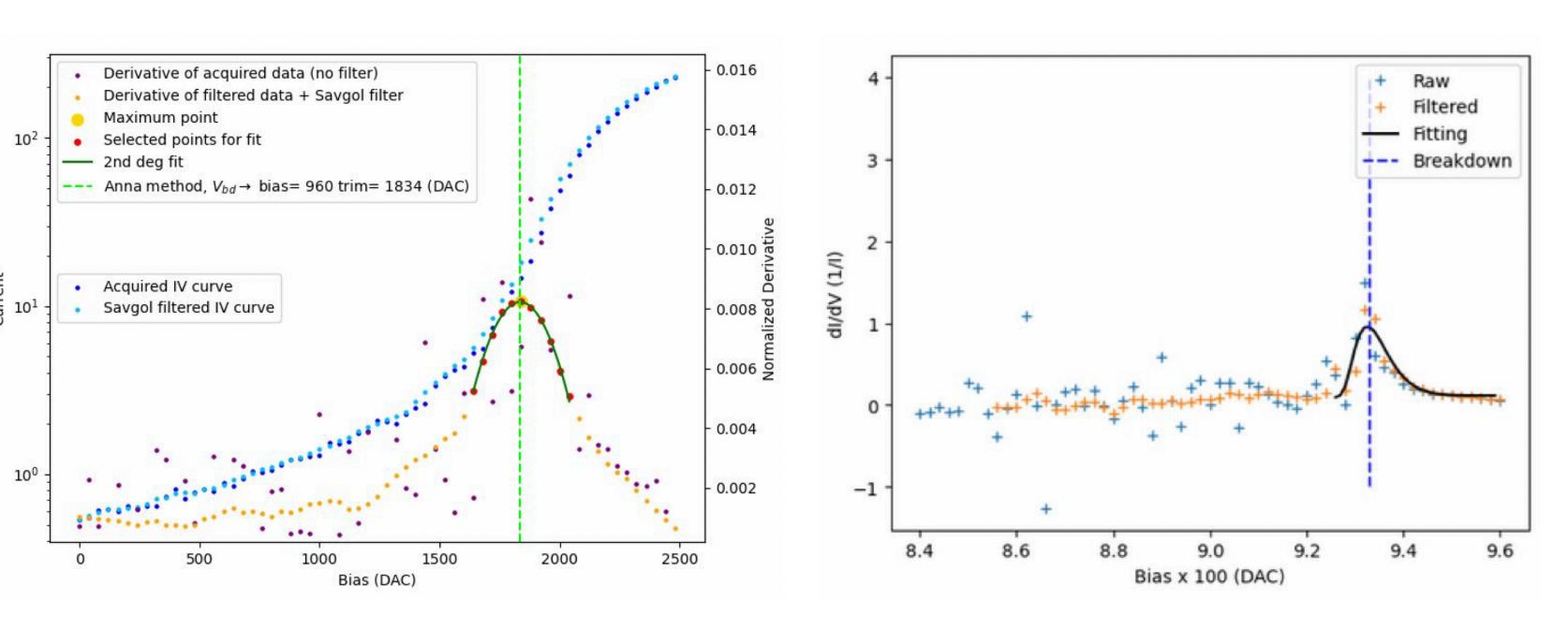

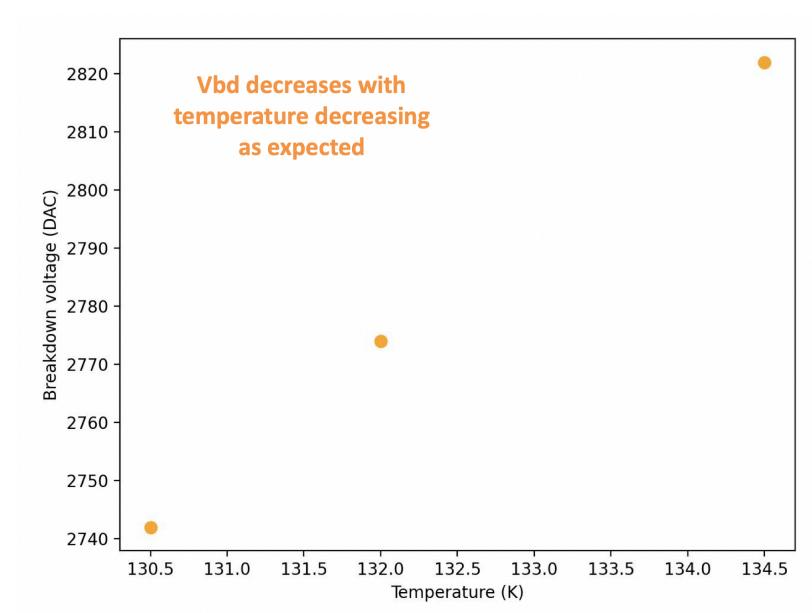

## IV curves and breakdown voltage

- All IV curves at room-T were recorded daily and breakdown voltage ( $V_{bd}$ ) computed. Data saved for posterior analysis refinement. Ongoing comparison with  $V_{bd}$  measured in the labs

- IV curves during cooldown and filling: code by Manuel and others.

- We took 2-3 measurements per day at the beginning and 1 measurement now

- Detailed analysis ongoing

$\bullet$  Ongoing detailed analysis by Renan and Anna with two different methods for estimation of  $V_{\text{bd}}$

10

Plan is to have an automatic script that creates a json file with the breakdown voltages

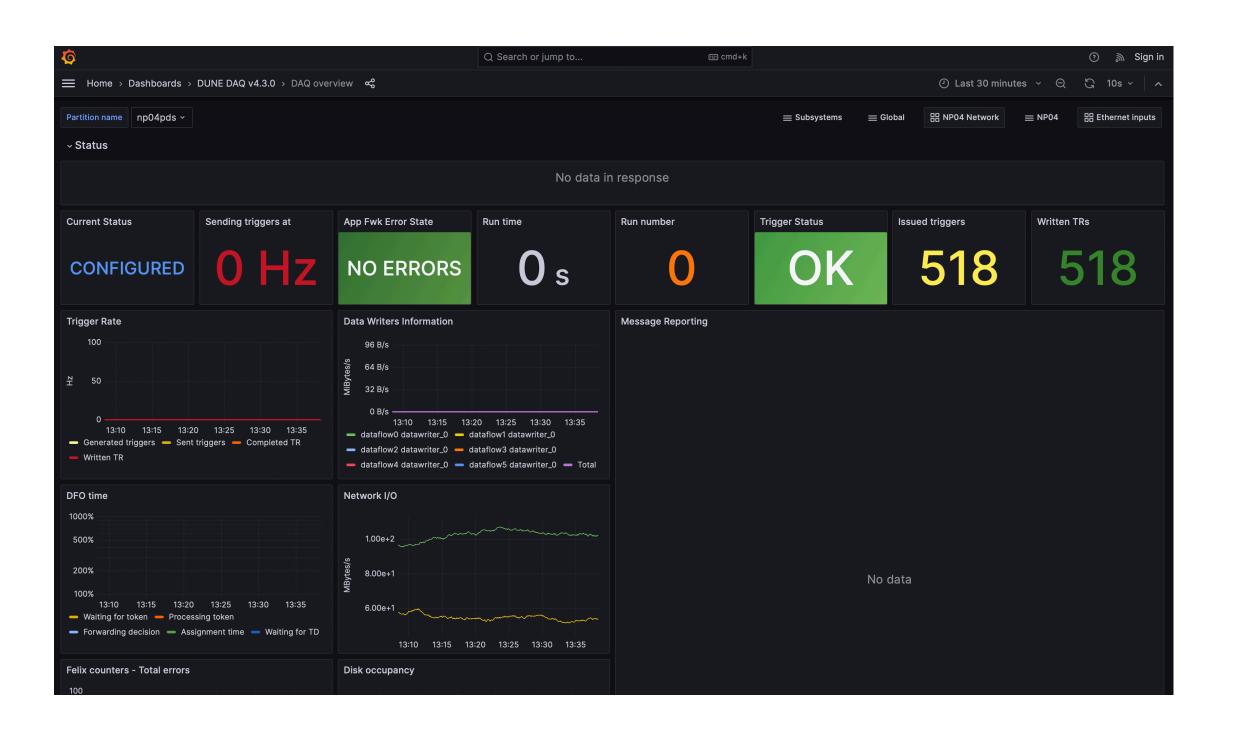

### Integration with DAQ

- We are currently able to take data with the DAQ

- Main DAPHNE parameters can already be configured through DAQ. The rest will be part of the DAQ release next week

Anselmo Cervera Villanueva

#### DAQ files

- Ongoing efforts (J. Soto et al.) to convert hdf5 files from DAQ into root files updating existing code from J. Calcutt, V. Popob y A. Oranday)

- So we are now able to take test runs and quickly look at the data

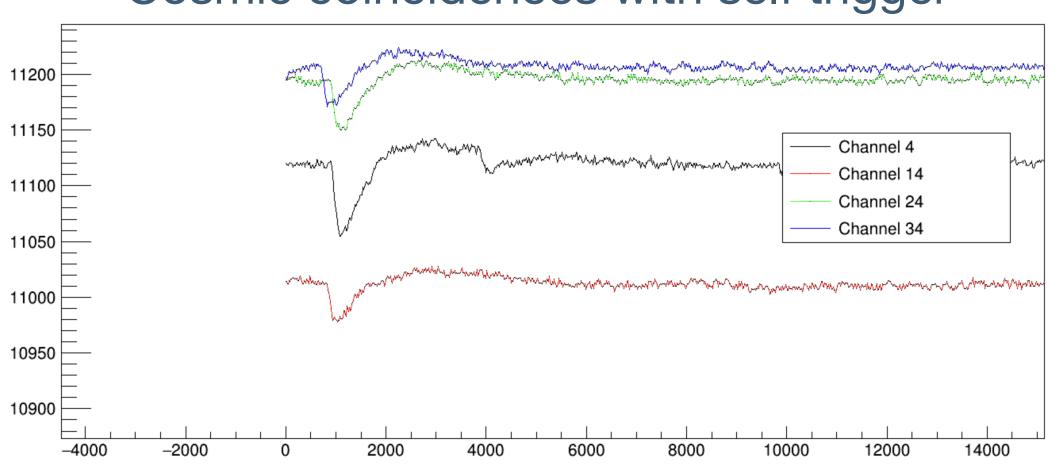

#### Cosmic coincidences with self trigger

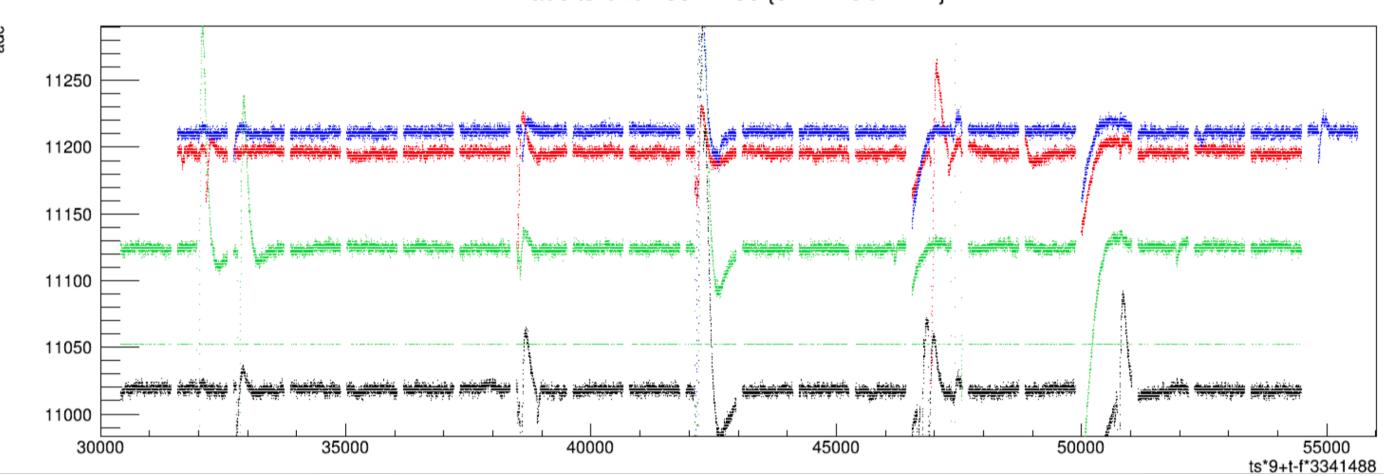

#### Timing command trigger at 5 kHz

adc:ts\*9+t-f\*3341488 {ch==2 && f==1}

## Interesting runs

We have started to fill a run list with interesting runs for tests

| A           | В                | С        | D        | E          | F          | G                                                                                                                        | Н                                             |

|-------------|------------------|----------|----------|------------|------------|--------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

| un number S | Start time       | End time | Shifter  | PDS expert | # triggers | Configuration                                                                                                            | Issues/Comments                               |

| 24496       | 2024-03-11 20:44 |          | marroyav |            |            | cosmics. All modules biased. (which endpoints were active?)                                                              | Signal only in 20 channels from slots 9,11,13 |

| 24606       |                  |          | acervera |            |            | test with TI command at 5000 Hz in ch 0-7 in endpoint 113. SiPM biased                                                   |                                               |

| 24606       |                  |          | acervera |            |            | test with TI command at 5000 Hz in ch 0,2,5,7 in endpoint 113. SiPM biased                                               |                                               |

| 24608       |                  |          | acervera |            | 416        | test with TI command at 500 Hz in ch 0,2,5,7 in endpoint 113. No bias. Constant offset at 11000                          |                                               |

| 24609       |                  |          | acervera |            | 211        | test with TI command at 5000 Hz in ch 0,2,5,7 in endpoint 113. No bias. Constant offset at 11000                         |                                               |

| 24610       |                  |          | acervera |            | 214        | test with TI command at 10000 Hz in ch 0,2,5,7 in endpoint 113. No bias. Constant offset at 11000                        |                                               |

| 24619       |                  |          | acervera |            | 62         | test with TI command at 5000 Hz in ch 0-7 in endpoint 113. No bias. With variable offset (1468+(ch-4)*30)                |                                               |

| 24620       |                  |          | acervera |            | 86         | test with TI command at 5000 Hz in ch 0-7 in endpoint 113. No bias. With variable offset, higher slope (1100+(ch-4)*150) |                                               |

#### Data format

- DAQ group is asking for the definitive self trigger frame format

- This is the current space allocation with 4 32-bits words for the header

- Ongoing discussion to increase it in order to accommodate up to five peaks

|     |      |                                                     |         |       | _         |        |         |        |         |          |                  |                  |       |                                   |                                   |               |           |          |                  |               |                  |                  |               |                |    |                  |  |   |   |       |          |          |

|-----|------|-----------------------------------------------------|---------|-------|-----------|--------|---------|--------|---------|----------|------------------|------------------|-------|-----------------------------------|-----------------------------------|---------------|-----------|----------|------------------|---------------|------------------|------------------|---------------|----------------|----|------------------|--|---|---|-------|----------|----------|

|     | K/D  | 31 30 29                                            | 28      | 27    | 26        | 25     | 24      | 23     | 22      | 21       | 20               | 19               | 18    | 17                                | 16                                | 15            | 14        | 13       | 12               | 11            | 10               | 9                | 8             | 7              | 6  | 5                |  | 4 | 3 | 2     | 1        | 0        |

| 0   | 0    | Link Slot                                           |         |       |           |        |         |        |         | CrateID  |                  |                  |       |                                   |                                   |               |           |          |                  |               |                  | De               | tID           | Version        |    |                  |  |   |   | rsion |          |          |

| 1   | 0000 | Timing master'                                      |         |       |           |        |         |        |         |          |                  |                  |       | er Time stamp [31:0]              |                                   |               |           |          |                  |               |                  |                  |               |                |    |                  |  |   |   |       |          |          |

| 2   | 0000 | 0 Timing master Time                                |         |       |           |        |         |        |         |          |                  |                  |       |                                   | me stamp [63:32]                  |               |           |          |                  |               |                  |                  |               |                |    |                  |  |   |   |       |          |          |

| 3   | 0000 | Time_Pulse_UB (10 bits, so 6 high order bits are 0) |         |       |           |        |         |        |         |          |                  |                  |       | Ti                                | ime_Pe                            | ak (8 b       | its, so 2 | 2 high o | rder b           | its are       | 0)               |                  |               | Channel        |    |                  |  |   |   |       |          |          |

| 4   | 0000 | Max_Peak                                            |         |       |           |        |         |        |         |          |                  |                  |       |                                   |                                   |               | Time      | _Pulse   | _0B (1           | 1 bits,       | so 5 hi          | gh or            | der bits      | are            | 0) |                  |  |   |   |       |          |          |

| 5   | 0000 | ADC([3:0],2) ADC([13:0],1)                          |         |       |           |        |         |        |         |          |                  |                  |       |                                   |                                   | ADC([13:0],0) |           |          |                  |               |                  |                  |               |                |    |                  |  |   |   |       |          |          |

| 6   | 0000 | ADC([7:0],4)                                        |         |       |           |        |         |        |         |          |                  |                  | ADC([ | DC([13:0],3)                      |                                   |               |           |          |                  |               |                  | ADC([13:4],2)    |               |                |    |                  |  |   |   |       |          |          |

| 7   | 0000 | ADC([11:0],6)                                       |         |       |           |        |         |        |         |          |                  |                  |       | ADC([13:0],5)                     |                                   |               |           |          |                  |               |                  |                  | ADC([13:8],4) |                |    |                  |  |   |   |       |          |          |

| 8   | 0000 | ADC([1:0],9) ADC([13:0],8)                          |         |       |           |        |         |        |         |          |                  |                  |       | ADC([13:0],7) AD                  |                                   |               |           |          |                  |               |                  |                  | ADC([13:      | 12],6)         |    |                  |  |   |   |       |          |          |

| 9   | 0000 | ADC([                                               | 5:0],11 | )     |           |        |         |        |         |          | A                | DC([13:0],10)    |       |                                   |                                   |               |           |          |                  | ADC([13:2],9) |                  |                  |               |                |    |                  |  |   |   |       |          |          |

| 10  | 0000 |                                                     |         | ADC(  | [9:0],13] | )      |         |        |         |          |                  |                  |       | ADC([13:0],12)                    |                                   |               |           |          |                  |               |                  |                  |               | ADC([13:6],11) |    |                  |  |   |   |       |          |          |

| 11  | 0000 |                                                     |         |       |           | ADC([1 | 3:0],15 | )      |         |          |                  | ADC([13:0]       |       |                                   |                                   |               |           |          |                  | 3:0],14       | )                |                  |               |                |    | ADC([13:10],13)  |  |   |   |       |          |          |

|     | 0000 |                                                     | -       | -     | -         | -      | -       | -      | -       | -        |                  |                  |       |                                   |                                   | -             |           |          |                  |               |                  |                  | -             | -              | -  | -                |  |   |   |       |          | -        |

| 446 | 0000 | ADC([3:0],101                                       | 10)     |       |           |        |         |        | AI      | OC([13:0 | ],100            | 9)               |       |                                   |                                   |               |           |          |                  |               | ADC([13:0],1008) |                  |               |                |    |                  |  |   |   |       |          |          |

| 447 | 0000 | ADC([7:0],1012)                                     |         |       |           |        |         |        |         |          | ADC([13:0],1011) |                  |       |                                   |                                   |               |           | A        |                  |               |                  |                  |               |                |    | ADC([13:4],1010) |  |   |   |       |          |          |

| 448 | 0000 | ADC([11:0],1014)                                    |         |       |           |        |         |        |         |          |                  | ADC([13:0],1013) |       |                                   |                                   |               |           |          |                  |               |                  | ADC([13:8],1012) |               |                |    |                  |  |   |   |       |          |          |

| 449 | 0000 | ADC([1:0],1017)                                     |         |       |           |        | Α[      | DC([13 | :0],101 | 6)       |                  |                  |       |                                   |                                   |               |           |          |                  |               | AD               | OC([13           | :0],10        | 15)            |    |                  |  |   |   | Al    | DC([13:1 | 2],1014] |

| 450 | 0000 | ADC([5                                              | :0],101 | 9)    |           |        |         |        |         |          | ADC([13:0],1018) |                  |       |                                   |                                   |               |           |          | ADC([13:2],1017) |               |                  |                  |               |                |    |                  |  |   |   |       |          |          |

| 451 | 0000 |                                                     | A       | DC([9 | 0:0],102  | 1)     |         |        |         |          |                  |                  |       |                                   | ADC([13:0],1020) ADC([13:6],1019) |               |           |          |                  |               |                  |                  |               |                |    |                  |  |   |   |       |          |          |

| 452 | 0000 |                                                     |         |       | AI        | DC([13 | :0],102 | 23)    |         |          |                  |                  |       | ADC([13:0],1022) ADC([13:10],1021 |                                   |               |           |          |                  |               |                  |                  |               |                | 1) |                  |  |   |   |       |          |          |

| 453 | 0    | TBD                                                 |         | Νι    | umber_l   | Peaks  | 0B      | Nur    | nber_F  | eaks_l   | JB               |                  |       |                                   |                                   |               |           |          |                  |               | Charge           | e[19:0           |               |                |    |                  |  |   |   |       |          |          |

## Next steps

- With the tools for reading hdf5 files we can now start testing channel mapping and DCR

- We plan to integrate the LED calibration system in time for preliminary LED calibrations in three weeks (once detector is filled)

- Self trigger testing will come later (in about 5 weeks), but need to be prepared in advance

- C. Touramanis has been appointed run coordinator. Information about shifts will be available soon