### **AFC v4 Interim Production Readiness Review Status**

Stoyan Trilov AFC Interim Production Readiness Review 19/04/2024

### **Contents**

- AFC v4 validation

- Validation setup: hardware, firmware, and software

- Functionality tested

- Clock propagation

- Downstream data path

- Upstream data path

- Procurement and production plan

- Acceptance testing plan

- Handling, shipping, and storage

- Electrical safety

- Summary

# AFC v4 validation experimental setup

- The validation of the AFC v4 is documented in <u>EDMS 3071234 v.1</u>

- Two AFC v4s purchased from Creotech, and modified at Bristol were installed in a DTS vertical slice

- Each AFC is paired with a FIB (v1) prototype

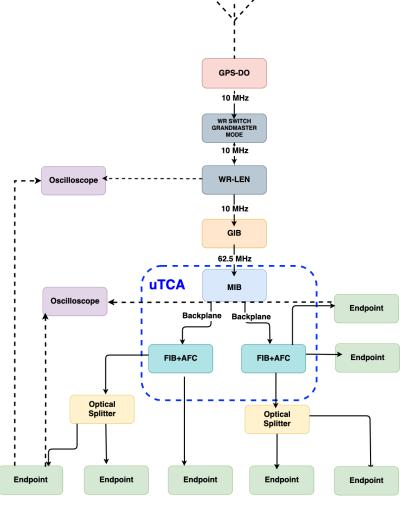

- 62.5 MHz DUNE clock generated by a GIB prototype locked to a 10 MHz clock provided by a GPS-DO

- Clock propagated through MIB, uTCA backplane, and the FIB+AFC pairs down to seven endpoints

- Endpoints constitute of DTS reference hardware FMCs mounted on FPGA baseboard

- MIB generates the DTS data(+clock) encoding the timestamp and synchronous commands received by the test endpoints

A diagram show the DTS full chain test topology

# AFC v4 functionality tested

### **Clock propagation**

Can the AFC receive the 62.5 MHz DUNF clock from the uTCA backplane, and propagate it to the FIB over one of its FMC connector and clock crossbar IC

#### **Downstream data path**

Can the AFC receive DTS data from the backplane, and propagate it, via the on-board FPGA, to the FIB SFPs

#### **Upstream data path**

Can the AFC receive return data from the FIB SFPs, and propagate it, via the on-board FPGA, to the uTCA backplane

A diagram show the DTS full chain test topology

19/04/2024

## Clock propagation test results

### **Clock propagation**

- An SI5395 PLL in the FIB successfully locked to the MIB clock as propagated by the AFC

- The PLL stayed locked over a period of 7 days

#### **Clock quality results**

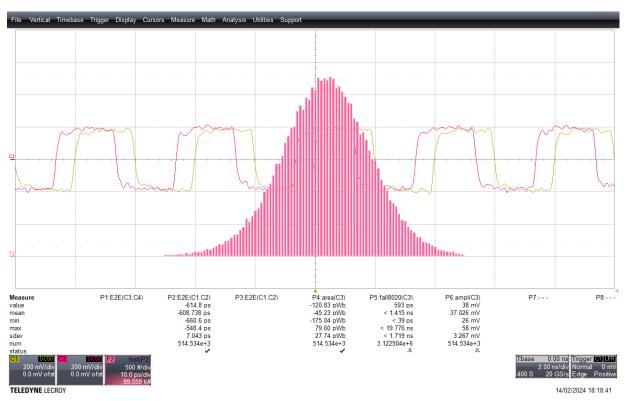

- Clock jitter was measured between two endpoints, and between an endpoint and the 10 MHz clock fed into the GIB

- In both cases the measured value was O(10 ps), several orders of magnitude lower than the DUNE requirement O(ns)

A screenshot showing a histogram of the difference in arrival time of the clock edges of two endpoints connected to different FIB+AFC pairs

### Downstream data path test results

#### **Endpoint data decoding test result**

All endpoints connected to the two FIB+AFC pairs were able to continuously decode the DCSK data for 7 days without errors

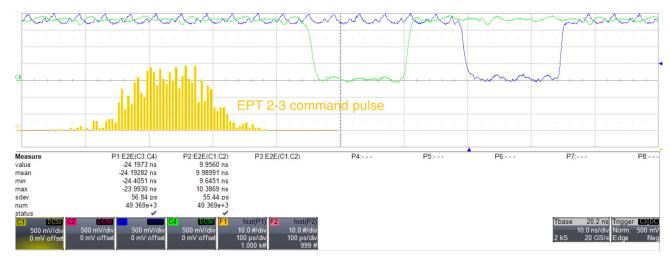

#### Synchronous command decoding

- Two endpoints were configured to produce an electrical pulse on the receipt of a synchronous command

- The MIB was configured to periodically send the command to downstream endpoints

- The pulses from the endpoints were found to arrive together (bar an offset), demonstrating the fixed latency of the synchronous command distribution via the FIB+AFC

A screenshot showing a histogram of the difference in arrival time of the edges of electrical pulses produced by two endpoints in response to the receipt of a synchronous command

### Upstream data path test results

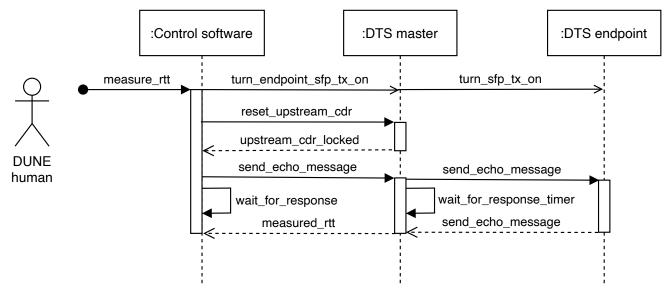

- Each DTS endpoint is able to communicate messages back to the master via its upstream data link

- The exchange of messages between master and endpoint is used measure the round trip time between the two devices

### MIB-endpoint round trip measurement

- For each endpoint connected to the two FIB+AFC pairs, the upstream data path was used to measure the round trip time between MIB-endpoint

- The round trip times were found to be stable over 7 days demonstrating the fixed latency of the synchronous message distribution from endpoint to MIB via the FIB+AFC

A sequence diagram showing exchanges of messages between master and endpoint during a round trip time measurement. The FIB+AFC forward messages between master and endpoint.

### Procurement and production plan

- Procurement and production plan is documented in <u>EDMS 3069484 v.1</u>

- The AFCs will be procured via the UKRI central purchasing system a tender process will take place to select supplier

- PCBs will produced, fully assembled, and tested by chosen manufacturer

- AFC is an open-hardware design meaning any manufacturer can choose to produce the boards

- Only one commercial supplier right now: Creotech, based in Europe

- Expected they will win tender due to already having advanced test capabilities for the AFC

- Procurement will proceed in three stages

- 1. Procurement of electronic components: purchase all component (barring generic resistor, capacitors, etc.) required to produce the AFCs mitigates risk of component becoming unavailable

- 2. Procurement of 5 pre-production AFCs: verify that the factory-modified AFCs have been produced correctly

- 3. Procurement of the full set of 36 production AFC includes 6 spares

19/04/2024

## **Acceptance testing**

- Each AFC arriving at Bristol laboratory will be subject to a QC compliance check

- Procedure documented in EDMS 3054874 v.5 approved by the DUNE QA manager

- Abridged QC steps:

- Visual inspection of board, and supplied documentation (manufacturer test results), assignment of UID

- Mounting of a FIB, and installation in an uTCA crate

- Power consumption check

- FPGA programming and flashing check

- Communication with FIB IC(s) check

- Check of SFP operational parameters (power consumption, optical power, etc.)

- Check of the full FIB+AFC DTS functionality for each SFP slot

- Clock propagation, downstream and upstream data path checks, phase measurement of endpoint clock

# Handling, shipping, and storage

- The QC compliance check described previously will be carried in an ESD controlled laboratory, with personnel using ESD protection

- Anti-static bench mats and straps, conductive floor mats

- After each FIB+AFC has passed the QC check, it will be placed in a static dissipative bag and packaged in boxes

- The boxes will be stored in a temperature controlled laboratory

- Prior to shipping to SURF, each board will packed in individual boxes with foam padding

- Shipment will include vibration monitoring, and GPS tracking

## **Electrical safety**

- The FIB+AFC have received a provisional electrical safety approval from the DUNE Compliance Office

- Documented in <u>EDMS 3057177 v.4</u>

- Full approval expected once the modified AFC v4 is available

- The electrical safety review included:

- Check of current carrying capacity and expectation of the FMC connectors, uTCA backplane power pins, DC-DC converters, power traces, planes, and vias

- Procedure of limiting the total available current to AFC from uTCA power supplies

- The AFCs are hosted in commercial uTCA infrastructure

- Crates, power supplies, crate controller modules

- uTCA infrastructure components are already approved for use at SURF EDMS 3064098 v.1

# **Summary**

- 3. Has the current design been validated sufficiently to give confidence that the components and assembled Printed Circuit Boards (PCBs) to be procured are the correct ones?

- The functionality of the AFC v4 validated at Bristol with a prototype of the modified board. It was found that the AFC is able to propagate clock and (duplex) data from the DTS master to test DTS endpoints. The performance of the AFC clock circuitry, as tested as a part of a full DTS chain, exceeds the requirements of the DTS.

- 4. Is there a credible plan in place for communicating the DUNE specific variations to the AFC design and ensuring that those changes have been correctly implemented?

- The DUNE specific modification have already been communicated to Creotech, and quotes for modified PCBs obtained. A small number of pre-production boards will be produced to verify that the modifications have been implemented correctly.

# **Summary (continued)**

# 5. Is there a credible plan in place for how the components will be procured, PCBs fabricated, and components assembled? Are the required quantities including spares well understood?

• The procurement and production process has been split into three stages, to reduce risk of component unavailability and production errors. The procurement process will follow the UKRI tendering process which is well exercised, and documented. The combination of 20% AFC spares, plus the 5 preproduction boards are expected to be enough to support permanent test and integration stands, as well as hardware replacements for DUNE.

# 6. Is there a credible plan for how the PCBs will be shipped, handled and stored before installation in the DTS system?

• The AFCs will be handled in an ESD controlled zones by trained personnel. They will be stored in environmentally controlled areas packaged in anti-static bags. Shipment to SURF will be monitored for excessive vibration.

# 7. Is an effective QC plan for acceptance testing in place in order to ensure the parts received meet specifications?

• An acceptance testing procedure is in place, and it has been approved by the DUNE QA manager.