# TriggerPrimitive Generation: Progress Update

Alejandro Oranday

June 12, 2024

# What's been happening?

- NP04 starts running.

- $\Rightarrow$  RS ADC data parameters redefined:

- ► ADC Integral, ADC Peak, and Peak Time.

- $\Rightarrow$  Configure RunningSum (RS) algorithms by plane.

- $\Rightarrow$  (**WIP**) TPHandler by plane.

- Documentation:

- ► Frame expansion.

- ► (*WIP*) TPG Algorithms.

- AVX2 vs Naive:

- ► Consistent!

- Consistent

$\Rightarrow$  Usable naive implementation in emulation & simulation.

## RS ADC Redefinition

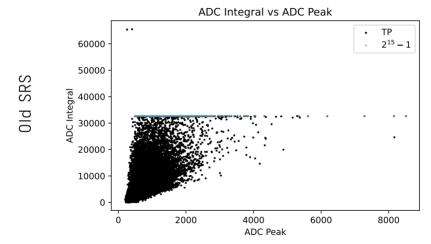

Previously struggled with negative values and centering to  $\Theta$  ADC.

# RS ADC Redefinition

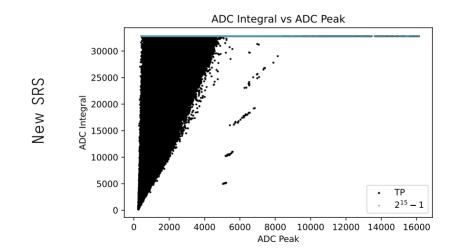

No longer struggles!

# Plane Refactoring

TPG by plane is a clear refactor point:

- Thresholding, RS configuring, and TPHandler identities are all by plane.

- Code duplication happened in a rush.

- $\blacksquare$  Prompts a new configuration schema (OKS).

### Documentation

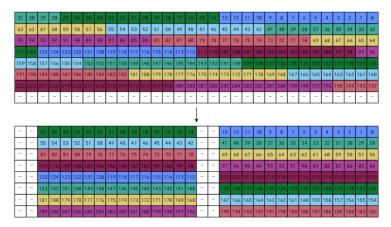

Diagrams of frame expansion: 14-bit to 16-bit.

### Documentation

Continue documentation for TPG algorithms.

- No complex register manipulation; less diagrams.

- Some AVX2 rule-bending; more math.

```

// Perform the division of __m256i with a const int

inline __m256i _mm256_div_epi16(const __m256i va, const int b)

{

__m256i vb = _mm256_set1_epi16(32768 / b);

return _mm256_mulhrs_epi16(va, vb);

}

```

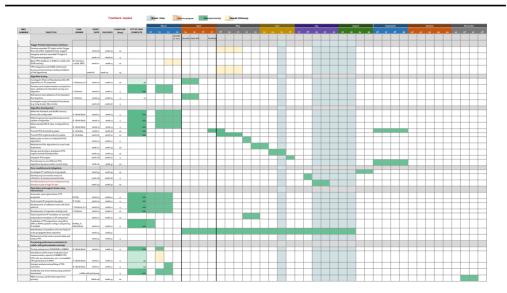

### TPG Gantt

# Points to Ponder

- RS:

- ► AbsRS is overflow prone.

- ► Add an overflow guard after division? For reference, (|sample| \* scale)/10.

- ► Apply the same guard to SRS?

- Does SRS become the standard instead of ST?

- uint16\_t  $\rightarrow$  uint32\_t?