# **DAPHNE Self-trigger integration**

D. Avila, E. Cristaldo, I. López de Rego August 15<sup>th</sup>, 2024

## Content

- Timing issues:

- How debug registers are read in the most updated commit in main.

- Pipelining: Solution to timing issue.

- Self-trigger integration:

- Module scheme.

- New timing issues and solution.

- Resources utilization.

- Self-trigger simulations:

- Signals.

- Trigger jitter.

- Conclusions.

# **Timing Issues**

| WNS(ns) | TNS (ns) | TNS Failing Endpoints | TNS Total Endpoints | WHS(ns) | THS (ns) |

|---------|----------|-----------------------|---------------------|---------|----------|

|         |          |                       |                     |         |          |

| -2.918  | -215.037 | 227                   | 50945               | 0.031   | 0.0      |

- The latest commit [97823e7] does not met timing constraints. This issue is caused by the introduction of debug registers in the st40\_top module, causing congestion due to the large amount of signals wire to the BIG mux in the ethernet data sender.

- Although the mentioned issue, the design was found to be stable during runs because the negative slack does not affect the core data senders and the integrity of data.

- When the self-trigger modules are included, the issue gets dramatically worse to the point where data integrity cannot be guaranteed.

- The issue was solved by pipelining and multiplexing the readout of these registers, but compatibility with the DAQ readout is lost. This solution was not merged yet and exist in a different branch.

## Module Scheme

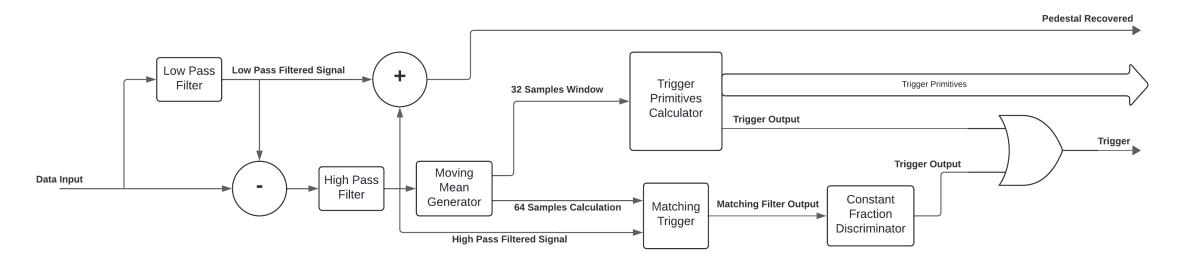

- The trigger aims to be a combination of all three strategies. Since the last results showed that the three modules have similar behaviours, we have decided to use ciemat's strategy in a parallel block to obtain the trigger primitives, avoiding problems with data synchronization since the trigger happens later using eia's matching trigger.

- However, we must keep in mind that by doing this, there is a possibility that sometimes triggers might

happen for the matching trigger and not for the ciemat's trigger, therefore creating packet frames with no

trigger primitives information, this must be addressed in following weeks.

4

## **New Timing Issues**

| Design Timin   |             |                       |                     |         |         |

|----------------|-------------|-----------------------|---------------------|---------|---------|

| WNS(ns)        | TNS(ns)     | TNS Failing Endpoints | TNS Total Endpoints | WHS(ns) | THS(ns) |

| 0.021          | 0.000       | 0                     | 267060              | 0.012   | 0.000   |

| All user speci | fied timing | constraints are met.  |                     |         |         |

- After the MUX and pipelining solution was placed, the merge of all three algorithms was done following this specific branch. However, new timing issues appeared.

- These timing problems were related to a register called packet\_size\_counter, located in the st40\_top module. This register was unnnecessary in later commits on the main branch since the usage of the almost\_full flag for the FIFOs was already guaranteeing the correct packet size, therefore it was commented and the timing issues were resolved.

## **Resources Utilization**

| +<br>  Site Type       | +<br>Used | +<br>  Fixed | Prohibited | ++<br>  Available   Util% |

|------------------------|-----------|--------------|------------|---------------------------|

| +                      | +         | +4           |            | ++                        |

| Slice LUTs             | 110884    | 0            | 800        | 133800   82.87            |

| LUT as Logic           | 94574     | 0            | 800        | 133800   70.68            |

| LUT as Memory          | 16310     | 0            | 0          | 46200 35.30               |

| LUT as Distributed RAM | 18        | 0            |            |                           |

| LUT as Shift Register  | 16292     | 0            |            |                           |

| Slice Registers        | 108550    | 0            | 0          | 269200   40.32            |

| Register as Flip Flop  | 108550    | 0            | 0          | 269200   40.32            |

| Register as Latch      | 0         | 0            | 0          | 269200 0.00               |

| F7 Muxes               | 5160      | 0            | 400        | 66900 7.71                |

| F8 Muxes               | 1166      | 0            | 200        | 33450 3.49                |

|                        |           |              |            |                           |

Warning! LUT value is adjusted to account for LUT combining.

| Site Type   Use    | d   Fixed | Prohibited | Available | Util% |

|--------------------|-----------|------------|-----------|-------|

| DSPs   520         |           | 0          | 740       | 70.27 |

| DSP48E1 only   520 |           |            |           |       |

- There was too much congestion in ٠ the initial design, this was produced by the matching trigger, that was previously optimized to not use DSPs.

- After reviewing the DSP usage by ٠ milano's filters, some DSPs were freed up in order to implement matching filter's strategy, and exchange its implementation, so most of EIA's strategy goes to the DSPs, while milano's filters use fabric.

- Congestion was reduced, and DSP ٠ usage is not as high, allowing room for more modules.

Main branch

#### Core module

Tcount: out array\_5x8x64\_type; Pcount: out array\_5x8x64\_type; Scount: out std\_logic\_vector(63 downto 0);

#### DAPHNE top module –BIG mux

(X"0000000000000" & "00" & inmux\_dout(5 downto 0)) when std\_match(r (X"000000" & st\_enable\_reg) when std\_match(rx\_addr\_reg, ST\_ENABLE\_AD Tcount(0)(0) when std\_match(rx\_addr\_reg, TRIG0\_COUNT\_ADDR) else Tcount(0)(1) when std\_match(rx\_addr\_reg, TRIG1\_COUNT\_ADDR) else Tcount(0)(2) when std\_match(rx\_addr\_reg, TRIG2\_COUNT\_ADDR) else Tcount(0)(3) when std\_match(rx\_addr\_reg, TRIG3\_COUNT\_ADDR) else Tcount(0)(4) when std\_match(rx\_addr\_reg, TRIG4\_COUNT\_ADDR) else Tcount(0)(5) when std\_match(rx\_addr\_reg, TRIG5\_COUNT\_ADDR) else Tcount(0)(6) when std\_match(rx\_addr\_reg, TRIG5\_COUNT\_ADDR) else Tcount(0)(6) when std\_match(rx\_addr\_reg, TRIG6\_COUNT\_ADDR) else Tcount(0)(7) when std\_match(rx\_addr\_reg, TRIG7\_COUNT\_ADDR) else Tcount(1)(0) when std\_match(rx\_addr\_reg, TRIG8\_COUNT\_ADDR) else Tcount(1)(1) when std\_match(rx\_addr\_reg, TRIG9\_COUNT\_ADDR) else Tcount(1)(2) when std\_match(rx\_addr\_reg, TRIG10\_COUNT\_ADDR) else

## **Timing Issues**

#### Self-trigger branch

#### Core module

Rcount\_addr: in std\_logic\_vector(6 downto 0); Rcount: out std\_logic\_vector(63 downto 0);

#### DAPHNE top module --BIG mux

(X 00000 & 00 & Chreshold\_XC\_reg(41 downto 0)) when std\_match(rx\_addr\_reg, THRESHOLD\_XC\_BASEADDR) else (X"000000000 & st\_config\_reg) when std\_match(rx\_addr\_reg, ST\_CONFIG\_ADDR) else (X"00000000000000 & adhoc\_reg(7 downto 0)) when std\_match(rx\_addr\_reg, ST\_ADHOC\_BASEADDR) else (X"00000000000000 & outmode\_reg(7 downto 0)) when std\_match(rx\_addr\_reg, DAQ\_OUTMODE\_BASEADDR) else (X"00000000000000 & "00" & inmux\_dout(5 downto 0)) when std\_match(rx\_addr\_reg, CORE\_INMUX\_ADDR) else (X"0000000 & st\_enable\_reg) when std\_match(rx\_addr\_reg, ST\_ENABLE\_ADDR) else (X"000000" & st\_enable\_reg) when std\_match(rx\_addr\_reg, ST\_ENABLE\_ADDR) else Rcount reg when std\_match(rx addr\_reg, RCOUNT ADDR) else

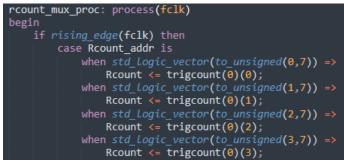

#### St40\_top – synchronous mux to read debug registers

- A synchronous mux was inserted in st40\_top module. In this way, we reduced the amount of output signals in the core module. Only

one signal is used to read the registers at the BIG mux.

- One way to restore compatibility with the DAQ is to include a simple state machine at DAPHNE2 top module that populates registers every 80 clock cycles (there are in total 80 registers). In this way, we can maintain the original read scheme.

7

# Simulations

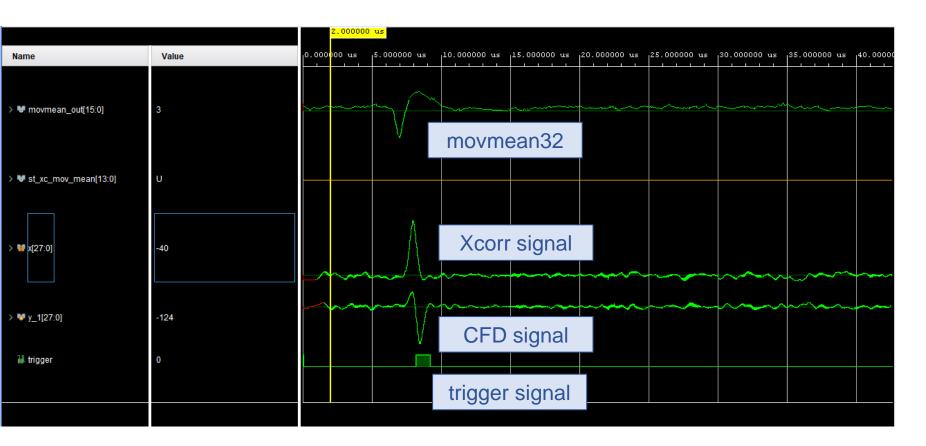

- Simulations using FBK waveforms and RAW noise data at VGAIN 0,89V (corresponding to a Dynamic range of around 2000 P.E.) was done to confirm signals are as expected.

- Minor offset and undershoot corrections were introduced and the CFD signal was verified to perform as expected to generate the trigger signal.

- Jitter performance was improved. See following slides.

## Simulations

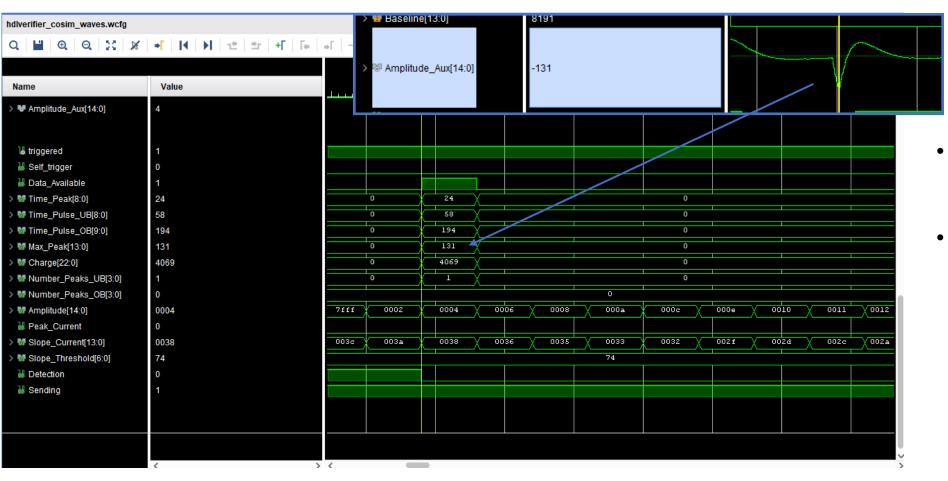

- Trigger primitives calculation was verified using the simulation.

- The waves file produced by the HDL simulation, shown at the left, verifies that for instance, the peak value is correctly calculated by the trigger primitives calculator.

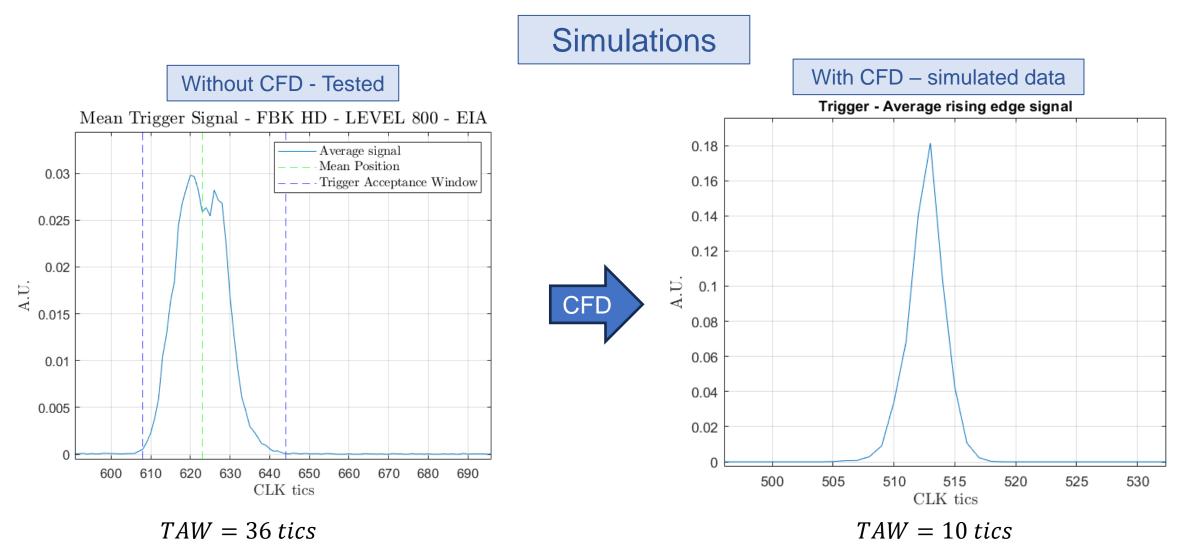

• The excess jitter issue observed during the self-trigger test at Milano-Bicocca in the EIA algorithm is mitigated by adding the CFD (constant fraction discriminator) stage.

TAW: Trigger Acceptance Window

## Conclusions

- The three different algorithms were succesfully integrated:

- Timing issues were resolved.

- Incompatibility with DAQ register readout will be adressed.

- Correct behaviour was verified using HDL simulations.

- The CFD module created by milano allowed eia's matching trigger to have an even better jitter behaviour than before.

- Using the OR gate to generate the final trigger output will need more study, since ciemat's jitter behaviour was degraded between the first test and the second test.

- Once the imcompatibility issue is adressed, the design will be ready to be deployed. (More on this

depends on experiment status, NP04 will not be available for testing, there is a small possibility of

testing in NP02, else, we will start the migration to DAPHNE V3)