## Interconnect activities at ORNL

#### Mathieu Benoit

**Physics Division**

ORNL IS MANAGED BY UT-BATTELLE LLC FOR THE US DEPARTMENT OF ENERGY

- Timepix4 TSV and Large Sensors development

- 3D-PDC and die-to-die eutectic bonding for 3D integration

- Anisotropic conductive glue for low-cost bonding

- Gold stud bumps for low-cost bonding

- Single die processing for bump deposition at ORNL

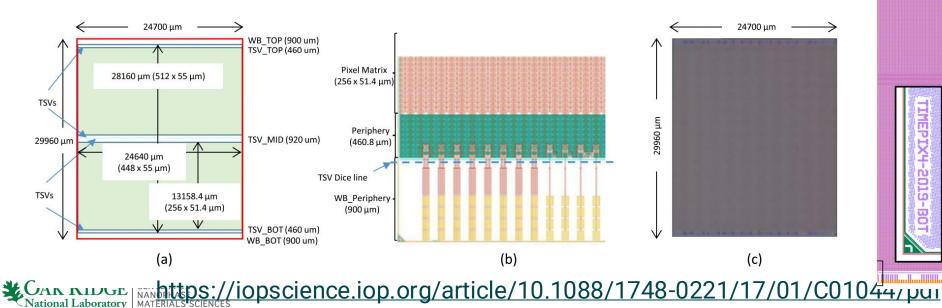

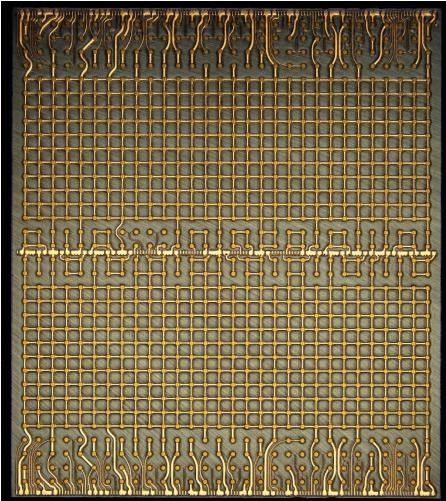

# **Timepix4 ASIC**

- 55 x 55 µm<sup>2</sup> pixels

- 448 x 512 pixel matrix, 24.7 x 30 mm

- ToT (16 bit counter,~1.5 keV) and ToA(<200 ps)

- ~3.6Mhz/mm<sup>2</sup>/s hit rate capability

- ~800e threshold

- 4 side buttable using TSV connections

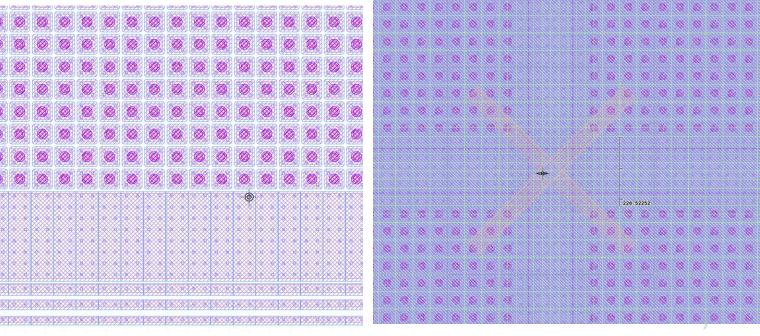

- Pixel Layout fits  $55x51 \ \mu m^2$ , Bump pad deported via top metal layer

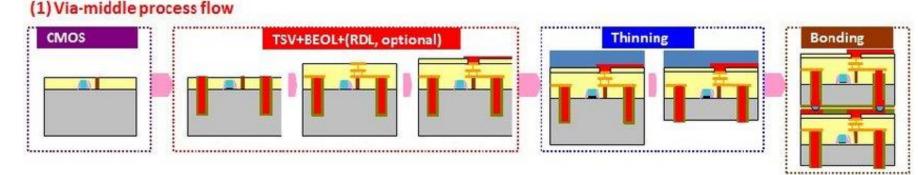

# **Through-Silicon-Vias processing**

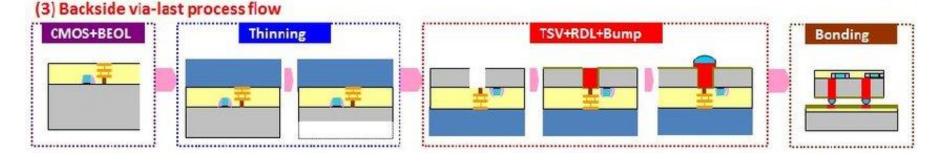

#### (2) Frontside via-last process flow

The Medipix/Timepix collaboration has a long history of R&D on via-last processing of large ASICs

- First trials with CEA-LETI with Medipix3 wafers with good results

- This drove the decision to make Timepix4 a TSV read ASIC

New Challenges brought by 65nm technology and beyond -> 12" wafers

• CEA, IZM not able to process 12", must rely on coring wafer

The collaboration is seeking partners to process full wafers

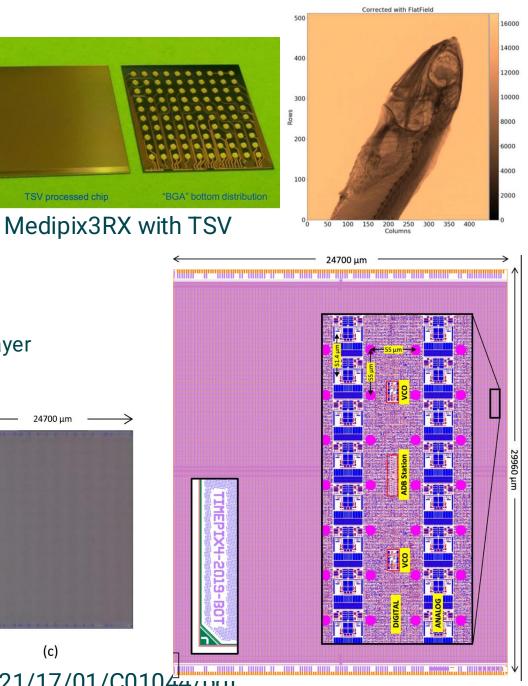

# **TSV Medipix3RX**

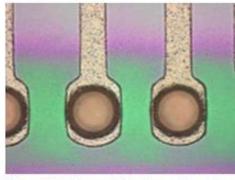

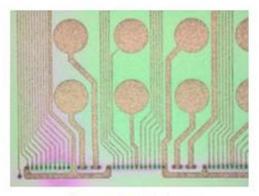

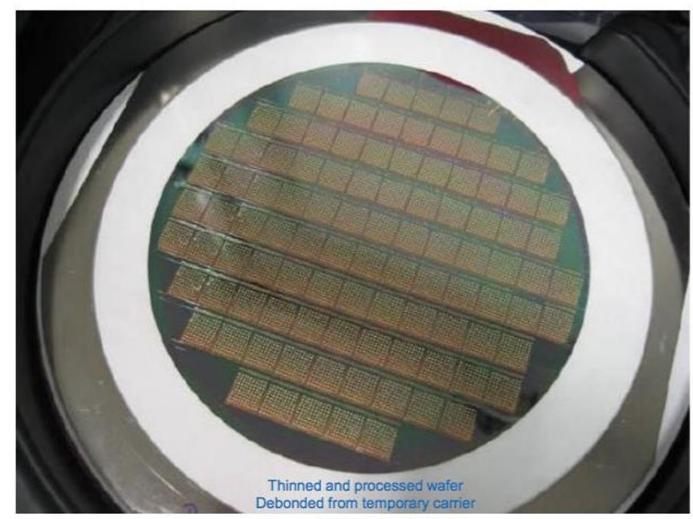

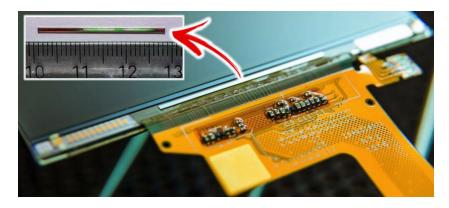

- Second run processed 6 wafers of Medipix3RX

- TSV yield ~ 70% to 80%

Through Silicon Vias diameter 60 µm Wafer thinned to 110-120 µm

Redistribution layer Back side of Medipix3 chip

Images courtesy of CEA LETI

19/4/16

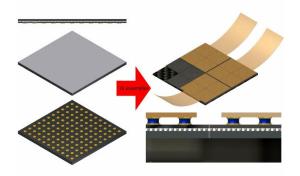

# A Timepix4 with TSV

ORNL is investing 75k in processing of 12" wafers with IZM Berlin, securing 2-3 wafers (~70 chips)

- TSV processing essential for large area tiling

- We plan on developing integration methodology using ACP/ACF or bumps that is ultimately wirebond less

**CAK RIDGE** National Laboratory

#### Pixel side

#### Back side

https://indico.cern.ch/event/1439336/contributions/6261676/atta chments/2978870/5244628/drd3\_extra\_results.pdf

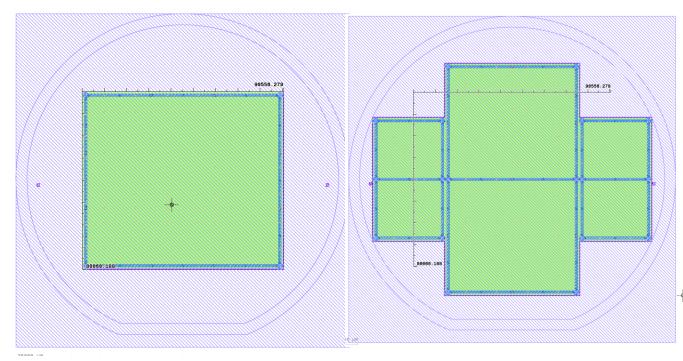

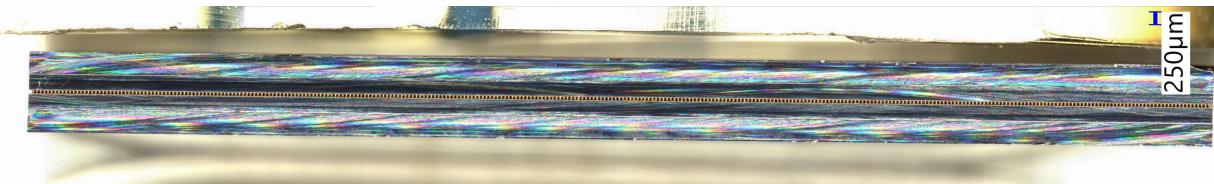

# **Sensor production**

- Timepix4 with TSV allows for the seamless tiling of ASIC on a large sensor, eliminating large gaps and keeping the ASIC in the acceptance

- we are working in partnership with Advafab, ORNL is financing the production of sensors exploiting the TSV

- Production of Thick (1 mm), and Thin(250 µm) bumped sensors with Thin Entrance Window

- Single ASIC for prototyping

CENTER FOR National Laboratory

- 2x2 or Quad sensors (5x5 cm<sup>2</sup>)

- 3x3 or Nonuplet sensor (7.5x7.5cm<sup>2</sup>)

- Flip-chipping of TSV ASICs to sensors. (10x singles, 6x quad, 9x nonuplets)

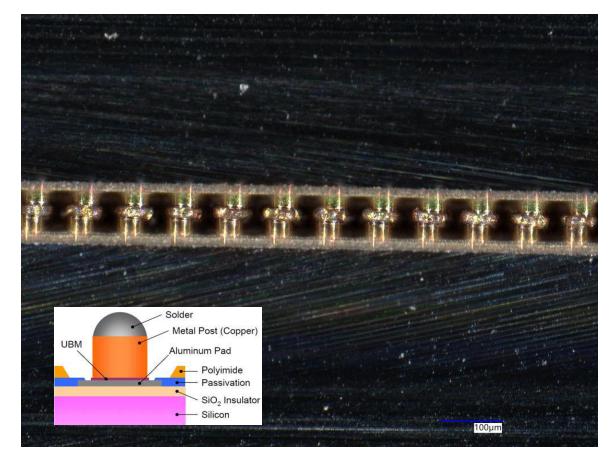

### **Copper Pillars trials**

- FC150 Flip-Chip bonder installed and commissioned at ORNL

- We repeated the trials with Medipix4 ASICs performed at the Flip-Chip vendor

- Medipix4 processed with Copper pillars by Winstech in Taiwan

- Promising low-cost process on 300mm wafers

- First trial have excellent yield <1um height uniformity</li>

- We bonded two Medipix4 together

- Not the intended use but 1-on-1 bonding facilitate things

- Focus on optimizing temperature and force parameters during bonding

- First optical inspection show excellent parallelism

- Small slip in alignment, observed on previous sample, need better heating during contact

https://indico.cern.ch/event/1439336/contributions/6261676/attachm ents/2978870/5244628/drd3\_extra\_results.pdf

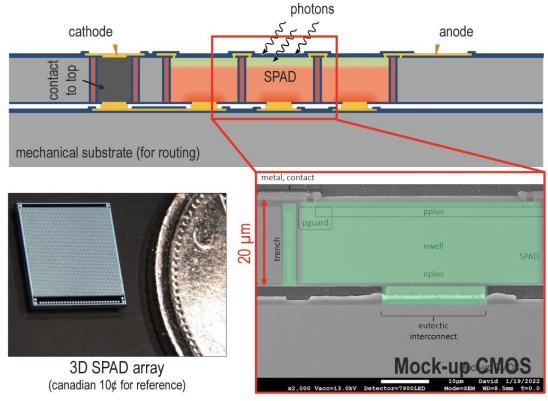

# **Other 3D Integration project at ORNL**

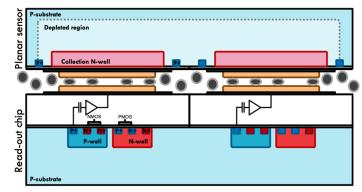

University of Sherbrook and ORNL are working together with Teledyne DALSA on the fabrication of 3D integrated Photon-Digital-Counter (PDC)

Project relies on TSV processing of the SPAD wafer and eutectic Al-Ge Wafer to Wafer bonding for interconnection to the ASIC

The Next generation of PDC hope to rely on the 65nm process with 300mm wafers

SPAD wafers on 6 inches

**CENTER FOR** National Laboratory

Need to core down wafer to do bonding

ORNL and UdS will investigate together the possibility of doing die to die bonding in ORNL FC150

- Flip-Chip bonder well within specs for this bonding

- Must verify effect of oxidation on bonds

- We may need to develop a etching process as well to pre-treat the dies before bonding

SEM cross section image

#### S. A. Charlebois<sup>1</sup>, S. Martel<sup>2</sup>, L. Fabris<sup>4</sup>, F. Retière<sup>3</sup>, J.-F. Pratte<sup>1</sup>

- 1. Université de Sherbrooke, Sherbrooke, QC J1K 2R1, Canada

- 2. Teledyne DALSA Semiconductor, Bromont, QC J2L 1S7, Canada

- 3. TRIUMF, Vancouver, BC V6T 2A3, Canada

- 4. Oak Ridge National Laboratory, Oak Ridge, TN 37771, USA

# Anisotropic conductive glues

ORNL IS MANAGED BY UT-BATTELLE LLC FOR THE US DEPARTMENT OF ENERGY

# **Anisotropic Conductive Films (ACF)**

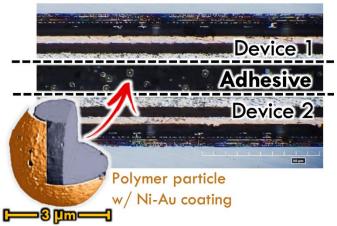

ACF is a technology developed for the LCD Display industry to connect drivers to each pixel row. Next step in the industry is  $\mu$ LED, which are driven individually and can measure as little as  $15x15\mu$ m<sup>2</sup>. Medipix and CLIC have been working with industry partners to adapt this process to pixel sensors

- Low cost, no lithography involved

- Wafer processing for pillar (ENIG) can be done in house with modest equipment

Bonding cross-section

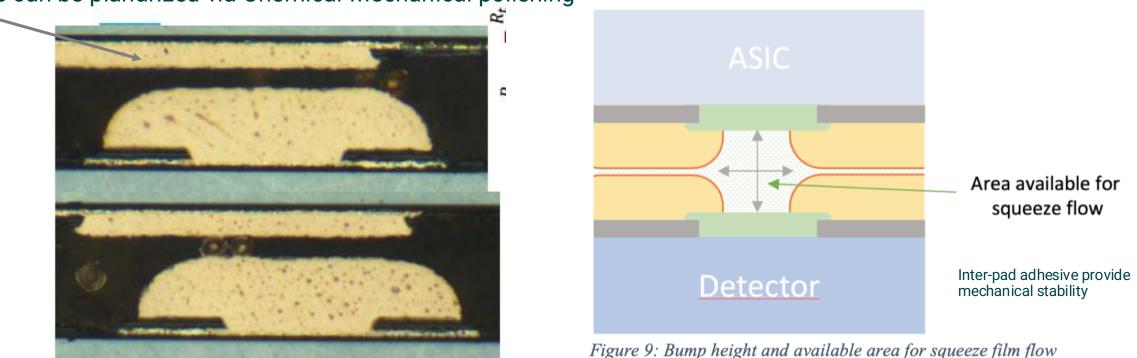

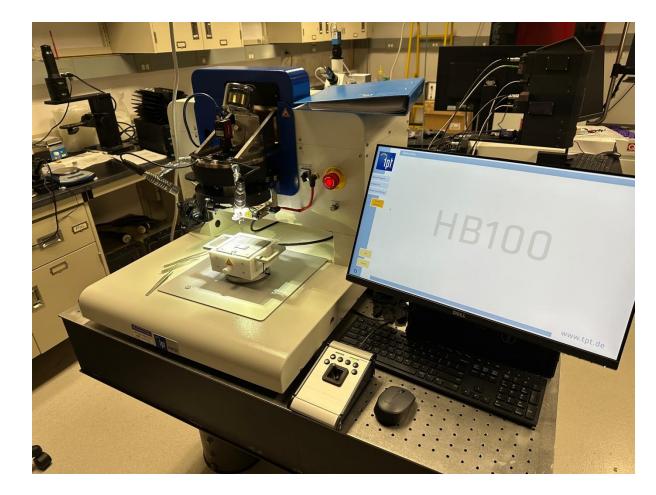

### **FC150 Flip-Chip bonder**

FC150 Automatic Flip-Chip Bonder

$\pm$  1  $\mu m$  post-bond accuracy and 20  $\mu radian$  leveling

Up to 150 mm substrate and chip bonding for chip-to-chip and chip-to-wafer bonding

Bonding force up to 2000 N and temperature up to 400  $^\circ C$

Active leveling using laser alignment and auto-collimation

Fully automated bonding process capable

High-precision fluid dispenser integrated for accurate fluid application during bonding

#### \$2M investment from ORNL on prober and flip-chip lab

### **ACF results**

#### <u>Ahmet Lale, DRD 3 Collaboration meeting,</u> <u>https://indico.cern.ch/event/1439336/contributions/6242532/</u>

Timepix3-ACF-sensor assembly cross-section

#### Pads can be planarized via Chemical-Mechanical polishing

# **ACP Fabrication at ORNL**

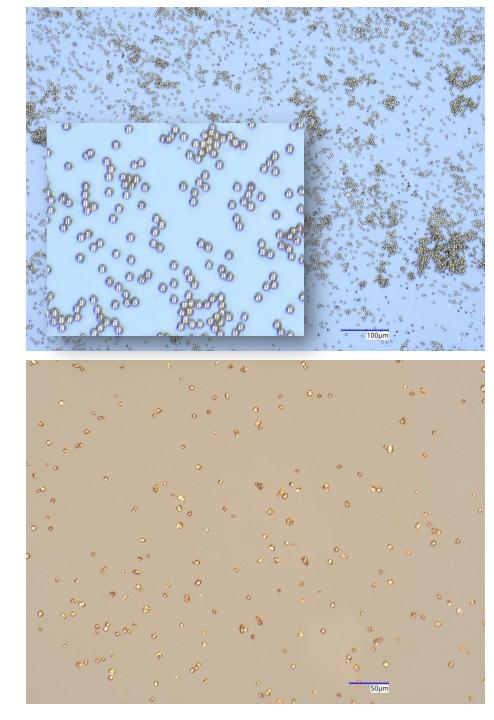

- We have started using ACP from various manufacturer to evaluate achievable pitch and reliability, handling, throughput etc.

- A much cheaper and efficient solution is to mix and fabricate our own ACP from particles from various vendors

- We can select the most appropriate matrix glue for our application, for example for radiation hardness

- Give access to more glues that have short lifetime for example

# **Gold stud bonding**

ORNL IS MANAGED BY UT-BATTELLE LLC FOR THE US DEPARTMENT OF ENERGY

# **Gold stud bonding**

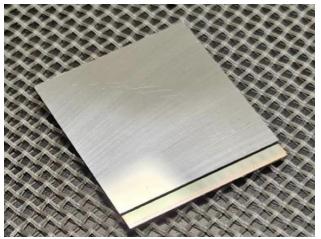

Gold stud bonding is a low-cost method for bonding dies with moderate pitch (> 100  $\mu$ m)

A gold pillar, which is essentially the first end of a gold ball bond, is deposited and cut short on the pad

This pillar can be further planarized by pressing against a surface, or used as is.

The bonding can be done in a flip-chip with heat and force, applying a non-conductive underfill glue to provide mechanical adhesion

Gold stud bumping at ORNL

Gold-stud hybridisation of ALTIROC3/A and LGAD sensors

- Using ALTIROC3/A ASICs and LGAD sensors from ATLAS High-Granularity Timing Detector (HGTD) to develop new in-house bonding process for sensor and ASIC qualification

- Single and stacked double gold studs used for the connections between the chips, epoxy underfill for bonding

- Used for radiation-hardness qualification of LGAD sensors

- Low temperature process (60°C) to avoid uncontrolled annealing

Gold studs are deposited one by one https://www.youtube.com/watch?v=ICRDBpmev4o&t=42s&ab\_channel=TP

T-Wirebonder

17

Stacked Gold studs

#### Gold stud

Preferred this solution to increase the gap between ASIC and sensor from 20 µm to 35 µm and thereby decrease coupling between them

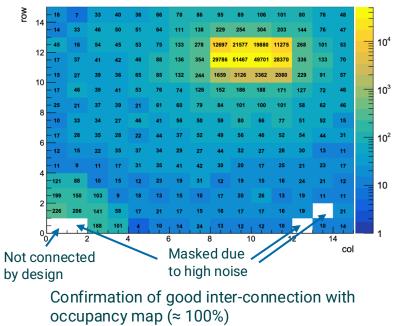

ALTIROC/LGAD Hybrid Flip-chip done with NCP (Araldite 2011)

Test-beam occupancy map of ALTIROC with double gold studs + irradiated LGAD sensor

- High connection yield, reproducibility, low temperature process

- Only for large pitch (>100μm), large pads (>80μm) chips

<u>Ahmet Lale, DRD 3 Collaboration meeting,</u> <u>https://indico.cern.ch/event/1439336/contributions/6242532/</u>17

### **Conclusion and perspective**

- ORNL is working on developing bonding techniques for our sensor and module assembly needs

- There is a big gap in the industry when it comes to prototyping and small volumes, where it is hard to find ways to progress and obtain integrated modules

- We need partners in developing the best glues, particles, bump deposition process

- We need to develop capabilities for die-to-die bonding to empower R&D and fill the gap in this industry and provide solution for many detector systems