# Testing and Programming the Integrator/ Digitizer Card for the Beam Loss Monitoring System

### Prakrit Shrestha Supervisor: Craig Drennan

The College of Wooster Wooster Ohio 44691

Fermi National Accelerator Laboratory Batavia Illinois 60510

SIST Program

August 5, 2013

### 1 The Beam Loss Monitoring System

- Integrator/ Digitizer Card

- Programming the Board

- 4 Testing the Module

- 5 Conclusion and Future Work

## Introduction

In a perfect system, installing a BLM system would be illogical and unnecessary, however since we do not possess such a machine, it is necessary to install this system.

# BLM @ Fermilab

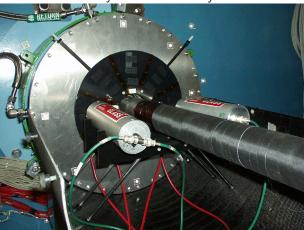

#### Ion Chamber

- · Nickel Electrodes

- $\cdot$  110cm<sup>3</sup> Argon gas

- $\cdot$  Calibration: 70nC/Rad

VME crate

- Control Card

Timing Card

- $\cdot$  Abort Card

- · High Voltage Card

- · Digitizer Card

4 / 26

### 1 The Beam Loss Monitoring System

### 2 Integrator / Digitizer Card

- 3 Programming the Board

- 4 Testing the Module

- 5 Conclusion and Future Work

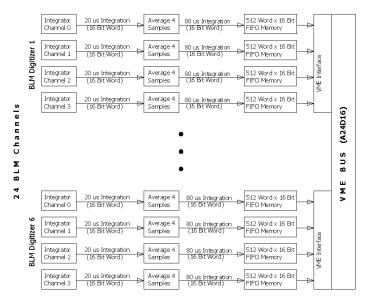

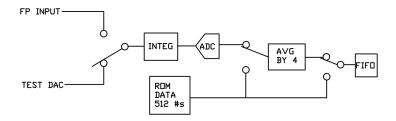

# 4 Channel Integrator/ Digitizer

## How does it work?

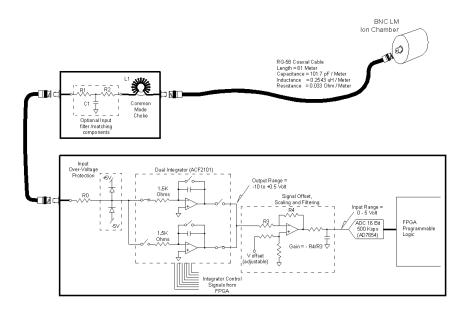

- Dual Integrator, integration for 20 μs,

- Analog to Digital Converter(ADC) produces a 16 bit word (1 bit≈15.26fC),

- Sum 4 sets of 20µs integration samples to get a 80µs sum,

- Divide the 80 µs sums by 4 to get 16 bit word,

- Data Acquisition for 40 ms produces 500 samples/cycle,

- 500 samples written to FIFO,

- Samples transferred over the VME bus for analysis.

## On Board Processing

- The Beam Loss Monitoring System

- Integrator / Digitizer Card

- Programming the Board

- 4 Testing the Module

- 5 Conclusion and Future Work

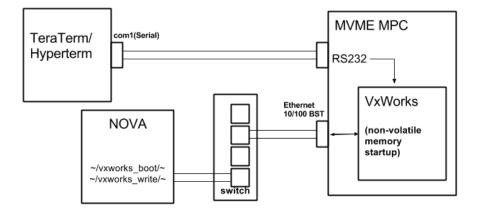

### FPGA (Field Programmable Gate Array)

Two FPGAs employed:

- Upper/ INTEG

- $\cdot$  manages sequencing and readout of integrator channels

- $\cdot$  performs scaling and averaging of readings

- Lower/ SUMS

- $\cdot$  DAC analog outputs

FPGAs manufactured by Altera.

Code written and manufactured using Quartus (\*.pof).

A \*.bst file created using ATMEL programming system.

FPGA configured from the EEPROM device at each power up.

# 4 Channel Integrator/ Digitizer

# Programming the FPGA

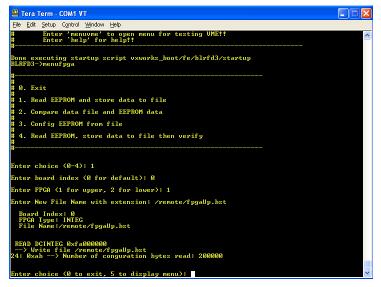

#### Menu Mode

# Programming the FPGA

#### **Command Line Mode**

| <u>File E</u> dit                      | <u>S</u> etup C <u>o</u> ntrol <u>W</u> indow <u>H</u> elp                                                                                                                                                                                                                                                                                                                                 |  |

|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| # That'<br>"                           | 's All Folks !!!                                                                                                                                                                                                                                                                                                                                                                           |  |

| #                                      | Enter `menufpga' to open menu for programming FPGA!!<br>Enter `cnd' to enter command line environment for programming FPGA!!<br>Enter 'menuvme' to open menu for testing UME!!<br>Enter `help' for help!!                                                                                                                                                                                  |  |

| Done e><br>BLRFD3-                     | xecuting startup script vxworks_boot/fe/blrfd3/startup<br>->cmd                                                                                                                                                                                                                                                                                                                            |  |

| # Confi<br># Read<br># Compa<br># Read | SYNTAX FOR COMMANDS<br>ig EEPROM from file:: urt <iboard> <type> (verify&gt; <fname><br/>EEPROM and store data to file:: prg <iboard> <type> <fname><br/>are data file and EEPROM data:: vfy <iboard> <type> <fname><br/>EEPROM, store data to file then verify:: prgvfy (iBoard&gt; <type> <fname></fname></type></fname></type></iboard></fname></type></iboard></fname></type></iboard> |  |

| # type=<br># fname<br># verif<br>#     | = 1 (DCINTEG, upper fpga) or 2 (DCSUMS, lower fpga)<br>= pointer to a filename string<br>fy= 0 (load without a verify) or 1 (load then verify)<br>(*for detail information: enter command help*)                                                                                                                                                                                           |  |

| #<br>>wet Ø                            | 1 1 upper130722.bst                                                                                                                                                                                                                                                                                                                                                                        |  |

| Board<br>FP(                           | i Index: 0<br>3A Type: INTEG<br>Uerify:VES<br>Le Name:/remote/upper130722.bst                                                                                                                                                                                                                                                                                                              |  |

| BURN I<br>VERIFI<br>≻exit<br>Have a    | ab 11010101<br>DCINTES Øxfa0000000<br>ESD> Number of conguration bytes written: 78310<br>nice day † :><br>= 21 = Øx15                                                                                                                                                                                                                                                                      |  |

- The Beam Loss Monitoring System

- Integrator/ Digitizer Card

- Programming the Board

- 4 Testing the Module

- 5 Conclusion and Future Work

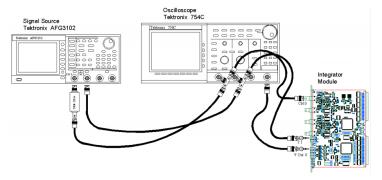

#### Test with External Pulse

### Test DAC (Digital to Analog Converter)

- Send analog signal from the Board

- Turn off all external input DIP switch and Registers employed to work with code

- Write certain values to registers at certain address to send commands example: write 0xff00 to register at address offset 0x01034 turns off FP input and turns on DAC input

- Data acquisition method is same

- Compare FIFO data to test DAC settings to evaluate Integrator and Digitizer

#### **ROM Test**

- Fixed values from ROM memory skips integration and digitization and stored to FIFO

- Data stored in FIFO is compared to expected data file computed from the known ROM values

## Testing the Digitizer Card

#### Screenshot of Test

| 📕 Tera Term - COM1 VT                                                                                                   |                          |                           |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------|--------------------------|---------------------------|--|--|--|

| Elle Edit Setup Control Window Help                                                                                     |                          |                           |  |  |  |

| Done executing startup script vxworks_boot/fe/blrfd3/startup BLRFD3->menuvme                                            |                          |                           |  |  |  |

|                                                                                                                         |                          |                           |  |  |  |

| === Setting up for Booster Operation ===                                                                                |                          |                           |  |  |  |

| All integrations have been sto<br>All FIFOs have been cleared.                                                          | opped.                   |                           |  |  |  |

| #<br># 0=Quit                                                                                                           |                          |                           |  |  |  |

| 1=Full ROM Test 2=Full test DAC                                                                                         |                          |                           |  |  |  |

| # 3=Set Test DAC 4=Run∕Stop Integ                                                                                       |                          |                           |  |  |  |

| # 0-Quit<br># 1=Pull ROM Test 2=Fu;<br># 3=Set Test DAC 4=Rur<br># 5=Read∧Write FIFO 6=Ex;<br># 5=Read∧Write FIFO 6=Ex; | pert Mode                |                           |  |  |  |

| Input Choice: 6                                                                                                         |                          |                           |  |  |  |

| 6. Expert Mode                                                                                                          |                          |                           |  |  |  |

|                                                                                                                         |                          |                           |  |  |  |

| === Low Level Menu ===                                                                                                  |                          |                           |  |  |  |

| <br>0=Quit                                                                                                              | 1=Full ROM Test          | 2=Display Register Status |  |  |  |

| # 3=Set Test DAC                                                                                                        | 4=Run Integ              | 5=Stop Integ              |  |  |  |

| 6=Clear FIFOs                                                                                                           | 7=Test FIFO              | 8=Read/Write FIF0         |  |  |  |

| a ∂-Quit<br>3-Set Test DAC<br>6-Clear FIFOs<br>9-Save Registers                                                         | 10=Restore Registers     | 11=Read Register          |  |  |  |

| # 12=Read & Modify Registers                                                                                            | 13=Move Memory to Buffer | 14=Move Buffer to Memory  |  |  |  |

| # 15=Test Data from ROM                                                                                                 |                          |                           |  |  |  |

| Input Choice:                                                                                                           |                          |                           |  |  |  |

#### Schematic for Data Acquisition

- The Beam Loss Monitoring System

- Integrator/ Digitizer Card

- 3 Programming the Board

- 4 Testing the Module

- built user interface to program the FPGA

- built routines to evaluate the veracity of the module

- build routines to test specific components of the board

- multi-board FPGA programming

- multi-board testing

- Craig C Drennan (Supervisor, Super Thanks)

- Elliott S McCrory

- Bradly T Verdant

- Dianne M Engram

- Linda M Diepholz

- Dr. Davenport

- ...entire SIST team

## References

- R. E. Shafer et al., Comments on the Tevatron BLM System, Fermilab BEAMS-DOC-790, July 2003.

- R. E. Shafer et al., *A Tutorial on Beam Loss Monitoring,* in proceedings of Beam Instrumentation Workship (NIW02), pp. 44-58, 6-9 May 2002, Upton, New York, USA.

- A. Baumbaugn et al., *Beam Loss Monitor Upgrades at Fermi National Accelerator Laboratory*, August 2011.

- C. Drennan, *Booster Beam Loss Monitor Data Acquisition and Presentation Specification*. Fermilab BEAM-DOCS-3723, December 2011.

- J. Lackey, C. Drennan *Booster Wire Scanner Integrator*. Fermilab BEAMS-DOC-3723, October 2009.

C. Drennan, Interfacing to the Booster BLM Upgrade Integrator/Digitizer VME Module. Fermilab BEAM-DOCS-3780, February 2011.

### Questions?